Verilog 多路选择器(MUX)

一般的遇到的情况都是单独的output 信号,对于inout信号,我们怎么做多路选择器呢?

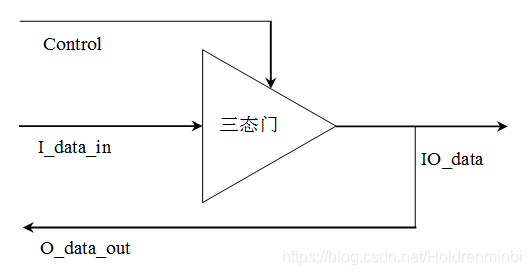

1、 inout、input、output的不同

2、inout电路

3、两路选择器

3.1 inout module

这是一个简单的inout使用模块

`timescale 1ns / 1ps

// Create Date: 2020/03/10 11:39:00

// Design Name:

// Module Name: mux_sub_function

//

module mux_sub_function (

input clk,

input reset_n,

input data_en_i,

output reg data_en_o,

inout [7:0] data_bus,

output[7:0] data_bus_in_o

);

parameter add1 = 1;

reg [7:0] data;

reg rev_r;

reg rev;

reg [2:0] count;

always@(posedge clk)

if(!reset_n)

begin

count <= 0;

data

这篇博客探讨了如何在Verilog中使用inout、input和output信号,特别是聚焦于构建两路inout多路选择器(MUX)。文章详细讲解了inout模块的设计,以及如何进行切换操作,并附带了MUX的testbench验证。

这篇博客探讨了如何在Verilog中使用inout、input和output信号,特别是聚焦于构建两路inout多路选择器(MUX)。文章详细讲解了inout模块的设计,以及如何进行切换操作,并附带了MUX的testbench验证。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

900

900

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?