随着人工智能(AI)快速发展,大模型正在掀起新一轮的信息革命浪潮,后摩尔时代算力面临发展瓶颈,算力成本居高不下,缺口持续扩大,亟需突破,国际半导体巨头们正在积极布局新一代基于Chiplet的AI算力芯片。AI Chiplet将成为AI 2.0时代算力芯片的核心,也是中国在人工智能时代突围的关键底层技术之一。

一、什么是Chiplet:

01

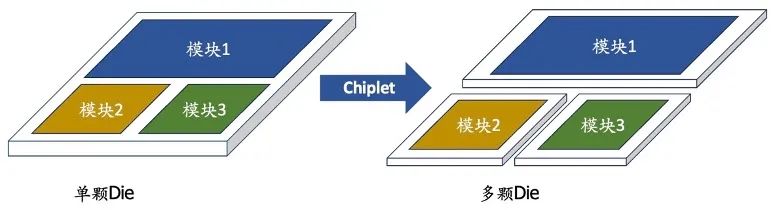

Chiplet是将一块功能丰富且面积较大的芯片裸片(Die)拆分成多个芯粒,通过将原来集成于同一单晶片中的各个元件分拆为独立的多个具有特定功能的芯粒,分开制造后再通过合适的封装技术将彼此互联,最终集成封装为一个系统芯片。

Chiplet技术示意图

信息来源:公开信息整理

02

Chiplet核心价值:

- 灵活性和定制化:Chiplet旨在将芯片性能与芯片工艺解耦,把传统的大型系统级芯片(SoC)分解为一系列更小、更灵活、更通用、且具有特定功能的芯片组;Chiplet能够提供产品定制化,允许通过混合封装不同的芯粒来满足不同的细分市场对于算力的需求。

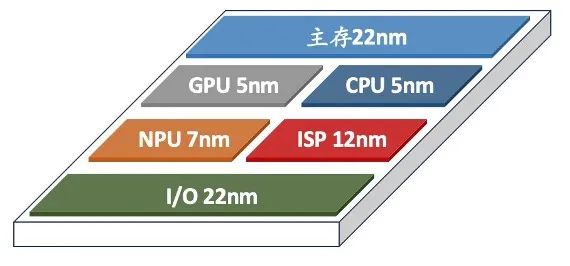

- 降低成本、提高良率:Chiplet技术通过使用成熟制程(低纳米)的情况下生产部分芯粒模块降低生产成本、提高良率,不同的芯粒可以根据需要来选择合适的工艺制程分开制造,不需要像SoC芯片全部都采用先进制程在一块晶圆上进行一体化制造,成熟的制程生产良率高、可显著降低芯片的制造成本。

Chiplet可采用不同制程工艺

信息来源:公开信息整理

- 性能优化:通过封装多颗芯粒异构集成一体来提升整体性能,对国内而言,虽然无法直接设计制造先进制程的芯片,但可以通过增加芯片的逻辑密度和功能、进行叠加封装,从而实现类似先进制程的性价比。

- 简化开发流程:通过对各功能模块分开设计、升级从而简化开发流程,对于单个芯片而言,如需升级芯片功能或采用最新技术,需重新开发整个芯片。如使用Chiplet的形式对芯片按照功能进行分割,则只需对具有相关功能的小芯片进行升级或使用最新技术对其进行开发即可,从而简化开发流程,提高工艺效率。

二、Chiplet应用场景/市场需求

随着人工智能、大数据分析、区块链等领域的发展,算力需求爆发,人们开始不断追求更高性价比的算力,Chiplet技术刚好迎合市场对于算力的性价比的需求。

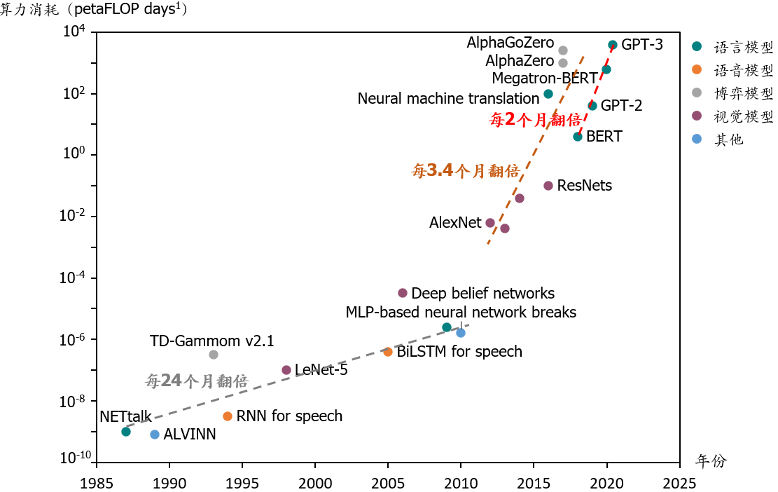

- 过去30年,人工智能(AI)模型的快速发展带来了对算力的指数级增长的需求。

不同AI模型对于算力的需求

信息来源:Brain-inspired computing needs a master plan

注释:petaFLOP days表示以1 petaFLOP/s 的效率运行一天消耗的算力,1 petaFLOP/s表示每秒钟进行10的15次方运算; 图中不同颜色的圆点代表不同年份推出的AI模型

- 提高芯片的算力本质上是大幅增加单颗芯片的晶体管数量;即在当前制程下增加单颗芯片面积或者在单位面积下使用更先进制程(更低纳米)的技术生产芯片;无论是哪种方法,都会因为良率的下降而导致成本大幅上升。

整体良率随SoC芯片面积增加而下降

信息来源:Chiplet Actuary: A Quantitative Cost Model and Multi-Chiplet Architecture Exploration

说明:上图横轴为SoC芯片面积,左轴为整体良率(从制造到最终测试通过),右轴为单位面积的原始晶圆成本;实线代表良率与SoC芯片面积的关系,虚线代表单位面积的原始晶圆成本与SoC芯片面积的关系

三、Chiplet技术应用瓶颈:平衡成本和运算性能

01

Chiplet技术的本质在于通过拼接高良率的小面积芯粒,达到媲美低良率的大面积、高算力芯片的效果,实现芯粒之间的高效数据传输是Chiplet芯片性能的核心瓶颈之一。

02

Chiplet行业面临着缺乏统一Die to Die(芯粒之间)数据传输互连的标准,互连技术是实现多个芯片之间高效通信的关键,缺乏统一的标准会导致互连方案不兼容、互操作性差等问题。

- Chiplet技术需要开发新型互连技术以便将小芯片连接在一起,Chiplet各裸片的互连接口和通信协议对于Chiplet技术十分关键,必须考虑到与制程和封装技术的兼容性,以及系统的集成和扩展需求,还需满足不同领域Chiplet集成对单位面积传输带宽、每比特功耗等性能指标的要求。

- Chiplet的大规模普及还依赖于标准化的芯片间互连协议。2022年3月,Intel、AMD、ARM、台积电、日月光等巨头成立 Chiplet 标准联盟,制定了通用 Chiplet 的高速互连标准 UCIe(Universal Chiplet Interconnect Express);2022年12月,由中国集成电路领域相关企业和专家共同主导制定的《小芯片接口总线技术要求》团体标准正式通过工信部中国电子工业标准化技术协会的审定并发布。目前行业内相关企业还未实现芯片间互连接口的统一化和标准化

03

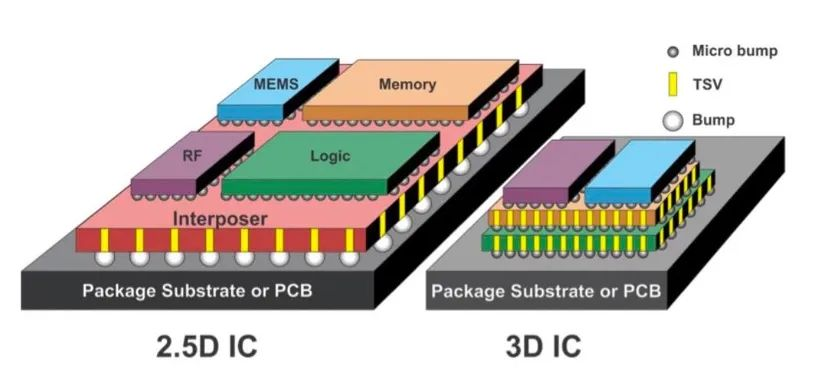

- Chiplet各裸片互连的物理实现依赖于芯片的封装,多芯片封装技术的性能、成本以及成熟度对于Chiplet芯片应用有着极大的影响。选择合适的封装技术能够有效地支持芯片之间的通信和数据传输,从而提高整体系统的性能和可靠性。

- 目前可用于Chiplet的封装技术主要包括基于基板(Substrate)的封装技术(MCM)、基于硅中介层(Interposers)的封装技术(2.5D/3D封装)以及基于重分布层的(Redistribution Layer,RDL)扇出封装技术(Fan-Out)。每种封装技术都有其独特的优势和劣势。2.5D/3D封装技术能够提供更高的性能和密度,但成本较高;而传统的封装技术成本较低,但性能可能会有所牺牲。因此合适的封装技术需要综合考虑产品需求、性能要求以及成本因素。

信息来源:Semiconductor Engineering,民生证券研究院

04

需要完整的EDA配套软件支持Chiplet芯片组的研发和仿真测试等环节。

- 对于Chiplet芯片来说,单个问题裸片会导致全芯片失效,代价很高,完善、全面的测试对于Chiplet芯片质量控制尤为重要。采用Chiplet技术集成的芯片组对热效应、电感耦合、电容耦合、电磁干扰、信号完整性等方面提出了全新的要求,需要针对各方面要求进行仿真建模,而这是原先用于SoC芯片的EDA工具相对薄弱的点。与单芯片集成相比,Chiplet将多个裸片封装在一起但管脚有限,可能仅能保证裸片部分管脚或部分裸片的测试连接需求,加剧了芯片测试的困难。因此,Chiplet需要成熟完善的配套EDA软件从架构探索、芯片设计、物理及封装实现等提供全面支持,以在各个流程提供智能化、优化的实施辅助,避免引入问题和错误。目前,国外针对Chiplet的EDA工具技术积累更丰富、产品更成熟,国内的EDA工具还在不断发展和完善中。

四、当前Chiplet芯片在一些方面存在限制,尤其是在制程成熟度和芯片面积方面。随着对标芯片制程的不断进步和面积的增大,Chiplet芯片的性价比优势会变得更加明显

01

成熟制程成熟工艺(制程大于14nm)节点不适合高密度Chiplet的原因为,这些节点的工艺相对成熟,良率较高,因此面积增大带来的芯片缺陷成本增加较小,不足以抵消更高级封装带来的成本增加。而小面积芯片(芯片面积小于200 mm2)也不适合高密度Chiplet,因为芯片缺陷成本较小,封装类的成本占据主要生产成本。

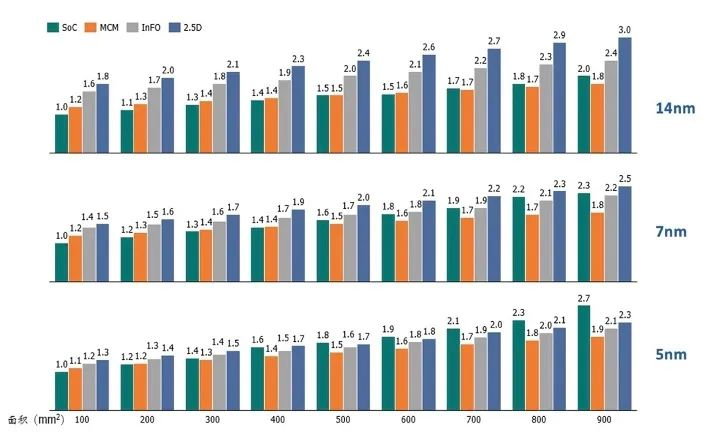

- 就 2 芯粒组成的14nm芯片而言,只有面积大于700mm2,SoC的成本才勉强大于MCM;而如果使用先进封装,即使到了900 mm2,SoC成本仍占据优势。

- 就 2芯粒组成的7nm芯片而言,当面积大于500 mm2,SoC的成本大于 MCM;当面积大于800 mm2,SoC的成本才大于InFO。

- 就2芯粒组成的5nm芯片而言,当面积大于300mm2,SoC的成本大于MCM;当面积大于500mm2,SoC的成本大于InFO;当面积大于700 mm2,SoC的成本才大于2.5D方案。

- 另外如果芯粒数量进一步增多,对成本的优化效果会进一步提升,比如5芯粒组成5nm芯片,只要面积大于200 mm2,使用Chiplet就会有制造成本优势。

不同工艺节点下2芯粒集成的制造成本比较

信息来源:Chiplet Actuary: A Quantitative Cost Model and Multi-Chiplet Architecture Exploration

MCM是传统封装,InFO和2.5D都是先进封装的一种形式;图片中成本为相对于100平方毫米的 SoC 芯片的成本关系比例

Chiplet产品

国内外主流AI芯片设计公司都已开始布局Chiplet产品,而且部分公司的相关产品已经量产落地,验证了Chiplet产品的可行性

- 从应用场景来看,大部分公司的产品主要应用于AI领域,但AMD、苹果的部分产品应用于个人电脑领域用来提升产品的性能,且Chiplet在汽车领域的应用有一定应用。

- 从产品类型来看,Chiplet产品主要是对性能要求较高的CPU、GPU和加速卡等。

- 从产品制程来看,国外芯片设计公司的产品制程一般在7nm及以下,但是国内公司受制于设计能力、供应链等,部分Chiplet产品的制程在12nm甚至14nm。

- 从产品落地来看,国外芯片公司如AMD、英伟达等都已经有了量产产品,国内虽然有Chiplet产品的公司较多,但根据了解只有寒武纪和芯动科技真正量产,初创公司原粒半导体等企业值得关注,目前Chiplet产品越来越多的量产落地也验证了产品的可行性。

如何学习AI大模型?

现在社会上大模型越来越普及了,已经有很多人都想往这里面扎,但是却找不到适合的方法去学习。

作为一名资深码农,初入大模型时也吃了很多亏,踩了无数坑。现在我想把我的经验和知识分享给你们,帮助你们学习AI大模型,能够解决你们学习中的困难。

我已将重要的AI大模型资料包括市面上AI大模型各大白皮书、AGI大模型系统学习路线、AI大模型视频教程、实战学习,等录播视频免费分享出来,需要的小伙伴可以扫取。

一、AGI大模型系统学习路线

很多人学习大模型的时候没有方向,东学一点西学一点,像只无头苍蝇乱撞,我下面分享的这个学习路线希望能够帮助到你们学习AI大模型。

二、AI大模型视频教程

三、AI大模型各大学习书籍

四、AI大模型各大场景实战案例

五、结束语

学习AI大模型是当前科技发展的趋势,它不仅能够为我们提供更多的机会和挑战,还能够让我们更好地理解和应用人工智能技术。通过学习AI大模型,我们可以深入了解深度学习、神经网络等核心概念,并将其应用于自然语言处理、计算机视觉、语音识别等领域。同时,掌握AI大模型还能够为我们的职业发展增添竞争力,成为未来技术领域的领导者。

再者,学习AI大模型也能为我们自己创造更多的价值,提供更多的岗位以及副业创收,让自己的生活更上一层楼。

因此,学习AI大模型是一项有前景且值得投入的时间和精力的重要选择。

2027

2027

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?