浅析FPGA局部动态可重构技术

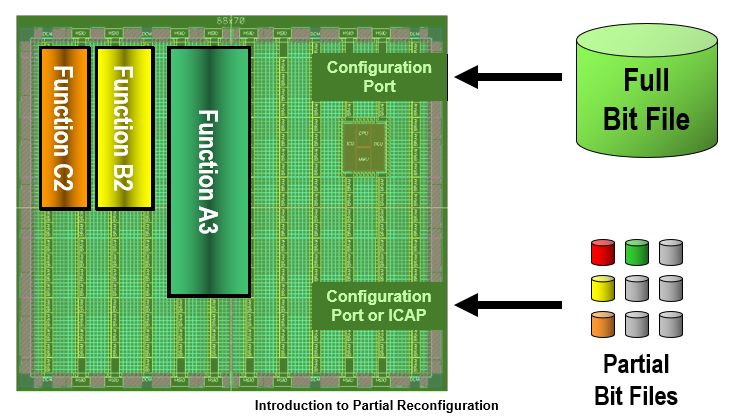

所谓FPGA动态可重构技术,就是要对基于SRAM编程技术的FPGA实现全部或部分逻辑资源的动态功能变换。根据实现重构的面积不同,动态可重构技术又可分为全局重构和局部重构。

1、何为局部动态可重构

局部动态可重构可以简单的理解为通过下载局部分区bit 文件来动态修改对应分区的逻辑功能,同时其余分区的逻辑功能持续运行而不中断。

2、局部动态可重构技术的优势

a、系统灵活性:可以在保持通信连接的同时执行更多的系统功能;

b、降低FPGA资源和成本:通过分时复用的方式降低FPGA硬件尺寸;

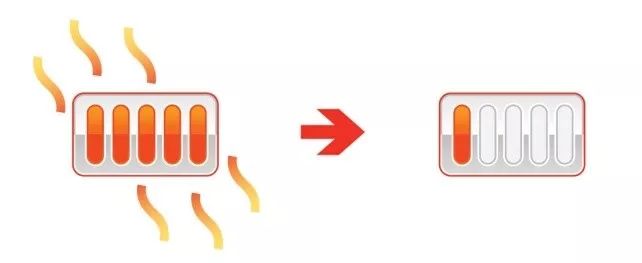

c、降低功耗:通过卸载掉暂时不用的局部逻辑的方式降低FPGA功耗;

3、 FPGA局部动态重构流程

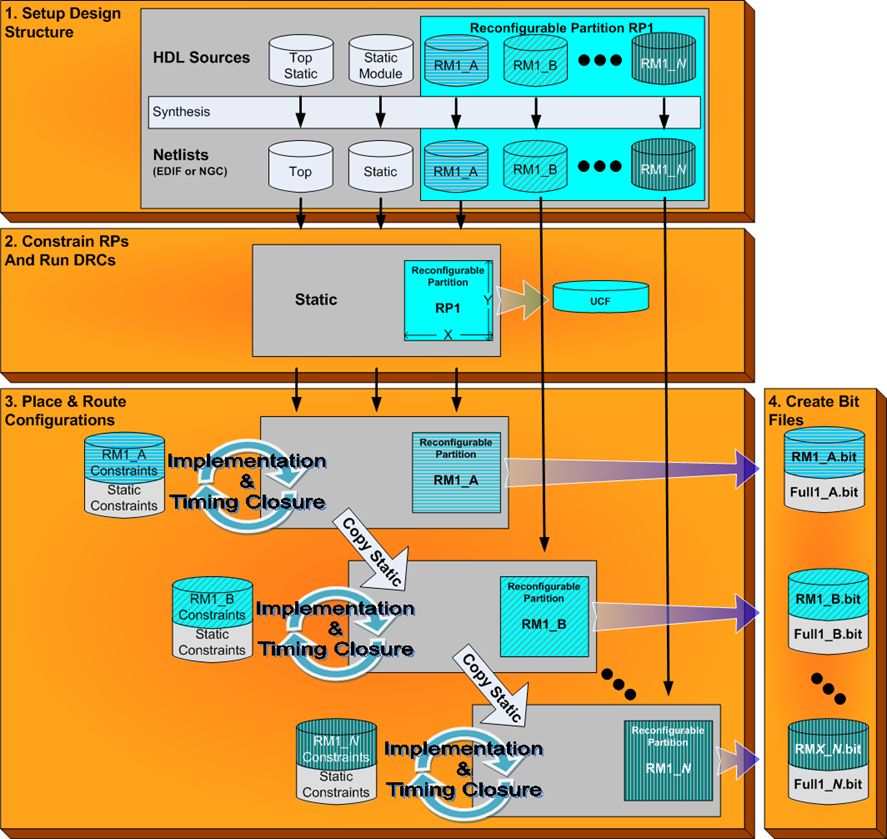

a、规划系统整体框架和可重构模块框架,编写各模块HDL代码,综合生成各子模块网表文件;

b、规划分区以及给各分区分配足够资源,创建各分区及静态部分的时序约束文件,执行DRC检查;

c、对各分区进行布局布线配置;

d、遍历各种可能的配置,编译生成全局bit文件和可重构模块的局部bit文件。

4、局部动态可重构的时序问题

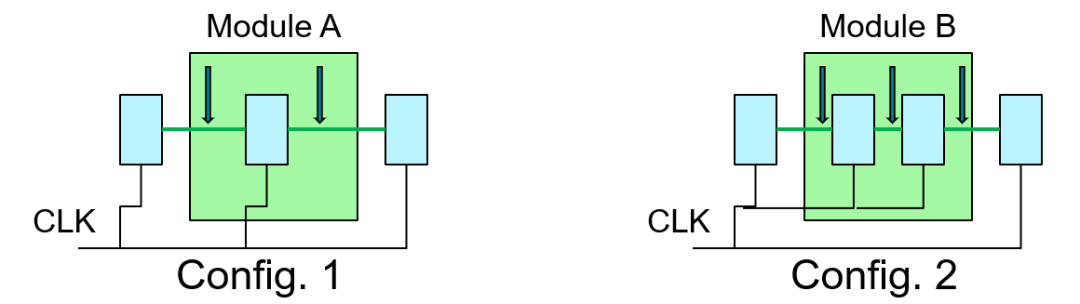

如上图所示,局部重构会带来时序路径的变化,使得局部可重构工程的时序约束问题变得更加复杂。

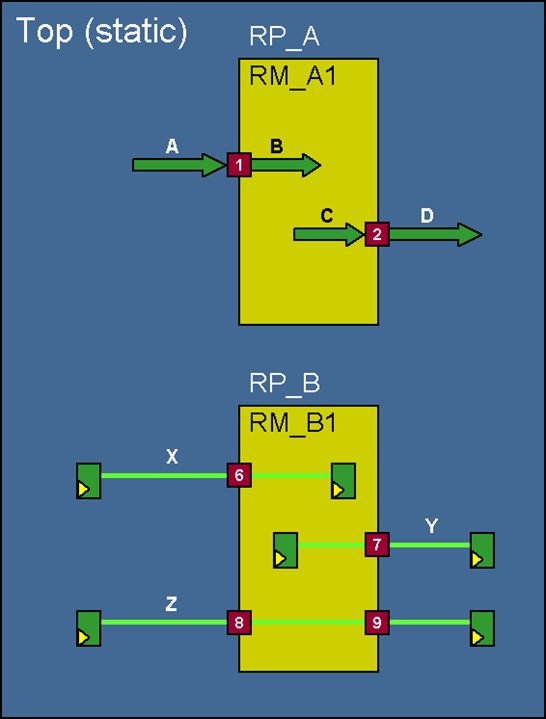

解决方法:在静态逻辑和可重构模块间的信号传递路径上添加代理逻辑点,如下图红色数字点,将单条时序路径分割为两个独立的部分,然后分别对两部分的路径进行单独约束,以达到时序要求。

- END -

NOW现在行动!

推荐阅读

【Vivado那些事】如何查找官网例程及如何使用官网例程【Vivado使用误区与进阶】总结篇【Vivado那些事】Vivado中常用的快捷键(二)其他常用快捷键SystemVerilog数字系统设计_夏宇闻 PDFVerilog 里面,always,assign和always@(*)区别图书推荐|ARM Cortex-M0 全可编程SoC原理及实现

简谈:如何学习FPGA拆解1968年的美国军用电脑,真的怀疑是“穿越”啊!高级FPGA设计技巧!多时钟域和异步信号处理解决方案现代计算机的雏形-微型计算机MCS-4AD9361 和Zynq及其参考设计说明1202年了,还在使用虚拟机吗?Win10安装Ubuntu子系统及图形化界面详细教程谈谈Xilinx FPGA设计的实现过程

Github 上有哪些优秀的 VHDL/Verilog/FPGA 项目

AD936x+ZYNQ搭建收音机(一)

AD936x+ZYNQ搭建收音机(二)含视频演示

AD936x+ZYNQ搭建收音机(三)-终篇

AD936x+ZYNQ搭建OpenWIFI

Verilog 版本:Verilog-95、Verilog-2001与System Verilog区别简谈

FPGA时钟设计方案无招胜有招-Vivado非工程模式下的详细设计

追寻ARM的起源-Acorn电脑简史及FPGA实现

面试中经常会遇到的FPGA基本概念,你会几个?

Xilinx FPGA MIPI 接口简单说明

介绍一些新手入门FPGA的优秀网站

Vivado ML(机器学习) 2021尝鲜

推荐一些可以获取免费的国外的原版书籍(电子版)网站

【Vivado那些事】FPGA的配置方式

FPGA 的重构

点击上方字体即可跳转阅读

本文探讨了FPGA局部动态可重构技术的原理,优势,包括系统灵活性、资源节省和功耗降低。深入解析了重构流程,并关注了时序问题的解决方案。适合了解FPGA设计者和工程师参考。

本文探讨了FPGA局部动态可重构技术的原理,优势,包括系统灵活性、资源节省和功耗降低。深入解析了重构流程,并关注了时序问题的解决方案。适合了解FPGA设计者和工程师参考。

7287

7287

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?