童年修复系列-SNES芯片组介绍及FPGA实现

超级任天堂1990年11月21日在日本开始发售,北美于1991年8月13日发售,欧洲于1992年4月11日发售。

超级任天堂,简称超任,是任天堂公司开发的家用游戏机。英文名称Super Famicom,简写SFC;在欧美洲销售的产品名为Super Nintendo Entertainment System,简写SNES。超级任天堂是任天堂红白机的后继机种。由于芯片组的复杂,中国鲜有“复制品”出现。

所以今天就来聊一聊SNES的芯片组及其特殊性,同时带来FPGA实现SNES的开源方案。

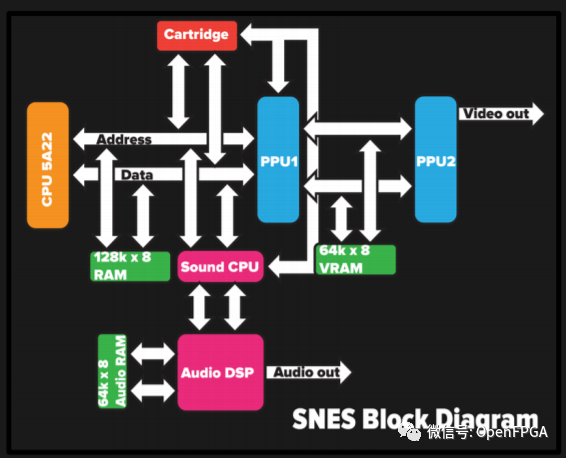

SNES和现今的PC芯片组很相似-CPU+显卡+声卡组成,同时SNES为了处理复杂的运算增加了一颗DSP芯片,下面就按照组成一个一个介绍。

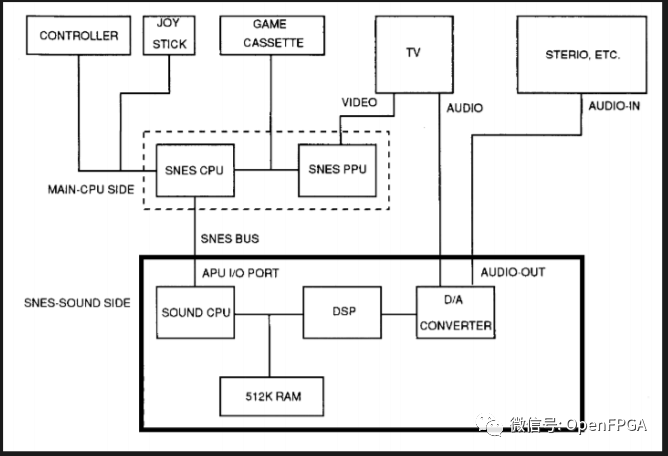

下图是整机的框图:

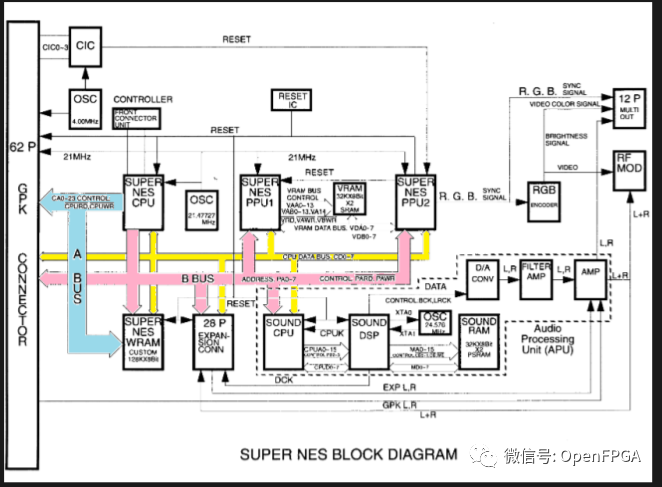

整机的总线互联如下:

CPU总线使用的是从6502继承过来的类ISA总线。

CPU

SNES 的 CPU (中央处理单元)是基于 65c816 的处理器-5A22《一块带给无数人年少欢乐的CPU,别说你没用过它在00-中的硬件寄存器);用于慢速访问(即和)和用于非常慢的访问(即4000-在00 到 $3F 中的硬件寄存器 )。这种变速模式来源于6502有一个叫做“ZERO-PAGE”的寻址模式,但是进行了进一步扩展。

它是一个带有 24 位总线的 16 位处理器(16 位数据指针和 8 位组指针)。支持16MB的寻址空间。它有一个计算器和两个寄存器,可以在8位或16位模式之间切换。

然而,它具有许多寻址模式。它使用可变宽度指令。单个指令的宽度可以根据某些寄存器的长度而变化。

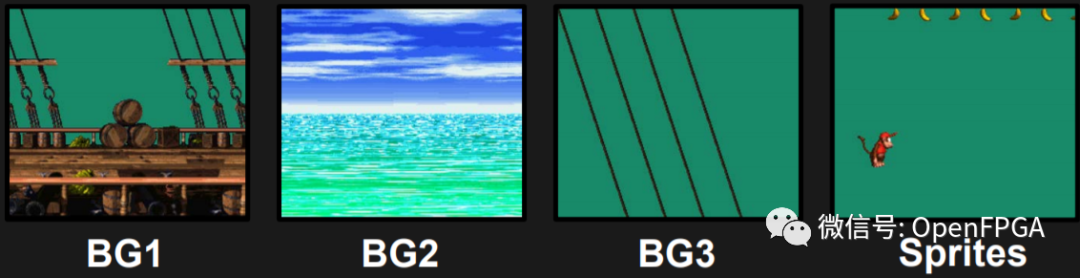

PPU

SNES有两个特制的图像处理器,主要运行于256×224的分辨率,最高支持512x448的分辨率,最大发色数32768色,最大同屏幕显示256色,最大活动块数为128个,并支持缩放、回旋、马赛克、半透明、窗口、光栅等特效。

声优芯片

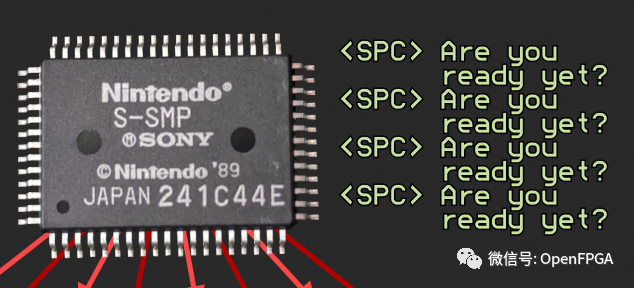

辅助CPU采用一颗SPC700(索尼推出),是一个8位的CPU核心,很接近6502,但有一些不同的寻址模式和复数/分割指令,与一个定制的数字声音信号处理器共同集成在一个模块中。SPC700和65c816通过一个4路双向通道(8位I/O端口)通讯。SPC700有自己独立的64K内存,可以用来存储声音采样或者从65c816下载的程序。CPU有一个内建的64K ROM开机码,用来通过65c816从游戏ROM里加载更多的复杂程序或者采样数据。这个ROM可以被关闭,以存储开机码的64K RAM来代替它的工作。

声音数字信号处理器(Sound DSP)只能播放压缩的声音采样。这种使用一固定比率的压缩算法,可以将16个16位声音采样压缩成8字节加一字节标题的形式。一个采样的最小单位是一个区块,区块的标题字节包含一个移位和一个过滤值(算法解压信息),再加上一个最后区块标记和一个循环标记。循环标记仅仅在最后区块标记存在时才使用。

在同一时间内,最多允许有8个声音通道同时播放声音采样,每个声音通道都有单独的左右声道音量和频率的调节。每个通道都可以定义一个硬件音量调节,并各自设置其回声效果,不过复合的回声效果必须受制于一个8路的FIR声音分流器。一个通道的声音输出可以用来调整在数字序列上的下一个声音通道的频率。DSP也有一个白噪音源,可以播放一个替代采样数据的声音通道。所有的8个音源连同回声数据最后都混合到一个双通道的主音量控制下。DSP有3个间隔定事器,头两个运行在8KHz下,最后一个是64KHz。游戏通常只使用三个中的一个来输出一个恒定的音乐回放频率。

顺便一提SNES的声音处理芯片SPC700是PS之父久多良木负责设计的,所以说索尼大法好可不是白叫的。

声优芯片和整机总线如下图所示:

扩展芯片

数字信号处理器

SNES 的 S-DSP (数字信号处理器)用于向扬声器输出数据。产生的声音以 32 KHz 运行。S-DSP 使用比特率降低将所需的大小减少到原始大小的 9/16。S-DSP 是「自带鬼畜」,你输入一个PCM格式的音源进去,比如把F♂A乐器输入进去,然后往sound chip的寄存器里写入你要的包络,音调之类的,sound chip上的协处理器就会帮你处理输出,其实就和做音乐用的合成器播放软音源差不多。

DSP-1

DSP-1是一种主要用于数学和伪 3D 投影的芯片。这通常使用model 7。这是其中最常用的芯片。它也适用于 2D 旋转等。

SA-1

SA-1是 CPU 的更快版本,但在访问方面存在一些差异。它带有“I-RAM”和“BW-RAM”。它通常以大约 11 MHz 的速度运行,当访问与 CPU 相同的东西时,它的速度为 5 MHz。

GSU

GSU是著名的 SuperFX 芯片的技术名称。GSU 可用于绘制颜色。它在很多方面都比 SNES 的 CPU 更强大。它是一个伪RISC。它可用于绘制许多事物,例如精灵和对象的旋转或制作伪 3D 效果。

CX4是 Capcom 使用的芯片,它在三角和图形方面非常强大。它可以绘制线条、波浪和 3D 线框,旋转精灵并进行三角计算等。应用到的游戏包括:洛克人X2,洛克人X3 等卡普空街机移植作品。

SDD-1

数据解压芯片,解压使用 ASIC 无算压缩算法压制的数据,它活跃在 SFC 主 CPU 和 ROM之间,负责透明实时数据解压工作,针对一些资源太大的游戏,为了节省卡带空间成本而引入了该芯片,使用游戏包括:星之海洋,街霸 Alpha 2 等。

SNES FPGA实现

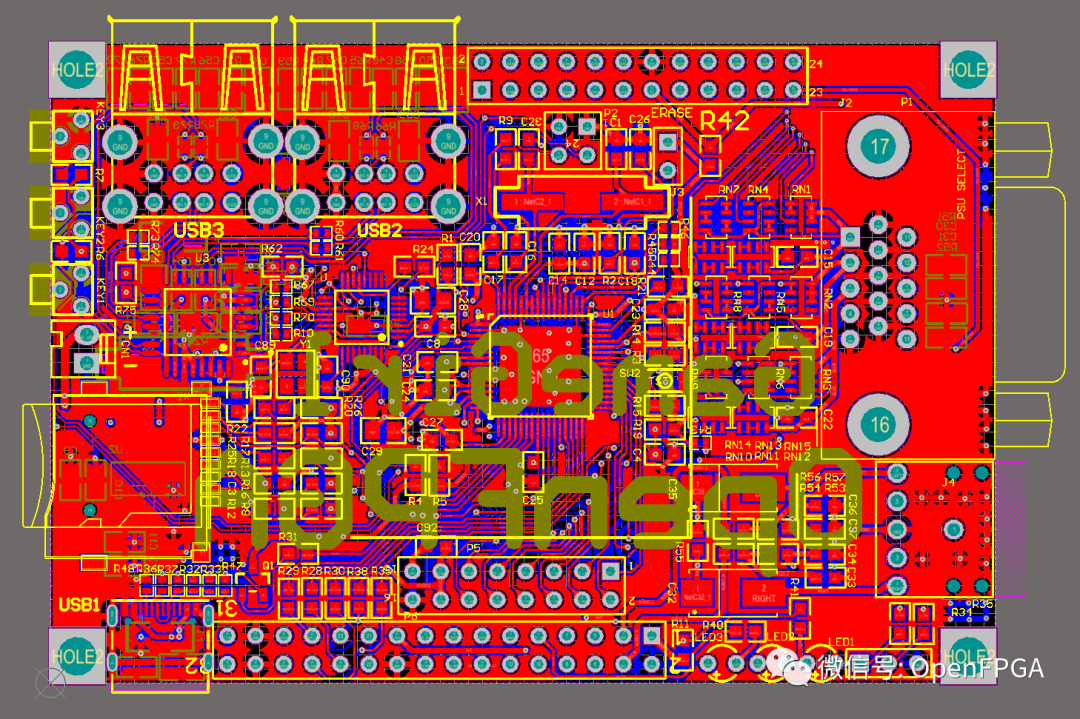

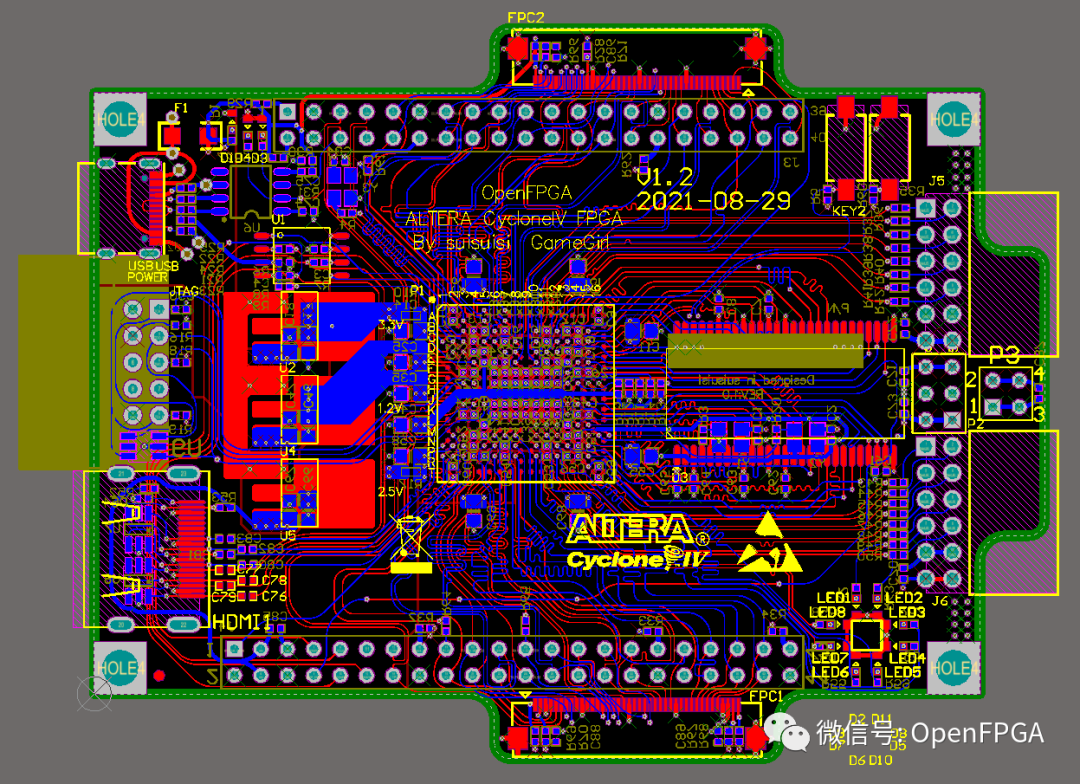

硬件

还是GameGirl硬件

开源地址:

https://github.com/suisuisi/gamegirl/tree/master/Hardware

FPGA程序

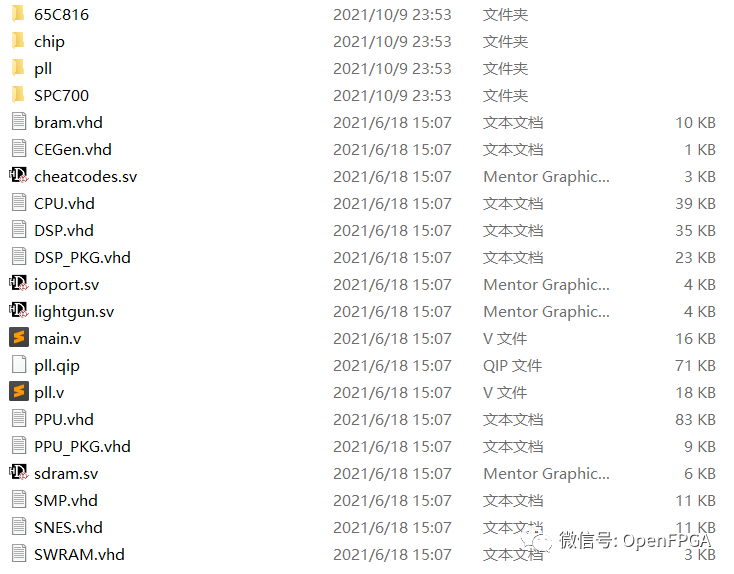

上面的CPU和SPC700都已经介绍过了。

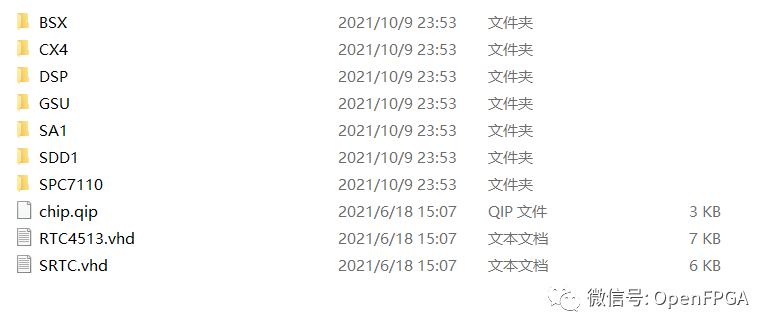

chip文件夹下还有上面介绍的芯片,组成芯片组:

开源地址:

https://github.com/suisuisi/gamegirl/tree/master/CoreCPU/SNES

使用方法:

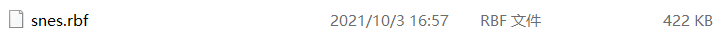

将编译产生的.rbf文件拷贝到SD卡的根目录:

产生的二进制文件在下面路径:

https://github.com/suisuisi/gamegirl/tree/master/Binaries/cores/snes

然后将游戏同步放到SD卡里,通过OSD就可以选择游戏,注意游戏启动及中间过渡阶段会有黑屏,所以需要等待。。。

视频

时间仓促还没来得及拍视频,后续补上。

NOW现在行动!

学习Xilinx FPGA最好的资料其实就是官方手册,下表总结了部分手册的主要介绍内容,关注我,持续更新中......

| 文件名 | 主标题 | 内容简单介绍 | 是否有中文版 | |

| UG476 | 7 Series FPGAs GTX/GTH Transceivers | GTX和GTH介绍,PCIe、serdes等学习必备 | 否 | |

| UG471 | 7 Series FPGAs SelectIO Resources | 描述 7 系列 FPGA 中可用的 SelectIO资源。 | 否 | |

| UG1114 | PetaLinux Tools Documentaton | PetaLinux 工具文档 参考指南 | 是,V2019.2 | |

| UG949 | UltraFAST 设计方法指南(适用于 Vivado Design Suite) | 赛灵思® UltraFast™ 设计方法是用于为当今器件优化设计进程的一套最佳实践。这些设计的规模与复杂性需要执行特定的步骤与设计任务,从而确保设计每一个阶段的成功开展。依照这些步骤,并遵循最佳实践,将帮助您以最快的速度和最高的效率实现期望的设计目标 | 是,V2018.1 | |

| IP手册 | pg057 | FIFO Generator | FIFO生成器IP使用手册 | 否 |

| pg104 | Complex Multiplier | 复数乘法器IP使用手册 | 否 | |

| pg122 | RAM-Based Shift Register | 移位寄存器IP使用手册 | 否 |

推荐阅读

【Vivado那些事】Vivado中常用的快捷键(二)其他常用快捷键

图书推荐|ARM Cortex-M0 全可编程SoC原理及实现

Github 上有哪些优秀的 VHDL/Verilog/FPGA 项目

高速串行通信常用的编码方式-8b/10b编码/解码

Verilog计时(微秒、毫秒和秒)脉冲的产生及同步整形电路

再说System Verilog 与 Verilog 的关系

本文介绍了超级任天堂SNES的芯片组,包括基于65c816的CPU、图像处理器PPU、SPC700声音芯片以及扩展芯片如DSP-1和SA-1等。文章还提到了SNES的FPGA实现方案,分享了开源项目链接,并提及了相关硬件和软件资源。此外,文章还讨论了SNES声音处理芯片SPC700的特性及其在PlayStation之父久多良木健的设计背景。

本文介绍了超级任天堂SNES的芯片组,包括基于65c816的CPU、图像处理器PPU、SPC700声音芯片以及扩展芯片如DSP-1和SA-1等。文章还提到了SNES的FPGA实现方案,分享了开源项目链接,并提及了相关硬件和软件资源。此外,文章还讨论了SNES声音处理芯片SPC700的特性及其在PlayStation之父久多良木健的设计背景。

433

433

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?