工程设计原理:

根据公式:被除数=商数·除数+余数,将被除数减去除数,每减一次,商的中间结果加一,直至被除数等于或者小于除数,运算完成,此时,被除数被减剩的结果就是余数。

根据以上的思想,设计由加法器和减法器组成的除法器。

引入一个sign信号,,被置为‘0’时,进行无符号的运算。

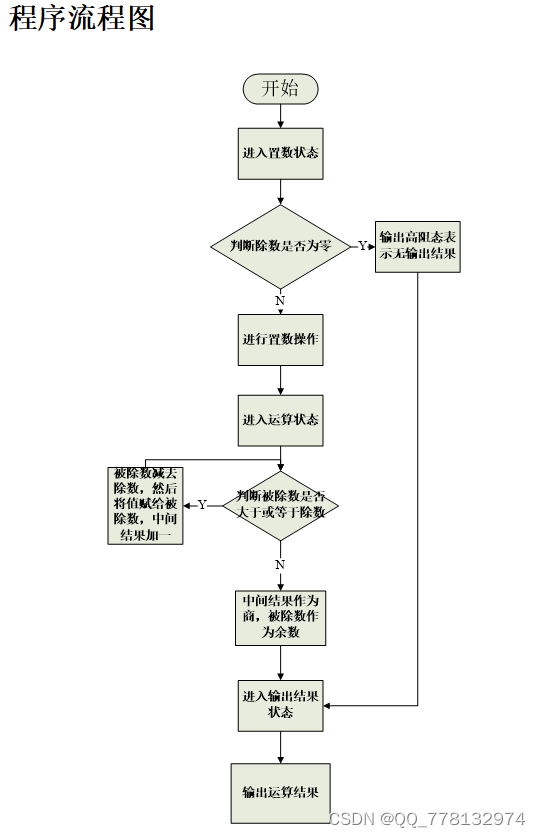

采用三个状态机控制运算的流程:

第一个步骤是置数,置数后进行判断除数是否为零,如果为零,则输出结果为高阻态。如果不是零则,进入第二个步骤,即运算状态

第二个步骤是进行运算,根据传统除法器的运算方法进行运算,即被除数=商数·除数+余数,判断被除数是否大于除数,如果大于或等于除数,将被除数减去除数,再将差赋给被除数,中间结果加一。如果小于除数,则退出运算,将中间结果作为商输出,被除数作为余数输出。

第三个步骤是进行结果的输出,然后重新回到第一个步骤,重新进行置数操作,以此循环。

根据公式:被除数=商数·除数+余数,将被除数减去除数,每减一次,商的中间结果加一,直至被除数等于或者小于除数,运算完成,此时,被除数被减剩的结果就是余数。

根据以上的思想,设计由加法器和减法器组成的除法器。

由于是任意四位除法器,所以输入的被除数和除数存在有符号和

订阅专栏 解锁全文

订阅专栏 解锁全文

6793

6793

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?