ISERDES/OSERDES

ISERDES模块的作用在于实现高速源同步输入数据的串并转换。

OSERDES模块的作用在于实现高速源同步输出数据的并串转换。

- SERDES支持SDR和DDR两个模式。

- SDR模式支持2、3、4、5、6、7、8bit位宽;

- DDR模式支持4、6、8bit位宽,10或14bit位宽需要两个模块级联。

- Bitslip模块可以使设计者重新排列输入的并行数据,可用于源同步。

1. ISERDES

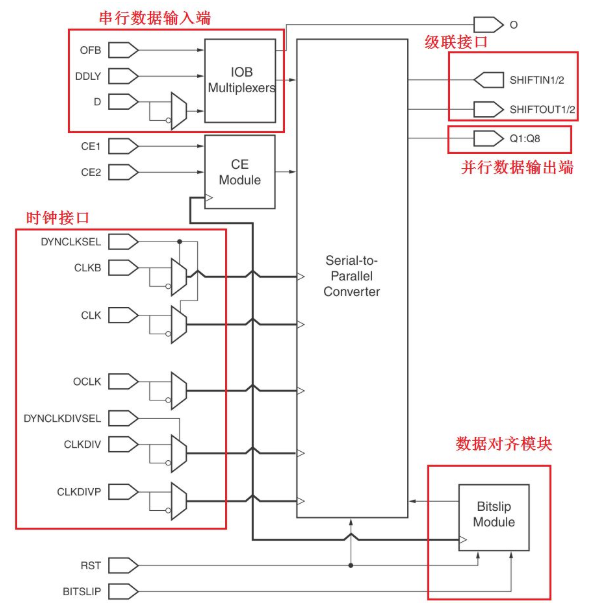

ISERDES接收外部输入FPGA的高速源同步串行信号,再FPGA内部将其转换成用户需要的并行数据。ISERDES的功能框图如下所示。

-

串行数据输入端

该部分接收外部输入的高速源同步数据,数据模式可以是SDR或者DDR。在SDR模式下,数据转换的位宽可以胃2,3,4,5,6,7,8bit。在DDR模式下,数据位宽可以是4,6,8bit。如果是两个iserdes模块级联使用,DDR模式还可以支持10,14bit。 -

时钟接口

该部分提供高速源同步串行时钟、并行数据获取时钟以及控制时钟。下图为源时钟接入ISERDES2模块的用法。

-

并行数据输出端

该部分输出用户所需的并行数据,SDR模式下,位宽为2,3,4,5,6,7,8bit;DDR模式下,位宽为4,6,8,10,14bit。 -

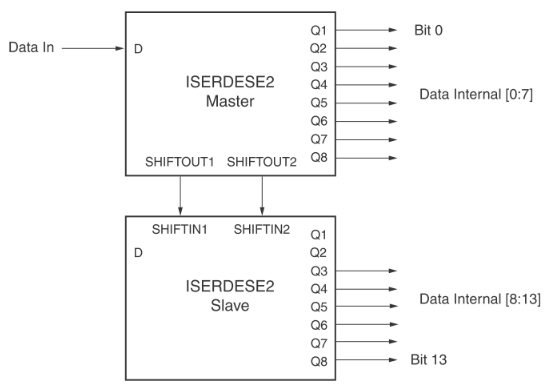

级联接口

该部分是实现DDR模式下10,14bit位宽的关键接口,通过该接口与两外一个ISERDES2级联,两者共同完成10bit,14bit数据的串并转换。如下图所示。

注意:对于级联模式下的slave,数据接口从Q3开始有效,Q1,Q2无效。

- 数据对齐模块

该部分称为Bitslip模块,用来实现并行数据的边界对齐。下图给出了Bitslip模块的工作方式。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

7575

7575

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?