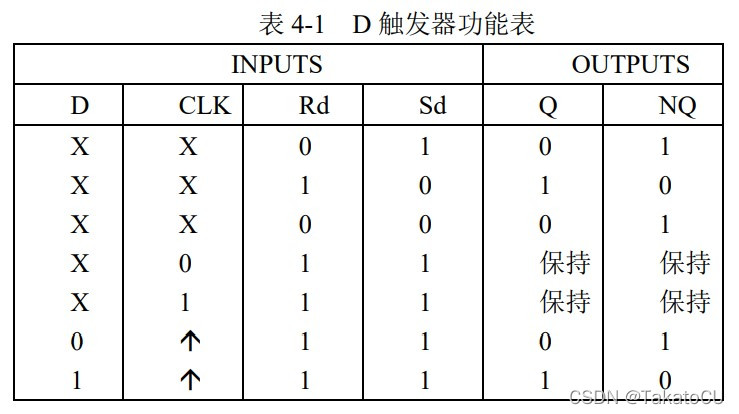

要求:

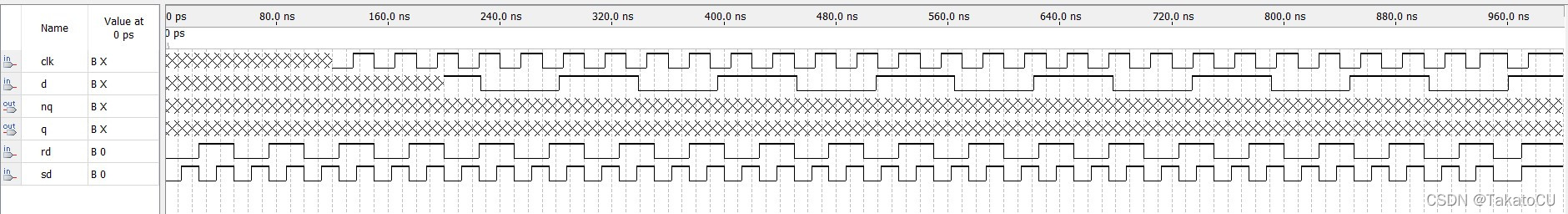

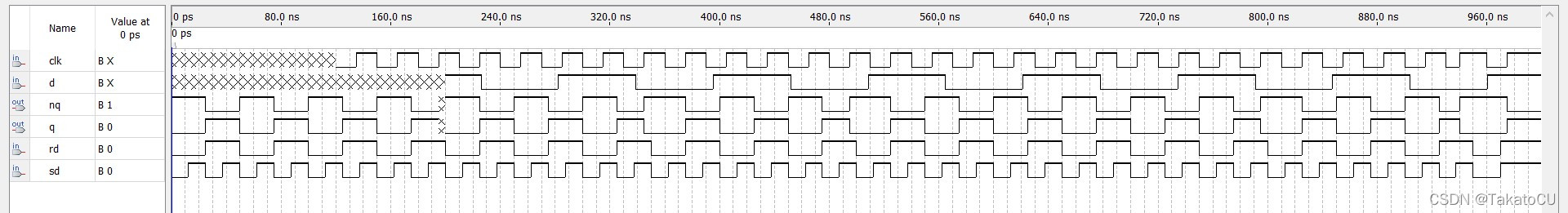

仿真波形:

仿真前:

仿真后:

代码:

module DDD(d,clk,rd,sd,q,nq);

input d,clk,rd,sd;

output q,nq;

reg q,nq;

always @(posedge clk or negedge rd or negedge sd)begin

if(rd==0)begin

q<=0;

nq<=1;

end

else begin

if(sd==0)begin

q<=1;

nq<=0;

end

else begin

if(d==0)begin

q<=0;

nq<=1;

end

else if(d==1)begin

q<=1;

nq<=0;

end

end

end

end

endmodule

本文介绍了如何使用Verilog语言设计一个具有异步清零和置位功能的D触发器。通过详细的仿真波形对比,展示了在不同信号输入下触发器的工作状态,并提供了实现该功能的源代码。

本文介绍了如何使用Verilog语言设计一个具有异步清零和置位功能的D触发器。通过详细的仿真波形对比,展示了在不同信号输入下触发器的工作状态,并提供了实现该功能的源代码。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

7242

7242

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?