随机存取存储器(RAM)

RAM(Random Access Memory)既可向指定单元存入信息又可从指定单元读出信息。任何RAM中存储的信息在断电后均会丢失,所以RAM是易失性存储器。所谓“随机存取”,指的是当存储器中的数据被读取或写入时,所需要的时间与这段信息所在的位置或所写入的位置无关(区别于顺序存储)。

1.静态随机存储器(SRAM)

1.1 基本存储单元

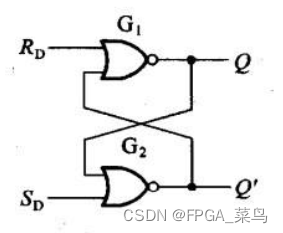

SRAM的基本存储位元是由锁存器构成的。锁存器可以存储一位二进制数,是由其结构决定的。下图是一个基本RS锁存器。

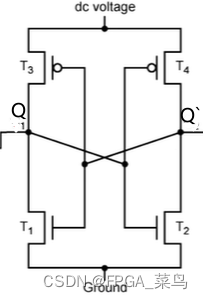

对SRAM的基本存储单元来说,不需要RD和SD端,则两个或非门简化成了非门。在这样的锁存器中,Q只能为0或1两种状态,取决于当时存储的数据。对应的CMOS结构如下(两个非门首位相接):

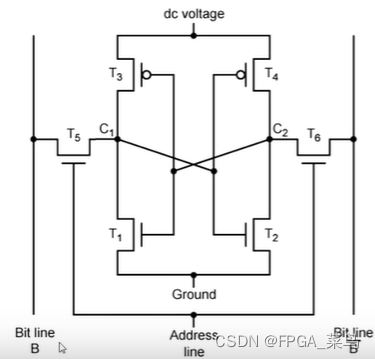

除了存储外,数据还需要能修改。将其结构进行改进,增加T5、T6两个NMOS,如下图所示。首先,通过地址线,选中这一基本单元,使T5、T6导通;随即在位线上写入待写的数据。此结构就是SRAM的基本位元。

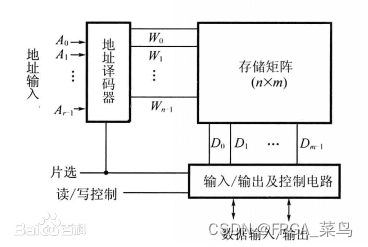

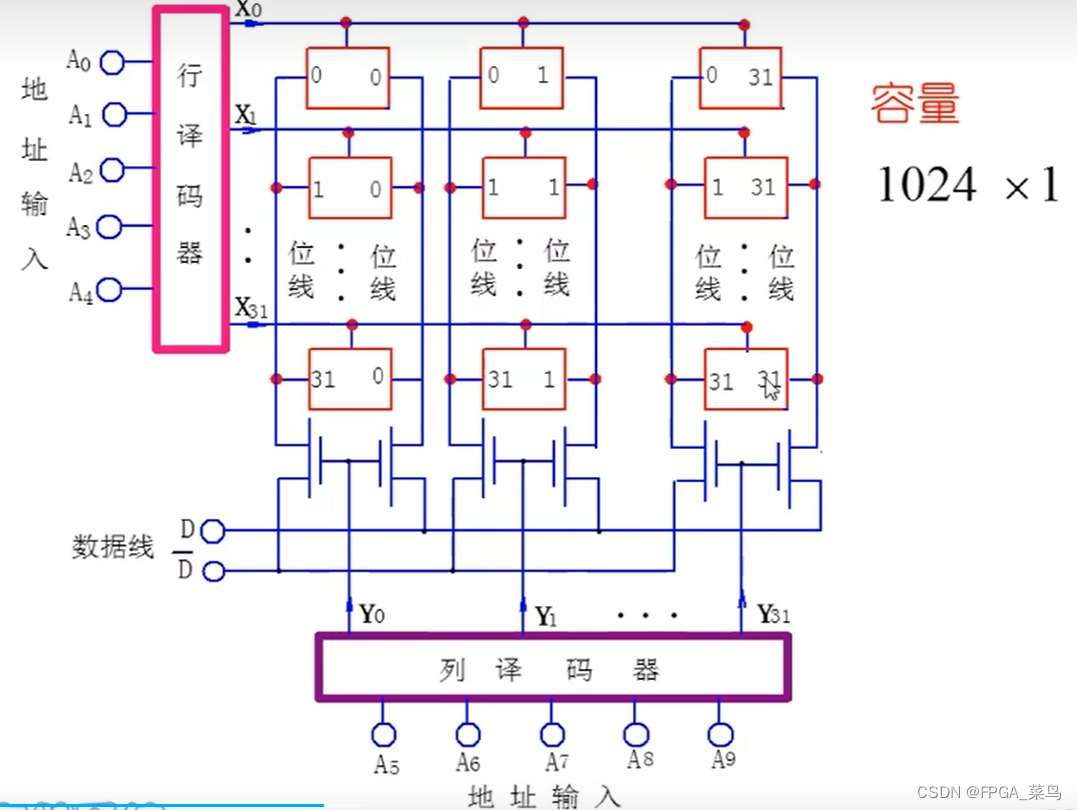

1.2 整体结构

下图是双地址译码的SRAM。如果你熟悉这种结构,就能发现,很多小型存储器的整体结构类似,只是存储位元不同。

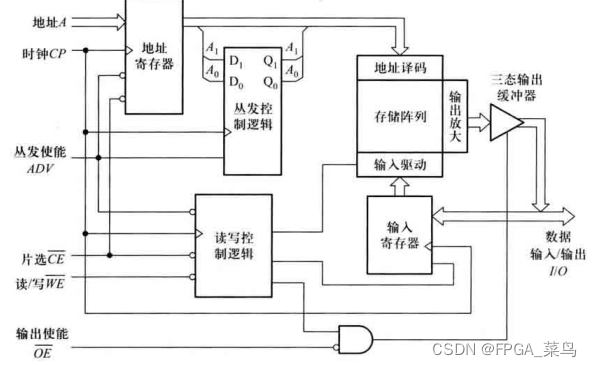

1.3同步静态随机存储器(SSRAM)

SSRAM(synchronous SRAM)是一种在SRAM基础上发展起来的,适合高速存取的RAM。其与SRAM最大的区别在于:前者的读写操作是在时钟脉冲节拍控制下完成的。在时钟有效沿到来时,地址、数据、控制信号被锁存到其内部的寄存器中,然后由内部进行读写操作。这种工作方式使其应用非常方便,用户只需围绕时钟的有效沿设计所有的输入信号即可;而普通SRAM则需严格按照时序输入地址、数据、控制信号等,要求较高,难以提升速度。

同步SRAM的另一个特点是从发,ADV端使能为1时,外部只需给一个首地址,就能连续读写接下来若干个地址单元。上图中的例子最多连续读四个地址单元,如果ADV使能信号不复位,则计数器循环计数,该地址也被循环读写。超高速缓冲存储器Cache使用的就是SSRAM。

RAM是一种易失性存储器,数据在断电后丢失。SRAM基于锁存器结构,用于快速访问,而SSRAM在SRAM基础上增加了时钟同步,便于高速存取,读写操作受时钟脉冲控制。SSRAM允许连续读写多个地址单元,常用于Cache。

RAM是一种易失性存储器,数据在断电后丢失。SRAM基于锁存器结构,用于快速访问,而SSRAM在SRAM基础上增加了时钟同步,便于高速存取,读写操作受时钟脉冲控制。SSRAM允许连续读写多个地址单元,常用于Cache。

6392

6392

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?