1.软件版本

quartusii

2.本算法理论知识

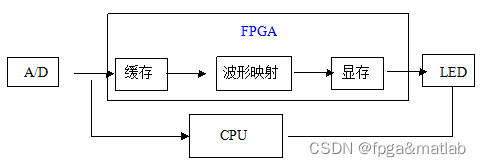

框图结构:

1.缓存里包含有触发控制和触发存储器;

2.由设计指标需要1GsPs的采样率,最后的数据流要降到到250MbPs;

3.从指标来看从波形的数据采集到最后的显示时间要在10s;

4.LED的选择要能和波形映射模块相对应;

5.整个设计主要就包含两个部分,FPGA的波形协处理器这几以及最后的LED显示;

6.二维显示效果,非三维;

步骤一:数据采集模块

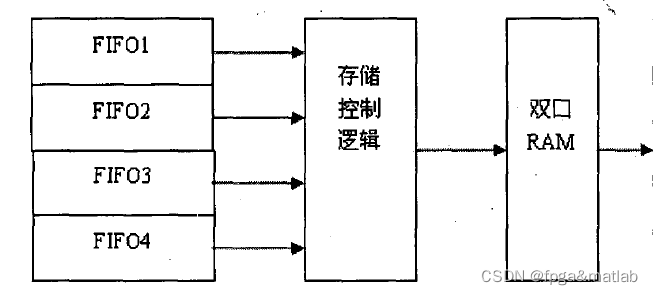

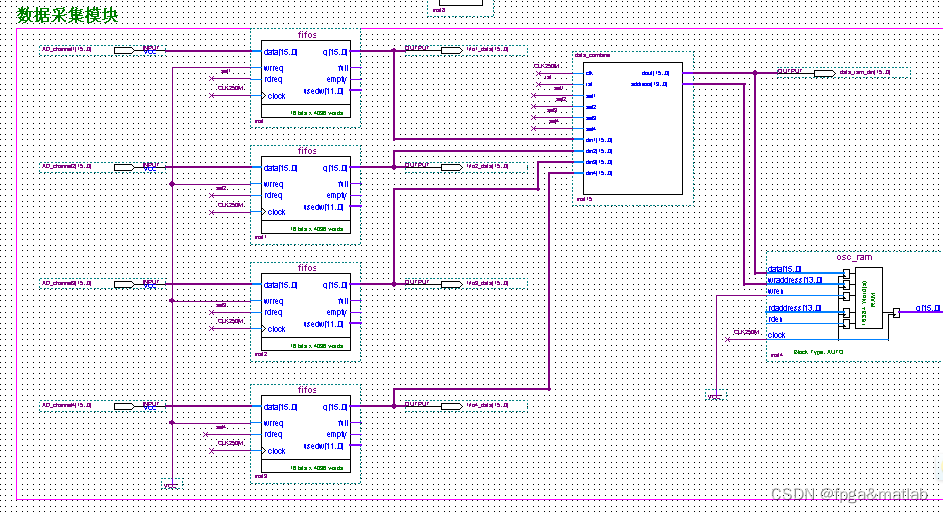

首先将外部输入的1G的数据通过思路FIFO缓存,变为每路250M数据,即一路高速数据转换为多路低速数据,从而使其能够在FPGA中进行工作。这个时候需要将系统的时钟倍频到250M。

那么,这里在QII中设计如下的结构:

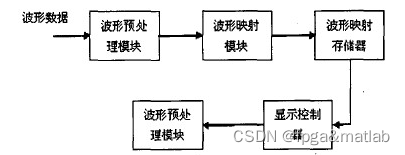

步骤二:示波器显示模块

波形映射模块就是将经过抽点后的波形数据映射到波形映射库中,映射库中的每个存储单元都是对应LCD显示器上的一个点,于是将需要显示的点的波形数据转换成幅度,幅度在LCD上标示为垂直方向的值,所以抽点后的每一个显示点都对应LCD上的一个像素点。横坐标代表时伺信息,纵坐标代表幅值信息。这样就可以将多次采样得到的波形数据映射到同一个映射库中,相当于将多次采集的波形重叠起来显示在一起,体现了高捕获率的作用,显示效果也达到了高刷新率的要求。

3.部分核心代码

module display(

clk,

cs,

datain,

RDADDR,

x_out,

y_out,

da_wrx,

da_wry

);

input clk;

input cs;

input [7:0] datain;

output reg [9:0] RDADDR;

output [7:0] x_out;

output [7:0] y_out;

output reg da_wrx,da_wry;

reg link_xout,link_yout;

reg [12:0] counttemp;

reg [2:0] bittemp;

reg [7:0] xbuf;

reg [7:0] ybuf;

parameter GET = 10'b0_000_000_001,

COMPARE1 = 10'b0_000_000_010,

COMPARE2 = 10'b0_000_000_100,

COMPARE3 = 10'b0_000_001_000,

COMPARE4 = 10'b0_000_010_000,

COMPARE5 = 10'b0_000_100_000,

COMPARE6 = 10'b0_001_000_000,

COMPARE7 = 10'b0_010_000_000,

COMPARE8 = 10'b0_100_000_000,

NEWCOUNT = 10'b1_000_000_000;

reg [9:0] state;

assign x_out=link_xout?xbuf:8'bz;

assign y_out=link_yout?ybuf:8'bz;

always @(posedge clk)

begin

if (cs)

begin

state<=GET;

link_xout<=0;

link_yout<=0;

counttemp<=0;

bittemp<=0;

da_wrx<=1;

da_wry<=1;

end

else

begin

link_xout<=1;

link_yout<=1;

case (state)

default: begin //GET

RDADDR<=counttemp[12:3];

bittemp<=7-counttemp[2:0];

state<=COMPARE1;

da_wrx<=1;

da_wry<=1;

end

COMPARE1: begin

da_wrx<=0;

da_wry<=0;

if (datain[bittemp])

begin

xbuf<={counttemp[6:0],1'b0};

ybuf<={counttemp[12:7],1'b0};

state<=COMPARE2;

end

else

begin

xbuf<=0;

ybuf<=0;

state<=NEWCOUNT;

end

end

COMPARE2: begin

da_wrx<=1;

da_wry<=1;

state<=COMPARE3;

end

COMPARE3: begin

state<=COMPARE4;

end

COMPARE4: begin

state<=COMPARE5;

end

COMPARE5: begin

state<=NEWCOUNT;

end

NEWCOUNT: begin

state<=GET;

if (counttemp==8191)

counttemp<=0;

else

counttemp<=counttemp+13'b1;

end

endcase

end

end

endmodule 4.操作步骤与仿真结论

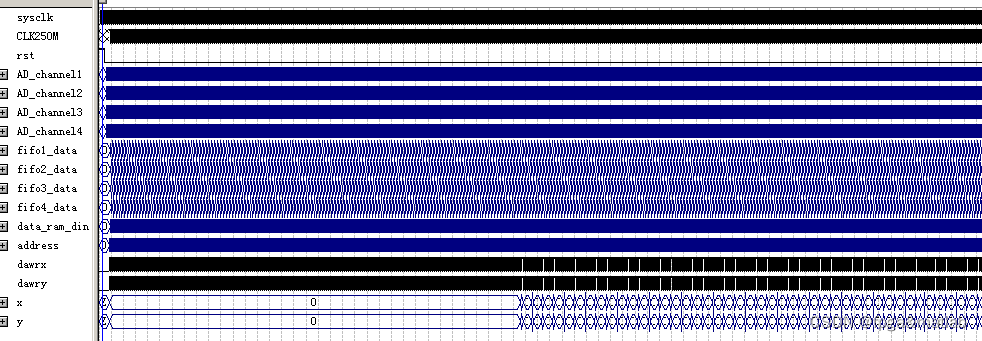

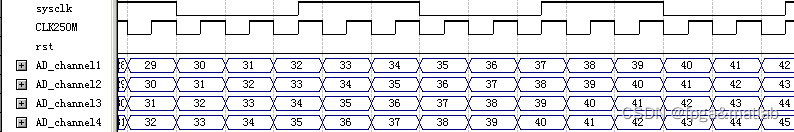

系统的仿真结果如下所示:

仿真波形含义为:

分别为系统时钟,以及250M的时钟,用于读取外部输入的AD数据。

Rst为系统的复位信号,0的时候系统正常工作。

下面四个就是思路进入FPGA的采集得到的信号。这四个信号将通过四个FIFO。

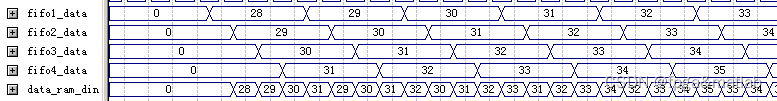

四个为FIFO的输出数据,最后面一个是送入双口RAM之前的数据,将思路数据合并为一路数据。

![]()

写入RAM的地址信号。

分别为示波器波形存储的读取地址信号,x,y就是从存储在外部的存储区的坐标位置,通过对不同坐标点的位置的读取,达到显示波形的效果。

5.参考文献

[1]初华, 万强, 曹海源,等. 基于DSP和FPGA的数字示波器设计[J]. 自动化仪表, 2013, 34(3):4.A35-12

2924

2924

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?