目录

1.同源时钟下的建立关系和保持关系

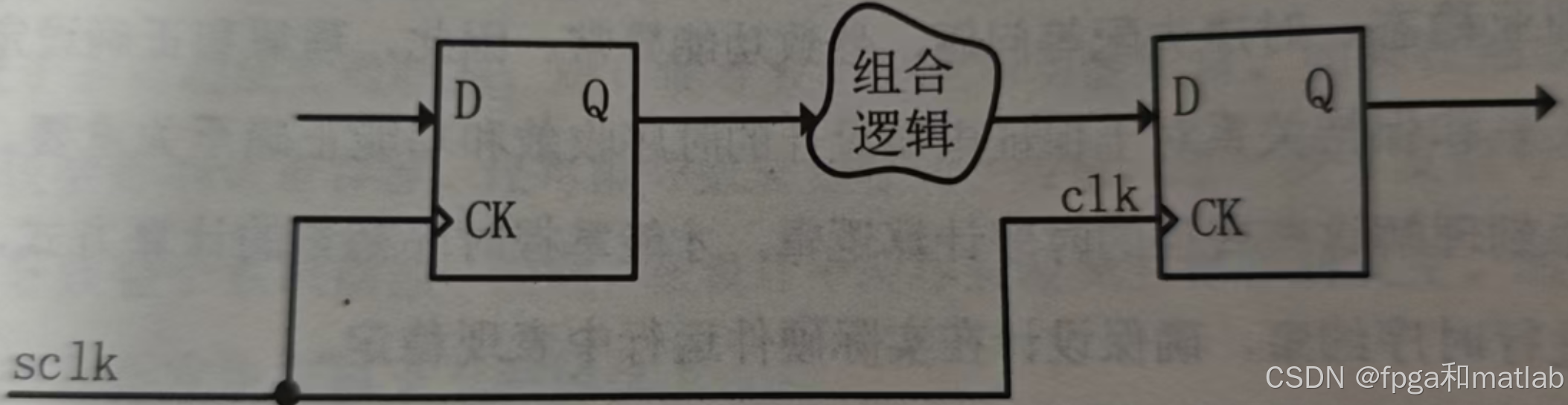

同源时钟指的是多个触发器或电路模块所使用的时钟信号来自同一个时钟源。如下图所示:

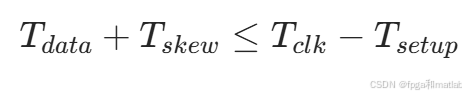

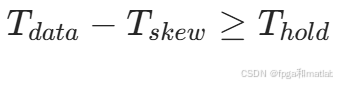

在同源时钟下,对于一个触发器,建立时间是指在时钟有效沿(上升沿或下降沿,取决于触发器触发方式)到来之前,数据必须提前稳定一段时间,以确保触发器能正确采样到稳定的数据。假设系统时钟周期为Tclk ,数据路径延时为Tdata ,时钟偏斜(同一个时钟信号到达不同触发器的时间差异)为Tskew ,建立时间要求为Tsetup 。为了满足建立时间要求,需要保证在时钟有效沿到达目标触发器之前,数据已经稳定,即:

由于时钟同源,各触发器的时钟信号具有相对稳定的相位关系,只要在设计中合理规划数据路径,使得数据传输延时在允许范围内,就比较容易满足建立时间要求。在同步电路设计中,通过布局布线工具对数据路径进行优化,减少信号传输延迟,从而满足建立时间的约束。

保持时间是指在时钟有效沿到来之后,数据必须在一段时间内保持稳定,防止触发器采样到错误数据。对于同源时钟下的触发器,保持时间要求为Thold ,需要保证在时钟有效沿之后,数据的变化不会影响到触发器的采样结果,即:

在同源时钟情况下,时钟偏斜相对可控,只要数据路径的延时足够长,满足保持时间的条件相对容易实现。设计时可以通过增加缓冲器等方式适当增加数据路径延时,以满足保持时间要求。

时序约束举例:

# 1. 定义同源时钟(来自同一时钟源)

create_clock -name CLK_SYS -period 10 [get_ports clk_in] ;# 10ns周期(100MHz)

create_clock -name CLK_DIV2 -period 20 [get_pins pll_div2] ;# 20ns周期(50MHz),与CLK_SYS同源

# 2. 建立时间约束(默认自动检查,可手动强化)

# 对关键路径设置更严格的建立时间要求

set setup_margin 0.5 ;# 额外增加0.5ns的建立时间裕量

set_max_delay [expr 10 - $setup_margin] \

-from [get_clocks CLK_SYS] \

-to [get_clocks CLK_SYS] \

[get_paths -of_objects [get_nets critical_data_net]]

# 3. 保持时间约束(默认自动检查,可手动调整)

# 对跨时钟域(但同源)路径设置保持时间裕量

set hold_margin 0.3 ;# 额外增加0.3ns的保持时间裕量

set_min_delay $hold_margin \

-from [get_clocks CLK_SYS] \

-to [get_clocks CLK_DIV2] \

[get_paths -of_objects [get_nets div2_data_net]]

# 4. 时钟不确定性设置(包含抖动等因素)

set_clock_uncertainty -setup 0.2 [get_clocks {CLK_SYS CLK_DIV2}] ;# 建立时间不确定性

set_clock_uncertainty -hold 0.1 [get_clocks {CLK_SYS CLK_DIV2}] ;# 保持时间不确定性

# 5. 时钟偏斜约束(控制同一时钟到达不同寄存器的延迟差)

set_clock_skew -setup 0.8 [get_clocks CLK_SYS]

set_clock_skew -hold 0.4 [get_clocks CLK_SYS]

2.非同源时钟下的建立关系和保持关系

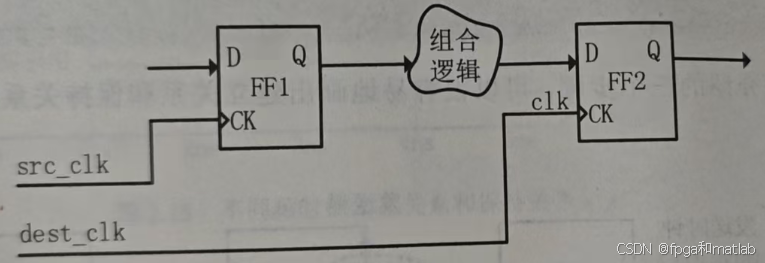

非同源时钟指的是不同触发器或电路模块所使用的时钟信号来自不同的时钟源,它们之间通常没有固定的相位关系和频率关系。如下图所示:

非同源时钟下,建立关系变得更加复杂。因为不同时钟之间没有固定的相位同步关系,当一个时钟域的数据要传输到另一个时钟域时,很难保证数据在目标时钟有效沿到来之前稳定。例如,在异步 FIFO(先进先出存储器)设计中,写时钟域的数据写入FIFO,然后在读时钟域读出。在数据从写时钟域传输到读时钟域时,需要考虑两个时钟的相对相位和频率差异,确保数据在目标时钟有效沿到来之前已经稳定在目标触发器的数据输入端。

为了满足建立时间要求,常采用异步信号同步化处理,如使用双触发器同步器(也叫打两拍同步器)。数据先进入第一个触发器,在目标时钟的作用下,经过一个时钟周期后,数据进入第二个触发器,此时数据已经在目标时钟域内同步,并且相对稳定,更容易满足建立时间要求。但这种方法会引入一定的延时。

在非同源时钟下,保持关系同样面临挑战。由于时钟的异步性,数据在传输过程中,很难保证在目标时钟有效沿之后保持稳定。例如,当读时钟域从 FIFO 中读取数据时,需要确保数据在被读取后,在当前时钟周期内不会因为写时钟域的操作而发生变化。

通常需要对数据传输路径进行特殊设计,如在异步 FIFO 中,通过设计合理的空满标志逻辑,保证在读时钟域读取数据时,写时钟域不会对该数据进行修改,从而满足保持时间要求。此外,还可以通过增加数据保持电路等方式来确保数据在目标时钟域内满足保持时间的要求。

时序约束举例:

# 1. 定义非同源时钟(来自不同时钟源)

create_clock -name CLK_A -period 8 [get_ports clk_a_in] ;# 8ns周期(125MHz)

create_clock -name CLK_B -period 12 [get_ports clk_b_in] ;# 12ns周期(83.3MHz),与CLK_A非同源

# 2. 标记异步关系(关键!告知工具时钟无相位关联)

set_clock_groups -asynchronous \

-group [get_clocks CLK_A] \

-group [get_clocks CLK_B]

# 3. 跨异步时钟域路径的建立时间约束

# 方法1:使用最大延迟约束(适用于简单异步路径)

set_max_delay 7 -from [get_clocks CLK_A] -to [get_clocks CLK_B] [get_nets async_data]

# 方法2:使用伪路径(适用于已通过同步器处理的路径)

set_false_path -from [get_clocks CLK_A] -to [get_clocks CLK_B] [get_nets sync_data_out]

# 4. 跨异步时钟域路径的保持时间约束

# 对未使用同步器的异步路径设置最小延迟

set_min_delay 1 -from [get_clocks CLK_A] -to [get_clocks CLK_B] [get_nets async_data]

# 5. 同步器路径特殊约束(确保同步器可靠工作)

# 对打两拍同步器的第一级触发器设置保持时间裕量

set_min_delay 0.5 \

-from [get_clocks CLK_A] \

-to [get_clocks CLK_B] \

[get_pins sync_ff1/D]

# 6. 时钟不确定性(非同源时钟通常设置更大的裕量)

set_clock_uncertainty -setup 0.5 [get_clocks CLK_A]

set_clock_uncertainty -setup 0.6 [get_clocks CLK_B]

set_clock_uncertainty -hold 0.2 [get_clocks {CLK_A CLK_B}]

1987

1987

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?