显示器产品辐射发射(RE102)问题整改案例与关键技术仿真分析-深圳市赛盛技术有限公司

全方位全流程电磁兼容工程技术服务与解决方案提供商

首页 ꄲ 显示器产品辐射发射(RE102)问题整改案例与关键技术仿真分析

显示器产品辐射发射(RE102)问题整改案例与关键技术仿真分析

一、 现象描述

1. 产品信息

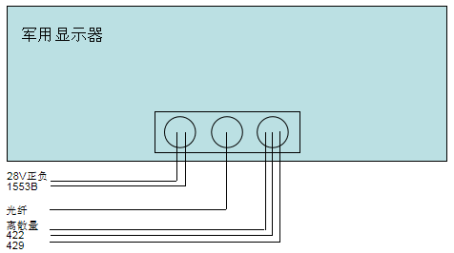

某显示器产品,输入电压:28VDC;对外接口:28VDC,1553B,光纤,离散量,RS422,RS429等。

表 1 供电特性

| 额定电压 | 电压范围 | 最大电流 | 备注 |

| 28VDC | NA | 15A |

表 2 接口特性

| 接口名称 | 工作电压 | 接口类型 | 电缆类型 | 备注 |

| 28VDC | 28VDC | 连接器 | 非屏蔽线 | 共用连接器 |

| 1553B | NA | 连接器 | 屏蔽线 | |

| 光纤 | NA | 连接器 | 非屏蔽线 | 共用连接器 |

| 离散量 | NA | 连接器 | 屏蔽线 | 共用连接器 |

| RS422 | NA | 连接器 | 屏蔽线 | |

| RS429 | NA | 连接器 | 屏蔽线 |

图 1 显示器接口示意图

2. 试验要求

试验标准:GJB 151B-2013

试验要求:电源线为非屏蔽线,信号线为屏蔽线

表 3 试验标准

| 测试项目 | 测试标准 | 测试规格 | 测试方法 |

| RE102 | GJB 151B-2013 | 2-10 MHz 34dBuV/m 10-100 MHz 24dBuV/m 100-1000 MHz 24~44dBuV/m 1-18 GHz 54-79dBuV/m | 拉杆天线 双锥天线V/H 对数天线V/H 喇叭天线V/H |

3. 问题描述

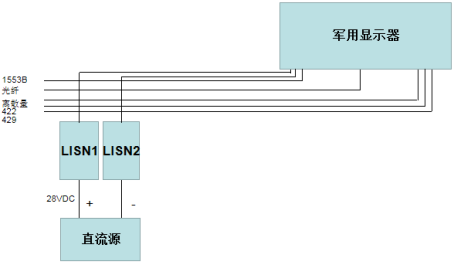

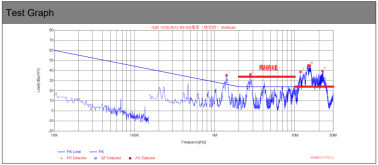

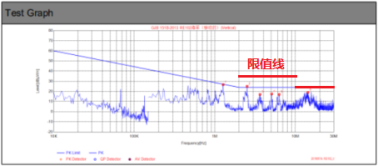

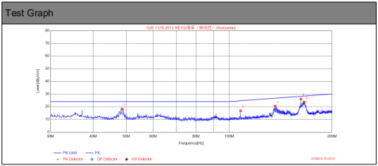

显示器产品依据GJB 151B-2013标准测试RE102辐射发射项目,测试结果FAIL,测试布置及数据如下图所示。

图 2 测试布置图

表 4 原始测试数据

| 序号 | 测试频段 | 测试曲线 |

| 1 | 拉杆天线 2-30 MHz |

|

| 2 | 双锥天线 V/H 30-200 MHz |

|

| 3 | 对数天线 V/H 200-1000 MHz |

|

二、 原因分析

1. RE102辐射问题分析

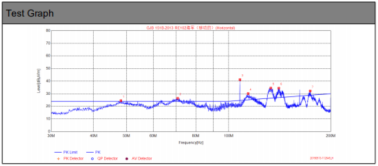

RE102辐射超标问题主要有:低频段11-22 MHz包络、高频段54MHz倍频毛刺,详细情况如下表:

表 5 RE102超标问题分析列表

| 序号 | 问题描述 | 频点特征 | 干扰分析 | 下一步动作 |

| 1 | 拉杆天线: 11-22 MHz 包络超标,14.81MHz超标21.18dB | 宽带 包络 | 包络可能由电源噪声通过线缆耦合辐射发射 | 排查关键频段干扰由哪根线缆耦合,关键干扰源由哪部分电路产生 |

| 2 | 双锥天线: 108MHz超标20.07dB | 窄带 毛刺 | 108MHz、270MHz、324MHz均为54MHz倍频,推测尖峰由时钟信号透过结构缝隙泄露 | 排查PCB与54MHz频率相关时钟走线 |

| 3 | 对数天线: 270MHz超标9.45dB,324MHz超标7.27dB |

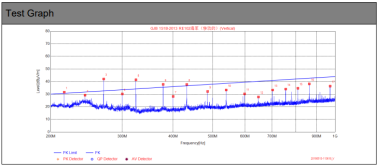

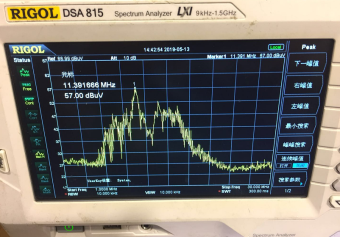

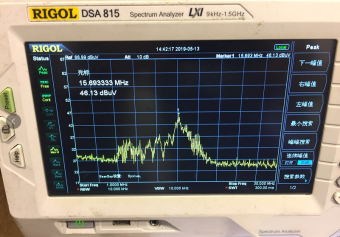

采用频谱仪进行初步定位分析,寻找辐射天线与辐射路径,对每根线缆进行测试,包括电源线和信号线,不包括光纤线缆,情况如下:

表 6 频谱仪定位数据

| 序号 | 卡环卡线位置 | 测试数据 |

| 1 | 端口1线缆(28V正负、1553B) |

|

| 2 | 端口2线缆(光纤) 注:正常情况下,光纤线缆无辐射问题,卡环测试有噪声,主要原因:卡环靠近连接器端口,噪声通过端口泄露,磁力线穿过卡环导致 |

|

| 2 | 端口3线缆(离散量、422、429) |

|

l 初步测试定位结论:

① 拉杆天线11-22MHz包络是由电源线缆和离散量线缆辐射;

② 双锥天线108MHz是通过屏缝隙泄露,显示屏右下角、左下角缝隙泄露值最大;168.6MHz包络是由离散量线缆辐射。

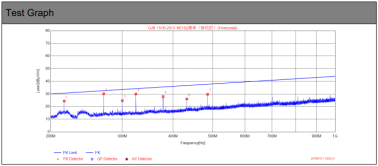

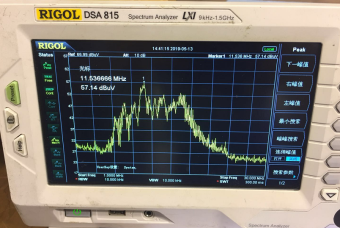

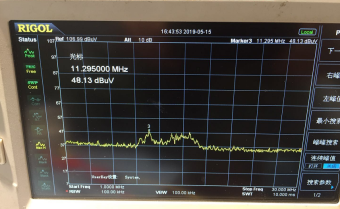

根据之前测试定位结论,对PCB板电源电路等进行逐个排查,寻找辐射超标问题点的噪声源头,情况如下:

表 7 测试定位过程数据

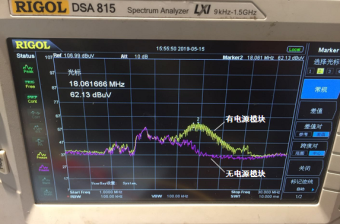

| 序号 | 定位措施 | 测试波形 |

| 1 | 断开28V转28V电源模块,使用跳线短接,18MHz附近包络下降明显 |

|

| 2 | 在28V正负分别对PGND跨102 Y电容,11.295MHz附近包络整体下降14dB |

|

l 最终测试定位结论:

① 14.81MHz包络超标主要是由28V转28V电源模块导致;

② 54MHz倍频毛刺由显示屏泄露,将显示屏面调转方向,高频毛刺下降明显;详细检查原理图和PCB设计,发现DVI时钟电路晶振频率为27MHz,PCB表层存在至少4000mil长距离走线。

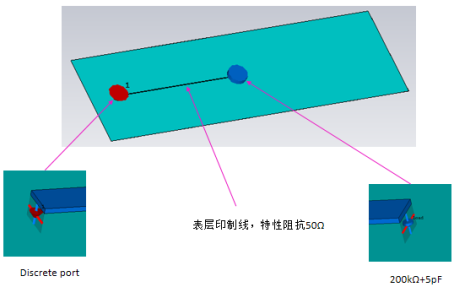

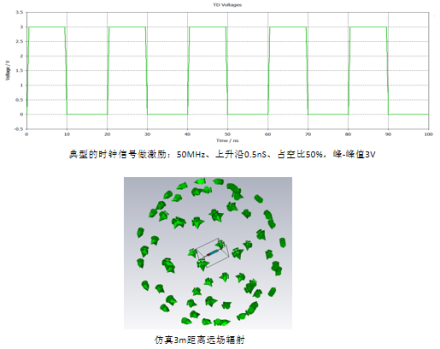

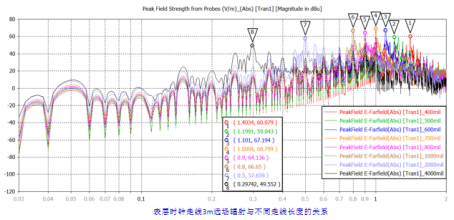

2. 时钟表层走线长度对EMI的影响仿真分析

由上面的分析可知,窄带噪声主要是由于PCB上的时钟电路、时钟信号导致,因此对PCB板的时钟走线的EMI影响进行仿真分析,主要结论如下:

表 8 时钟表层走线长度对EMI的影响分析

| 1 | 仿真模型 |

|

| 2 | 仿真设置 |

|

| 3 | 仿真结果 |

|

| 4 | 分析结论 | 1) 随着时钟线表层走线长度的减小,3m远场辐射最大点向高频移动; 2) 当表面走线长度为700mil时,最大谐振点在1GHz,当表层走线长度为700mil及以上时,最大辐射点均移到1GHz以上,而1GHz以上EMI限值不以准峰值而为限值(注:通信产品,1GHz以下以准峰值为限值;军工产品,1GHz以下以峰值为限值;表层走线仿真更多是说明EMI规律),而以平均值为限值更容易通过,故表面时钟走线长度应≤700mil,但600mil时最大辐射超过60dBuV/m,而500mil时辐射峰值低于60dBuV/m ,因此表面时钟走线长度应≤500mil。 |

3. 总结:

1) 毛刺:

DVI时钟电路信号PCB表层走线,显示屏与箱体结构件搭接处有缝隙,导致高频噪声泄露。

2) 包络:

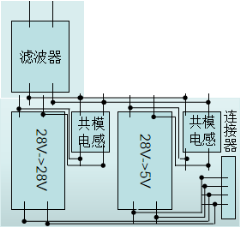

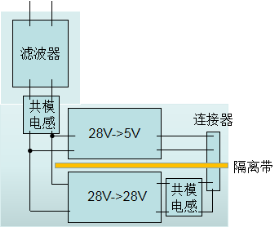

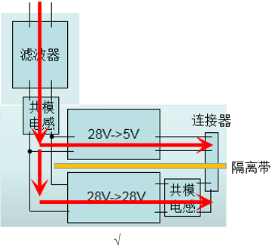

① 原理图设计不合理:经判断28V->28V电源模块干扰较大,28V->28V输出端口应增加共模电感滤波;28V->28V,28V->5V两电源模块输入端口并行有共模电感滤波,可删掉1个,输入端口可共用1个共模电感滤波;

② 布局设计不合理:输入共模电感前后存在交叉干扰;28V->28V,28V->5V两电源模块输出存在交叉干扰;

③ 布线设计不合理:电源噪声通过完整地平面耦合到对外端口线缆,导致辐射超标。

三、 措施与方案

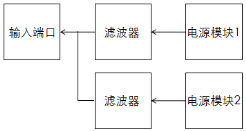

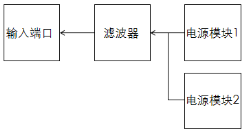

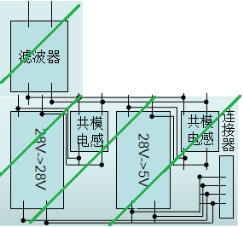

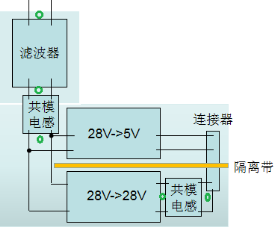

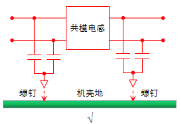

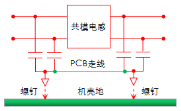

1. 两电源模块并行输入共模电感合二为一(28V->28V,28V->5V两电源模块输入端口取电位置相同,从EMC角度看,合二 为一对滤波电路插损不影响,同时节省空间有利于单板布局布线优化),在28V->28V电源模块输出增加共模电感滤波(测试定位发现28V->28V电源模块干扰很大,28V->28V为外购电源模块);

表 9 两种原理框图对比

| 原理框图 |

|

|

| 假设 | 电源模块1裸噪声为A,电源模块2裸噪声为B,滤波器插损为C; | |

| 输入端口噪声 | 电源模块1传导到输入端口噪声为A-C,电源模块2传导到输入端口噪声为B-C,最终两者取最大值; | 电源模块1和电源模块2噪声取最大值A或B,传导到输入端口噪声为A-C或B-C,两者取最大值; |

| 总结 | 最终对EMC有决定性影响的是输入端口噪声,两种电路框图,从EMC角度看,效果是一样的。 | |

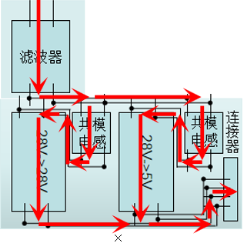

2. 调整电源板两电源模块布局,使整个大电流走势最顺,输入输出不相互交叉;

表 10 电源板布局示意图

| 优化前电源板布局 | 优化后电源板布局 |

|

|

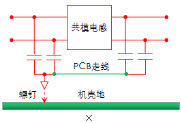

3. 取消地平面铺铜,滤波器、共模电感前后Y电容在单板上分地处理,分别通过螺钉锁至机壳地;

表 11 电源板铺地&接地处理示意图

| 优化前铺地处理 | 优化后接地处理 |

ü 整个单板全铺地; |

ü 去掉整个单板铺地; ü 共模电感、滤波器前后Y电容在单板上不建立连接关系,分别通过螺钉锁至机壳地; ü 调整PCB布局,使滤波前后不相互交叉,电源模块输入输出不相互交叉,两电源模块之间不相互交叉。 |

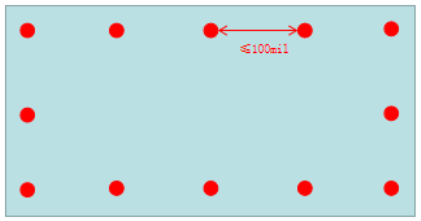

4. 将母板第二层和倒数第二层设置完整地平面,将时钟信号CLK和高速信号线打过孔移至PCB内层,在地平面边沿每隔100mil打地过孔对内部高速信号和铭感信号进行屏蔽。

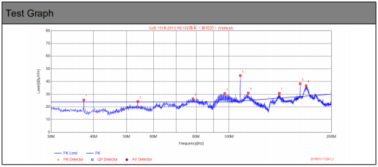

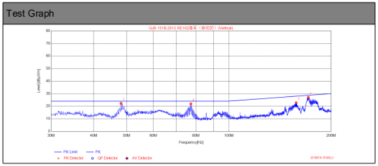

四、 试验结果

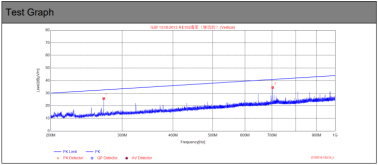

试验结果PASS,测试数据如下图。

表 12 优化后测试数据

| 序号 | 测试频段 | 测试数据 |

| 1 | 拉杆天线 2-30 MHz |

|

| 2 | 双锥天线V/H 30-200 MHz |

|

| 3 | 对数天线V/H 200-1000 MHz |

注:对数天线水平测试PASS,后面没有进行补充验证测试 |

五、 经验分享

1. 电源板铺地不同于信号板,地平面&接地处理,共模电感下方应掏空处理,共模电感前后Y电容在单板上分地处理,在单板上不建立连接关系,分别通过螺钉就近锁至机壳地;

表 13 Y电容分地处理示意图

| 推荐 | 不建议 | 禁止 |

|

|

|

2. 电源板布局应使大电流回路最顺,电源模块输入输出不相互交叉,电源模块之间不相互交叉,滤波电路前后不相互交叉并尽量远离;

表 14 大电流回路示意图

| 推荐 | 禁止 |

|

|

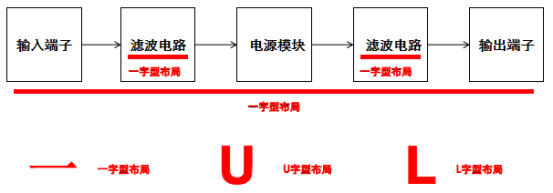

3. 输入端子->滤波电路->电源模块->滤波电路->输出端子,应呈一字型布局;

图 3 滤波电路一字型布局示意图

4. 时钟电路信号、高速信号严禁在PCB表层长距离走线,单板应在第二层和倒数第二层设置完整地平面,地平面边沿每隔100mil打地过孔,对时钟信号、高速信号、敏感信号进行屏蔽处理。

图 4 板边地过孔间距示意图

本文详述了一个显示器产品在遵循GJB 151B-2013标准进行辐射发射(RE102)测试时遇到的问题及整改过程。通过对电源线和信号线的测试定位,发现超标问题源于电源模块和时钟电路设计。通过改进电源模块布局、滤波电路设计和PCB布线,成功降低了辐射,试验结果达到标准。

本文详述了一个显示器产品在遵循GJB 151B-2013标准进行辐射发射(RE102)测试时遇到的问题及整改过程。通过对电源线和信号线的测试定位,发现超标问题源于电源模块和时钟电路设计。通过改进电源模块布局、滤波电路设计和PCB布线,成功降低了辐射,试验结果达到标准。

7365

7365

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?