文章目录

本篇博客是根据verdi ug介绍nwave nshema部分,是自己的verdi ug的理解以及亲自实际验证操作。

作者:ciscomonkey 未经允许不得转载抄袭!

1、Change the Schematic View Among Instances

Tools -> preference

verdi提供了三种schema的配色方案,并且还可以自定义。

- Classic Theme

- Black Theme

- White Theme

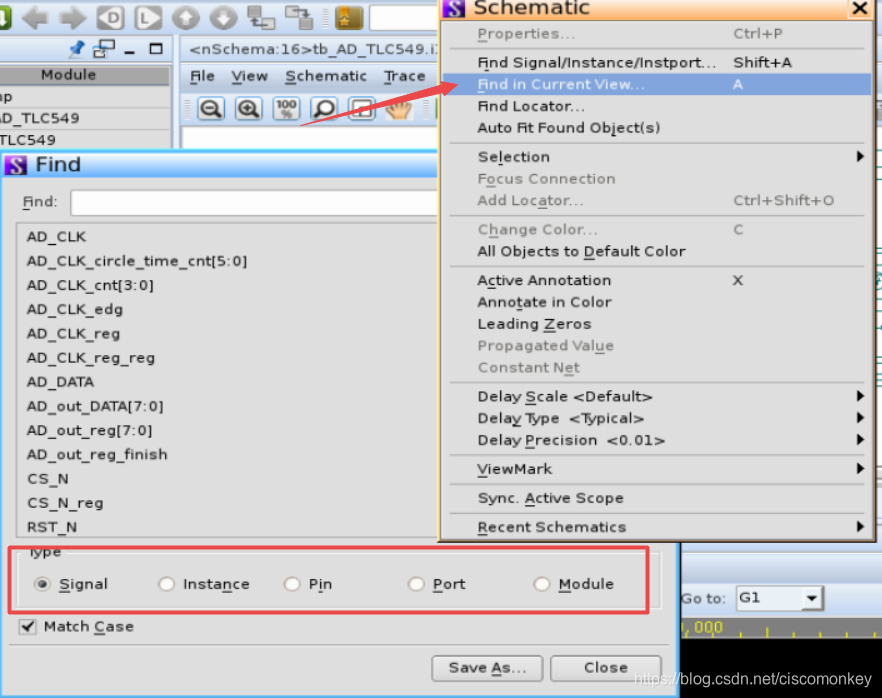

2、Find an Instance/Signal and Manipulate it

what’s the difference Signal betweent Instance?

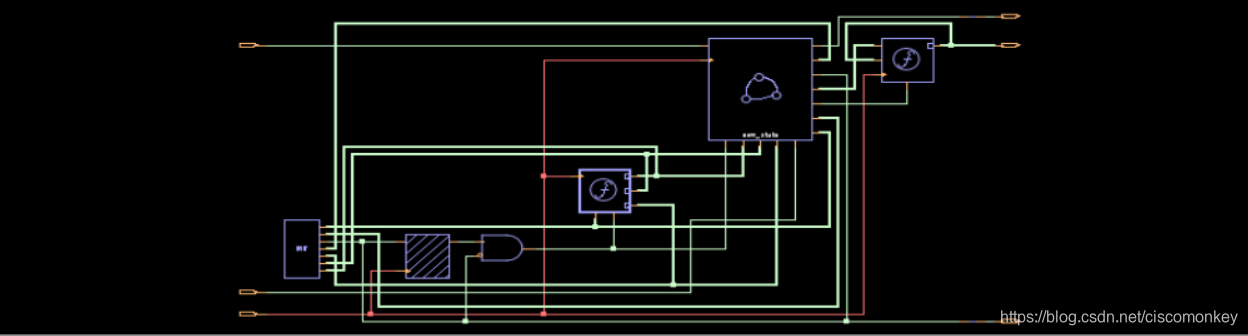

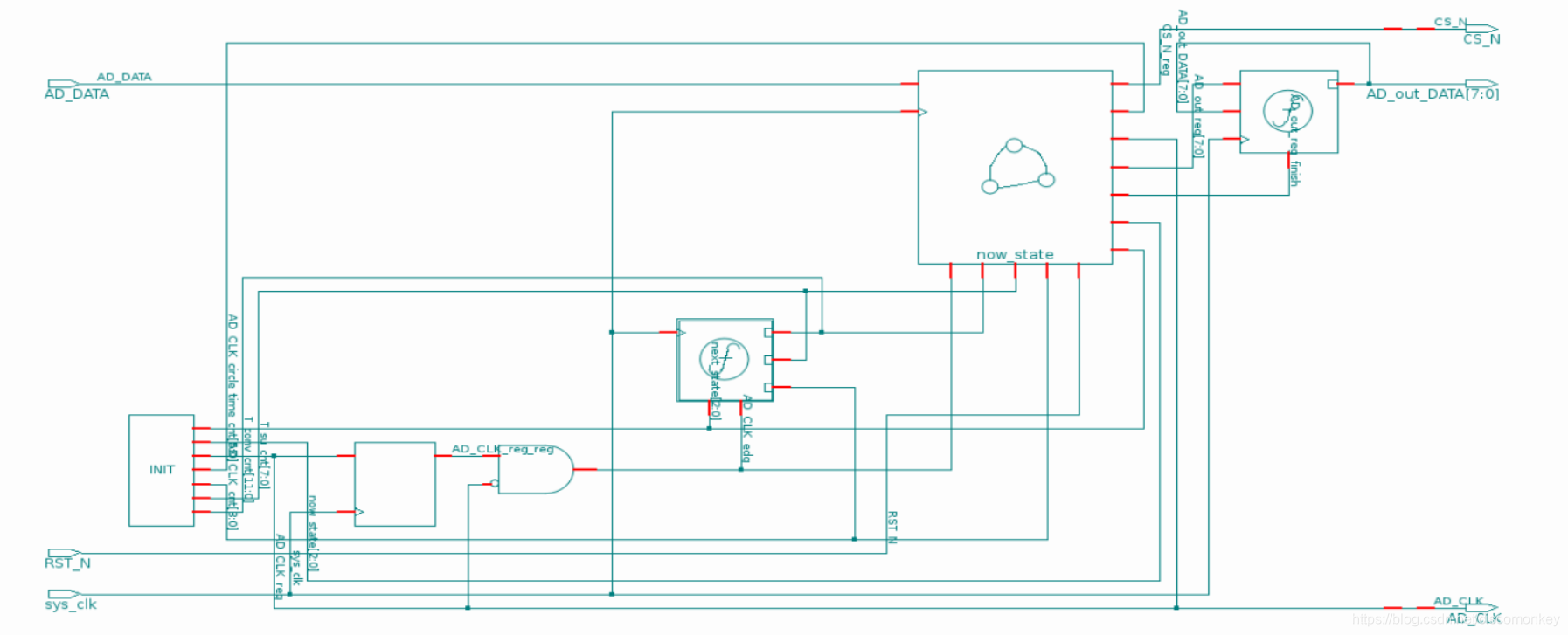

这一点,我们可以来看一下schematic。

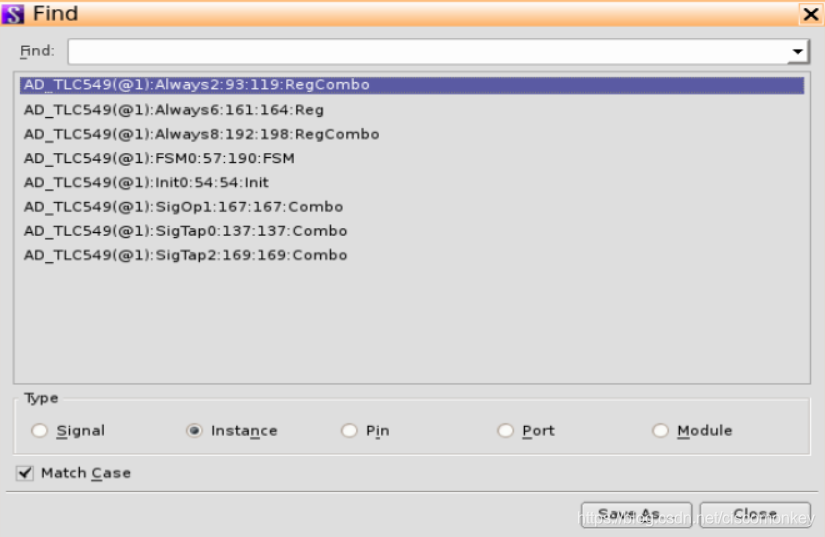

当我列出所有的Instance来查看。

如下图所示,所有的Instance如下:

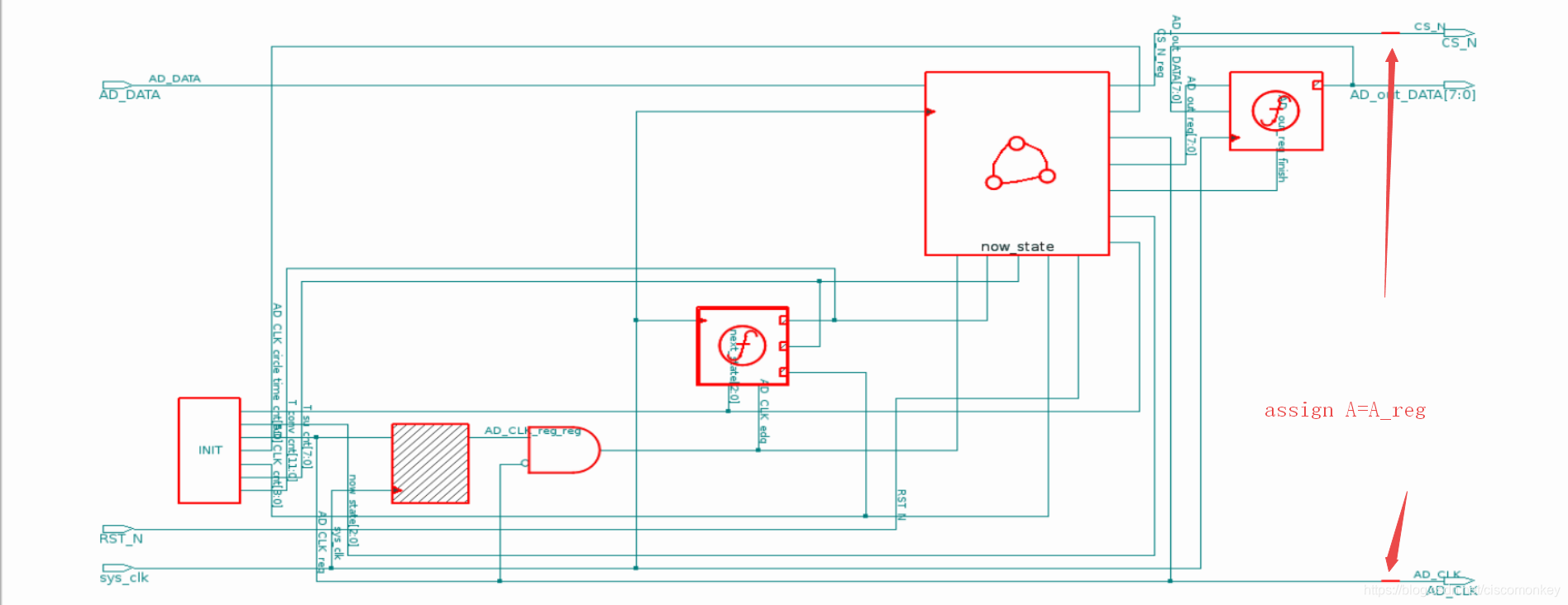

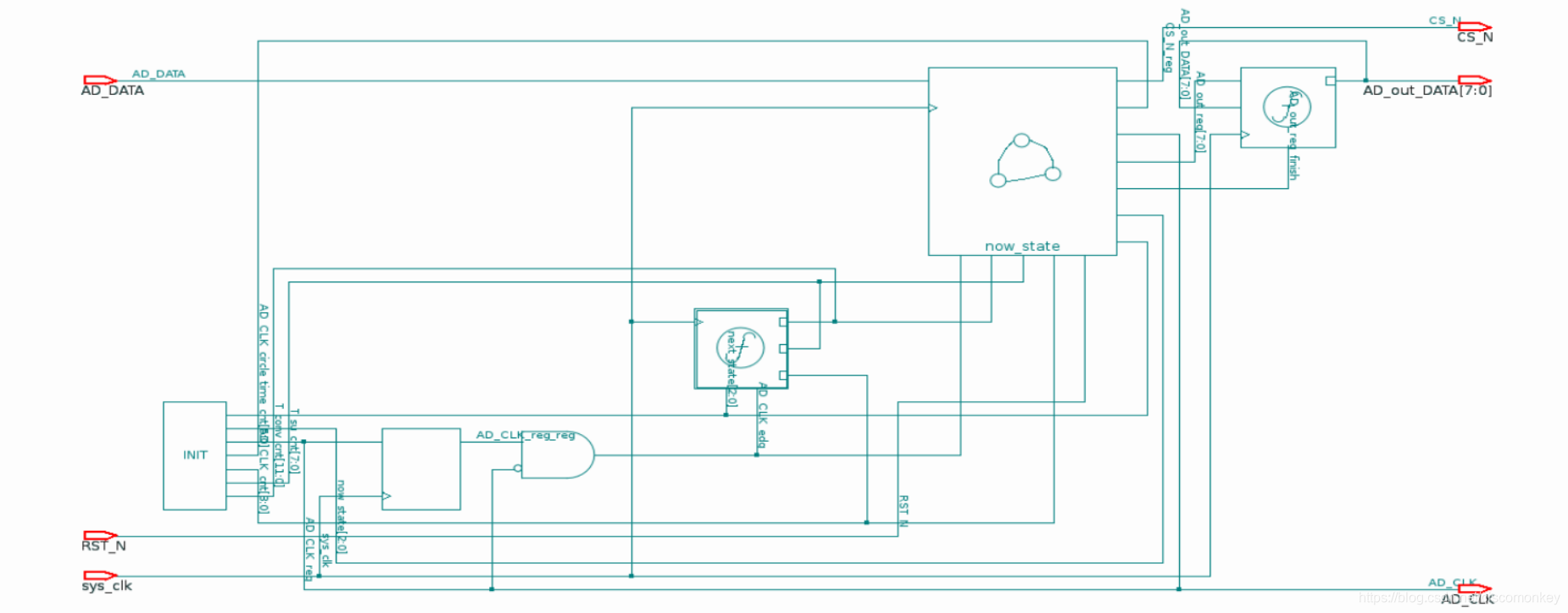

值得注意的是红色箭头的地方,我的Verilog语法是assign A=A_reg

这种也被视作Instance,也就是说这种也相当于一个I/O直接相连的空盒,同样为Instance。

现在,我列出所有的Signal:

可以看到所有的Signal都为instance的I/O

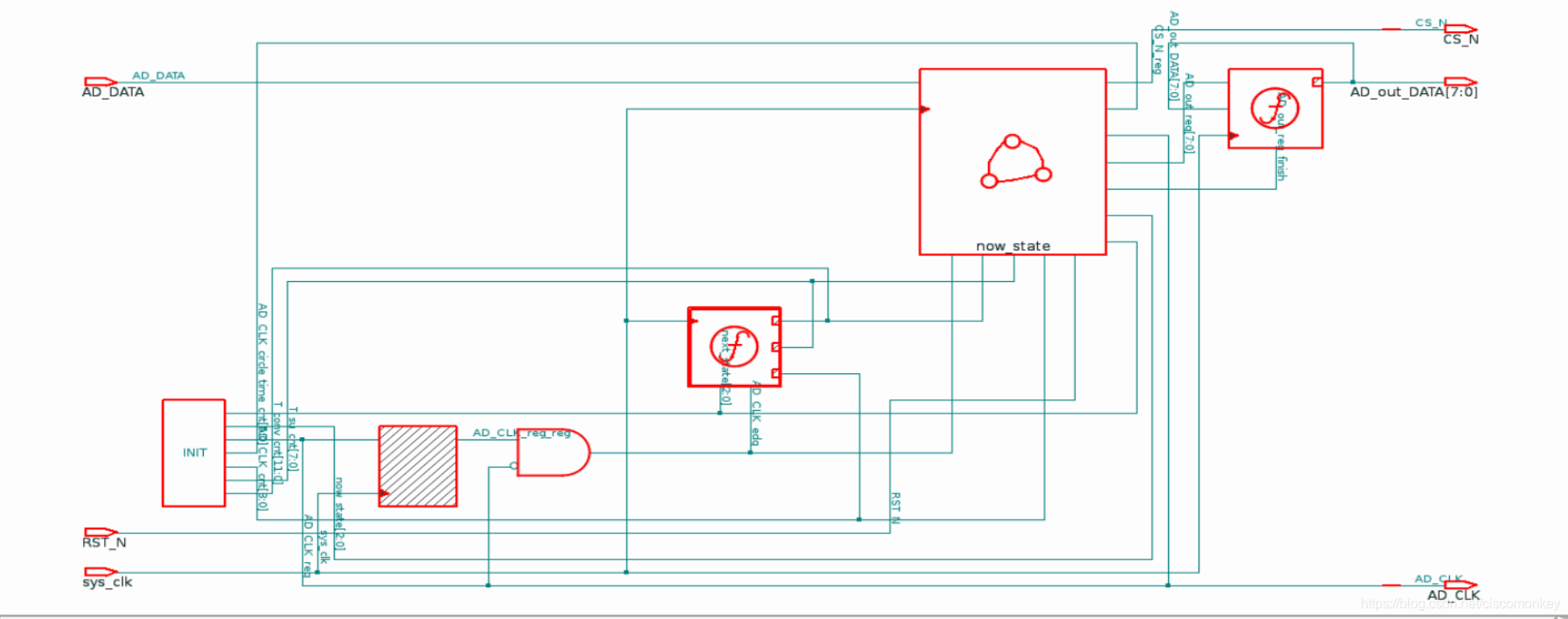

下面是所有Pin:

下面是所有的port:

下面是所有的module:

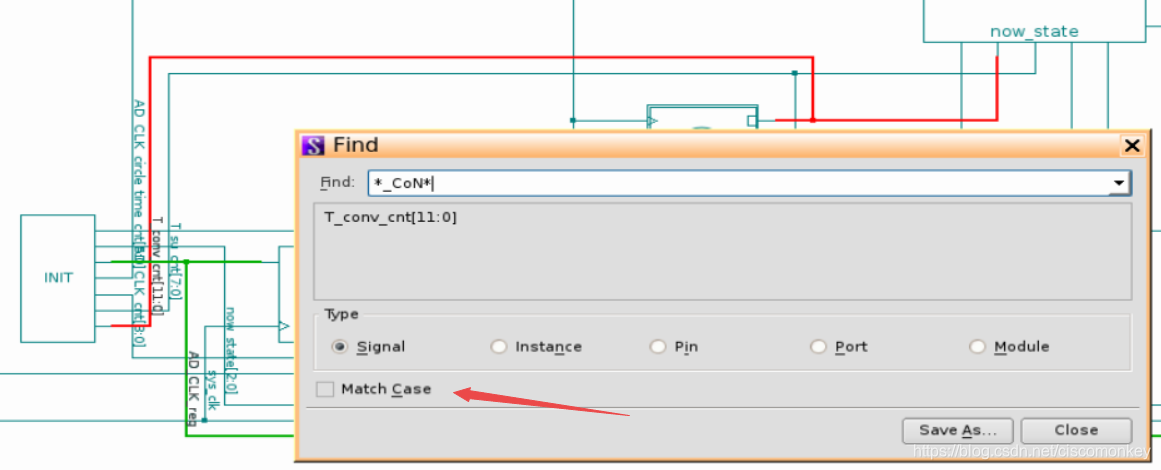

如下图所示,不要勾选Match Case后, 支持*匹配,无关大小写

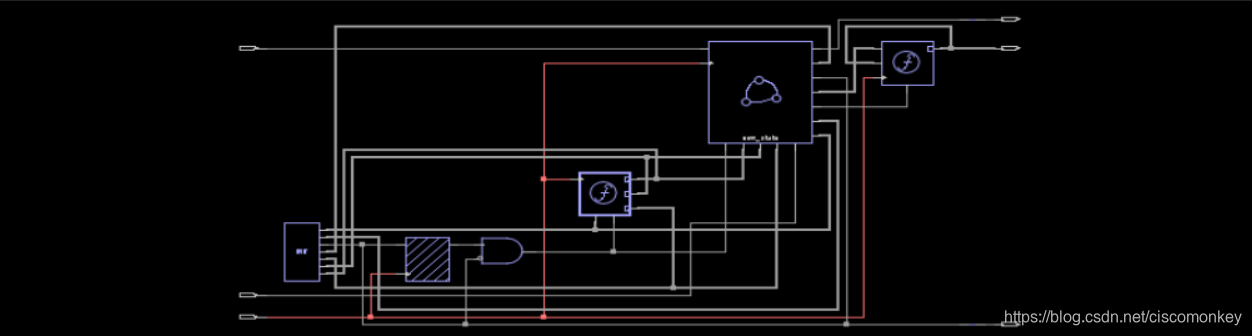

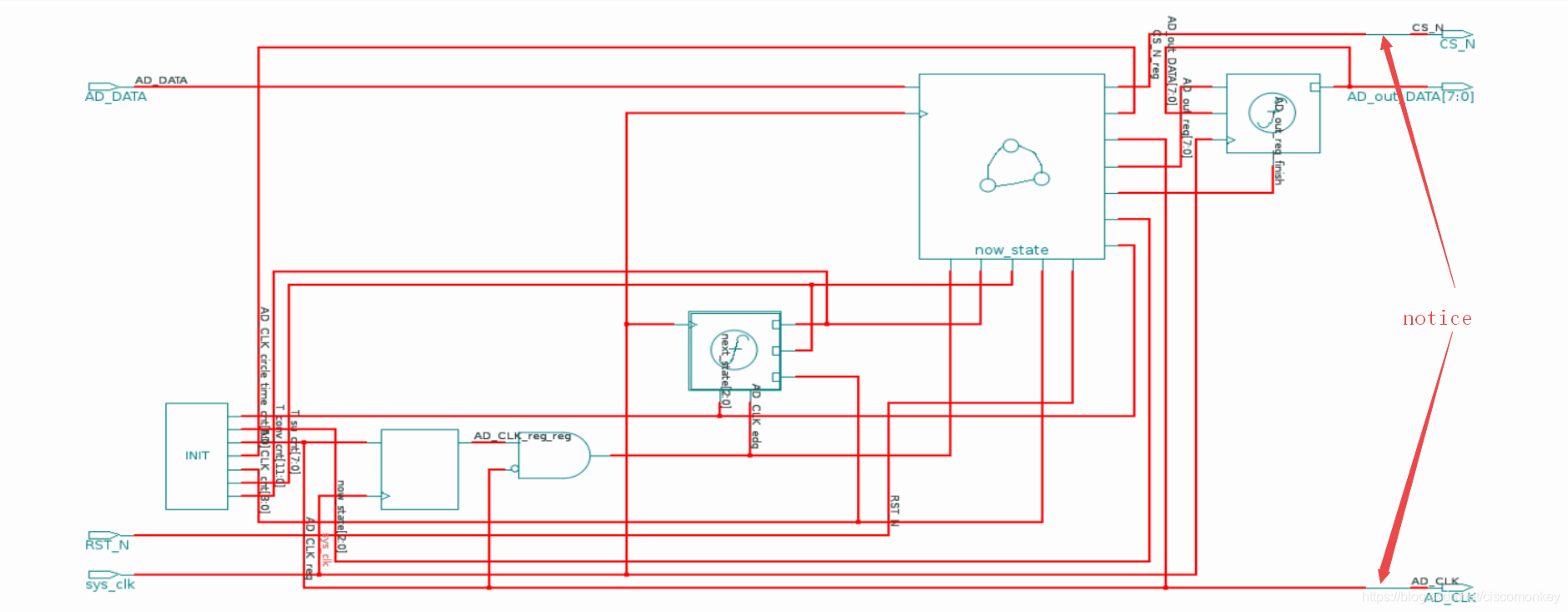

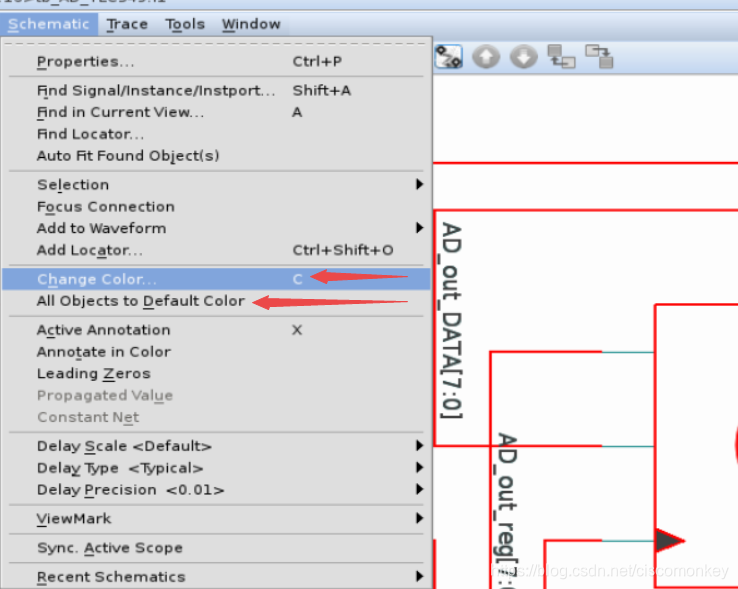

如何改变signal的颜色,很多时候我们可能会需要使用这个功能来trace信号。

如下图所示:

schematic -> Change Color

可以改变对象的颜色

schematic -> All Objects to Default Color

所有的对象恢复到默认颜色

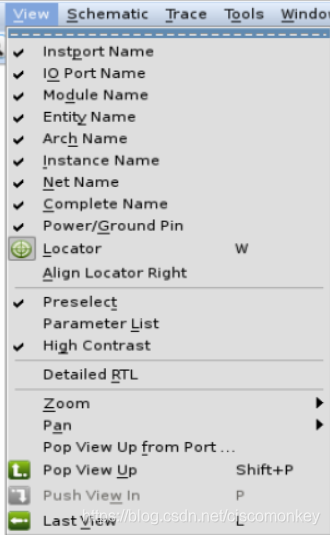

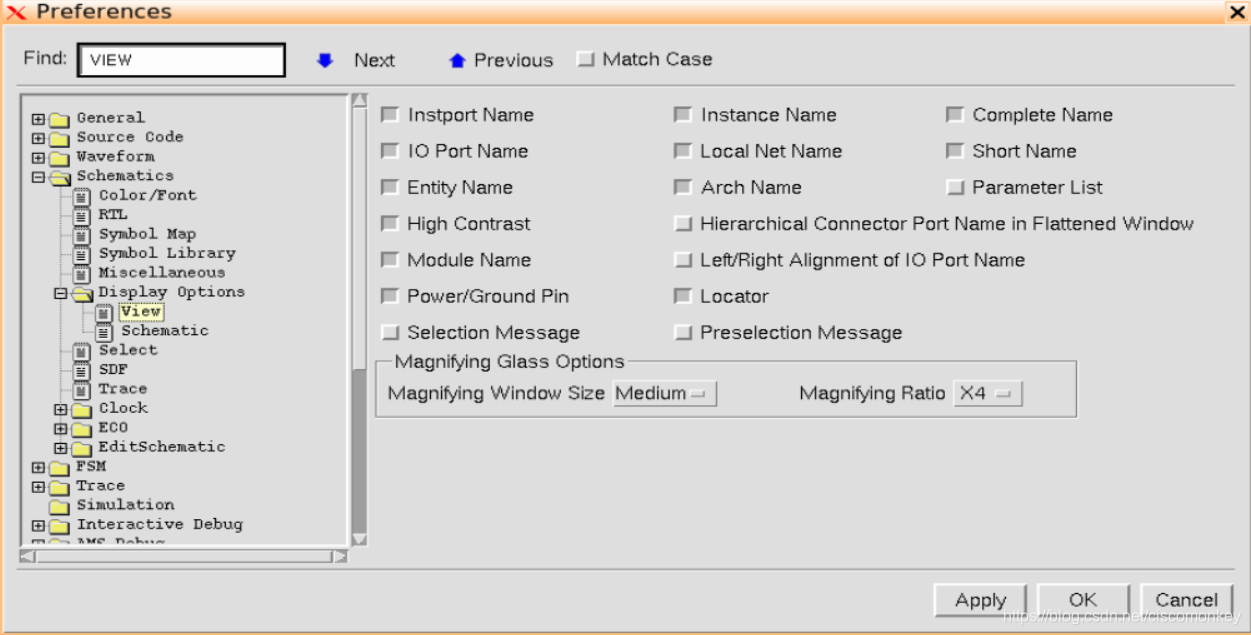

由于我们很多时候在View schematic的时候,打开一次就要点一次view -> hign contrast 以及IO Port Name等操作,非常麻烦,这里建议在preferences中输入view,修改设置view相关的默认参数即可。

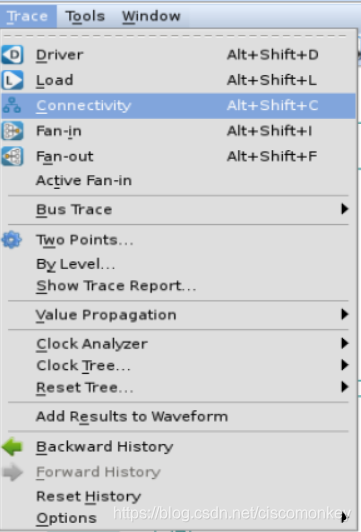

2、Trance Signal

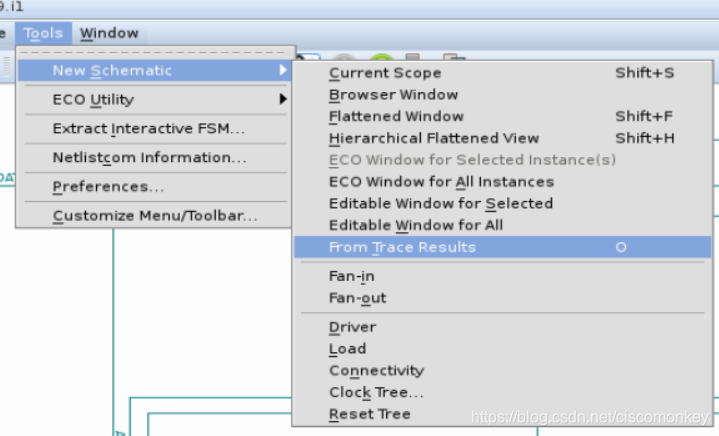

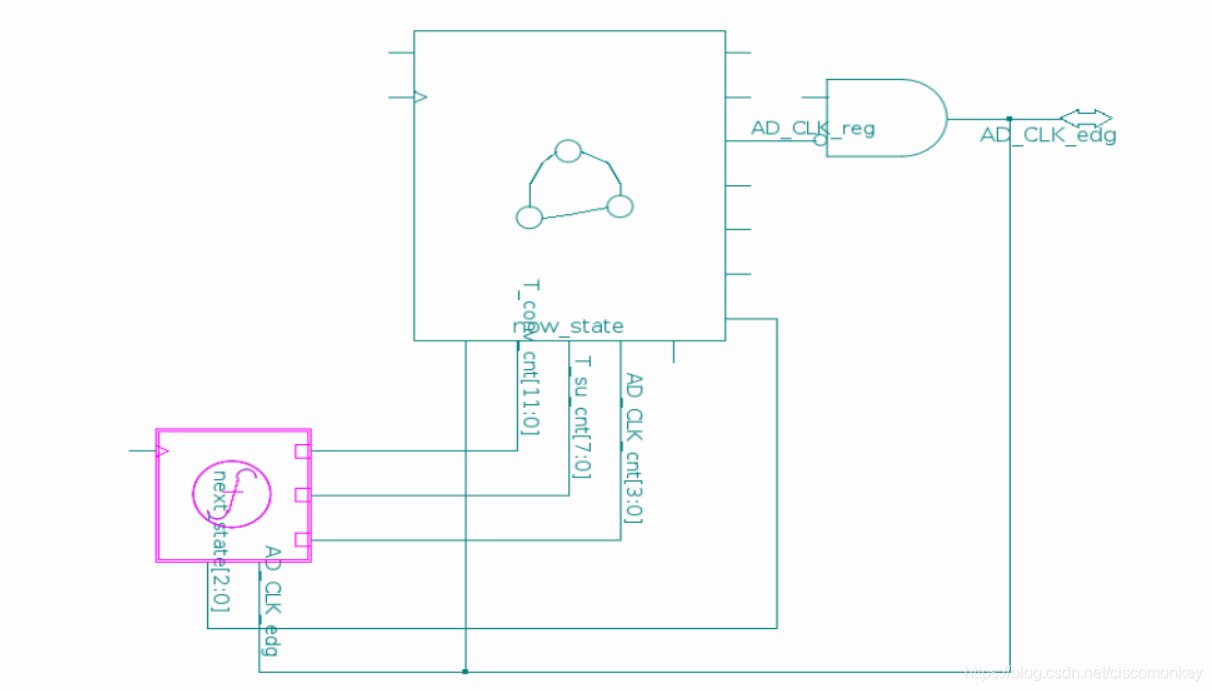

2.1 Find the Connectivity of a Signal and Generate a New Schematic from Trace Results

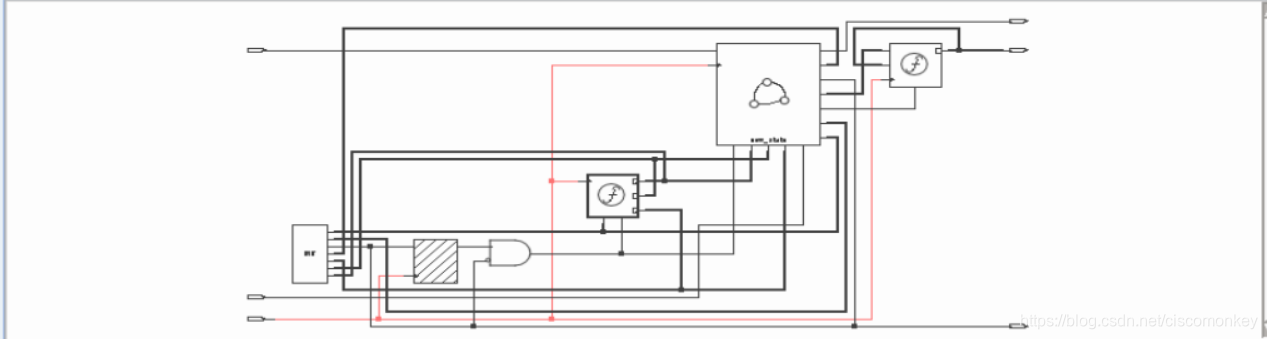

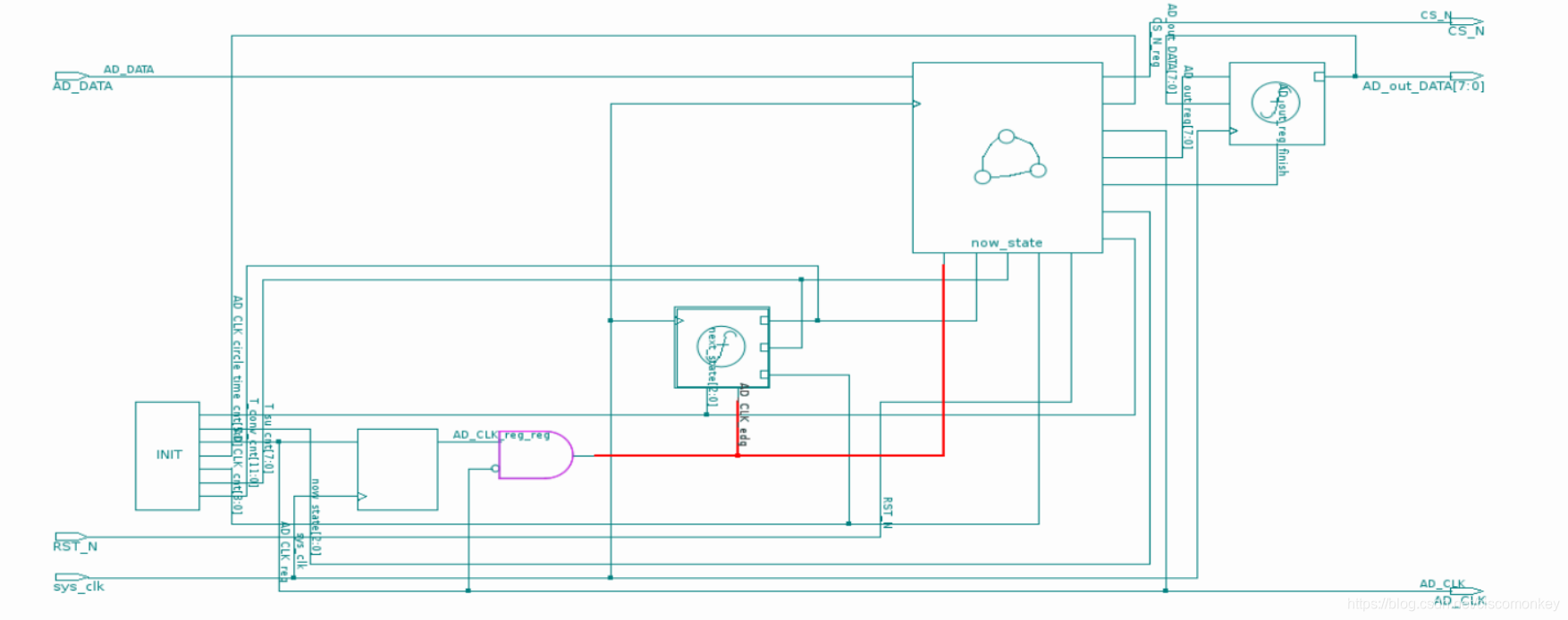

如下图所示,trace这条wire上的drive,为一个与门。

然后选择

Trace -> Connectivity ,

最后选择

Tool ->New Schematic -> From Trace Results

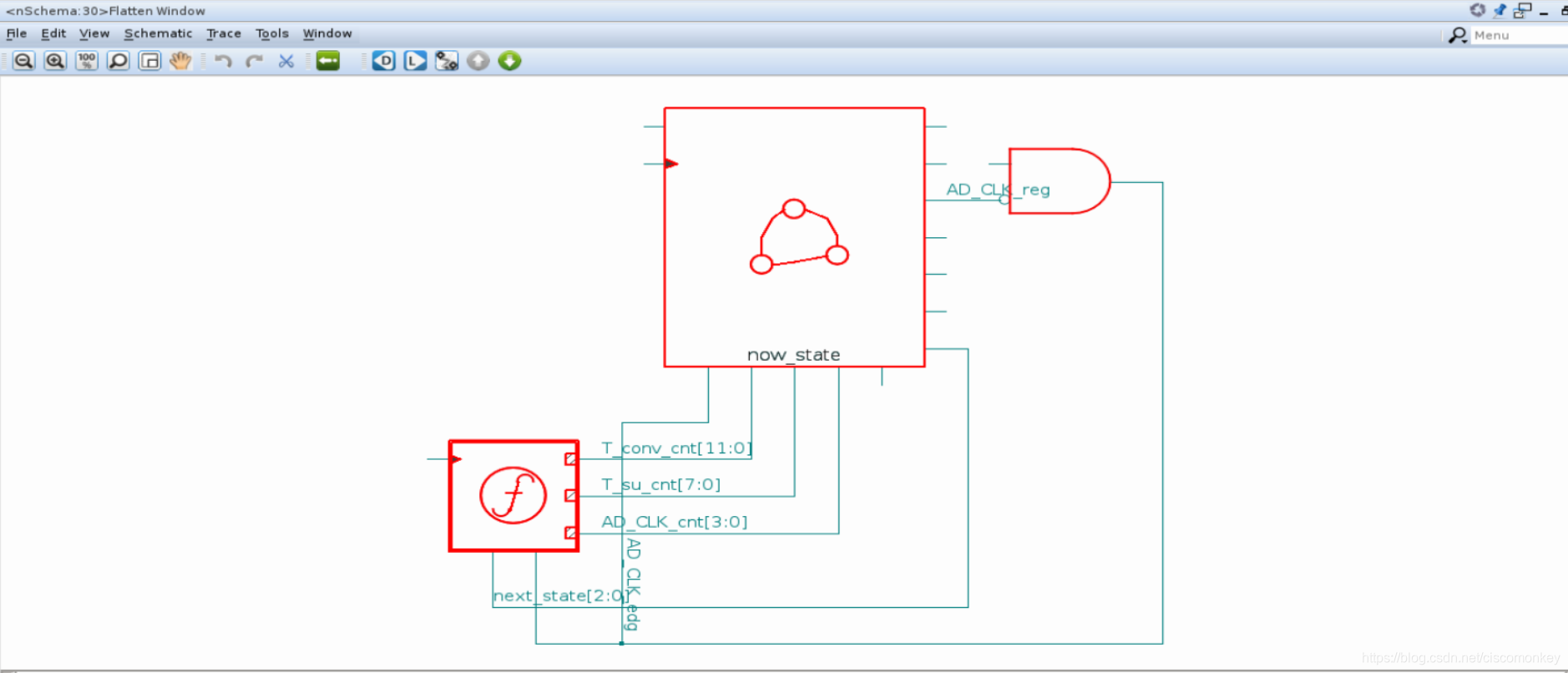

如下图所示,将会生成新的原理图

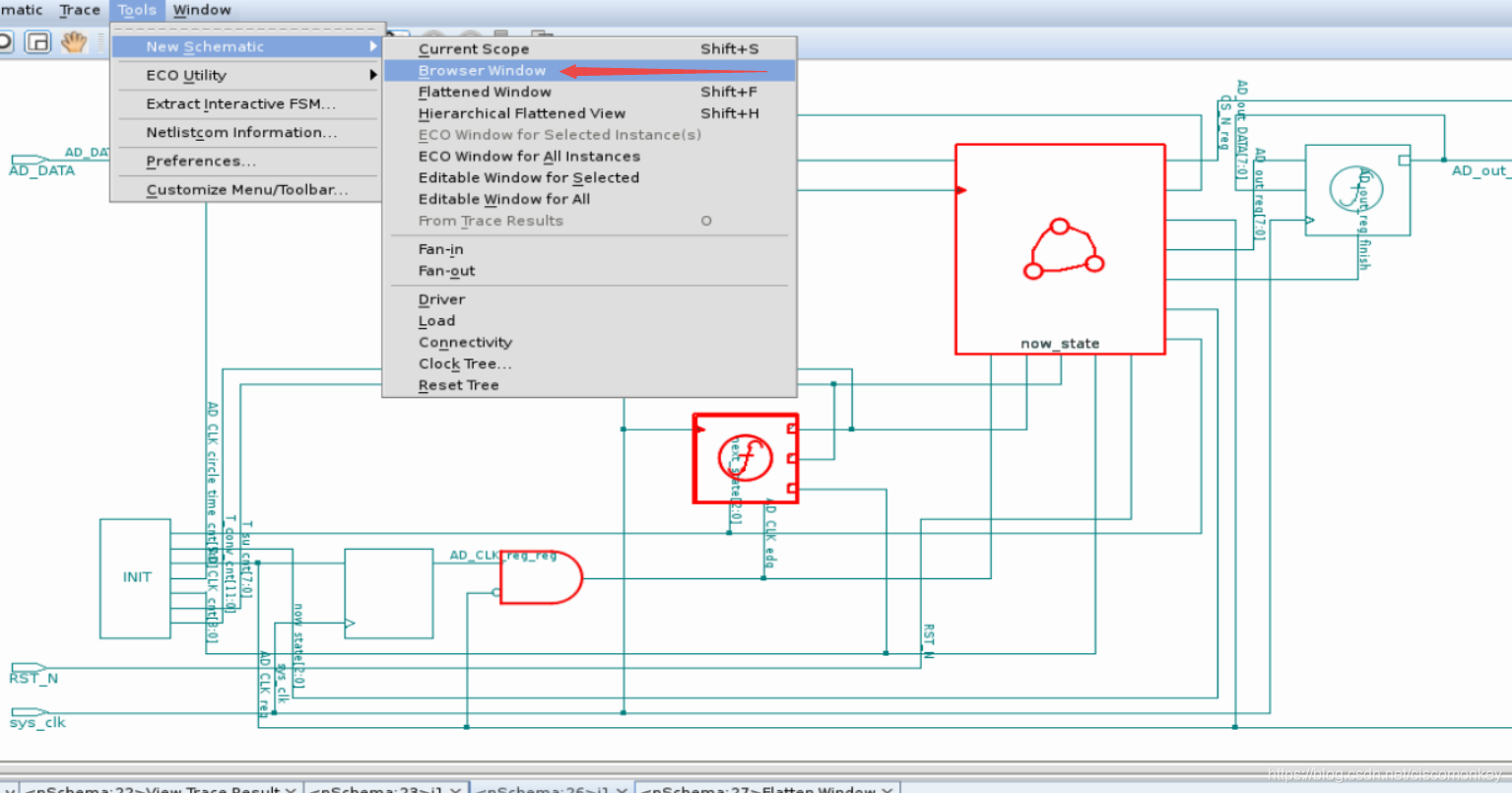

3、Generate Partial Schematics

3.1 Browser Window

有时候,由于电路的复杂性,我只想关心勾选的那些block,所以,我可以选定那些我勾选的block,按住shift键即可连续选择,然后

New Schematic ->Browser Window

即可开启一张新的schematic

3.2 Flatten Window(略)

788

788

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?