DONE信号的作用

• 是FPGA完成配置和初始化后的关键状态指示信号。

• 当FPGA成功加载配置数据并通过校验后,DONE信号拉高,标志FPGA进入正常工作模式。

FPGA配置的三个阶段

-

复位阶段

• 上电后,若nCONFIG引脚被拉低,DONE信号保持低电平,所有I/O处于高阻态。 -

配置数据加载阶段

• 数据从外部Flash或JTAG接口加载,通过CRC校验后,DONE信号从低电平变为高阻态,需通过外部上拉电阻拉高,标志配置完成。 -

初始化阶段

• DONE信号拉高后,FPGA初始化内部逻辑和I/O寄存器,完成后进入用户模式。

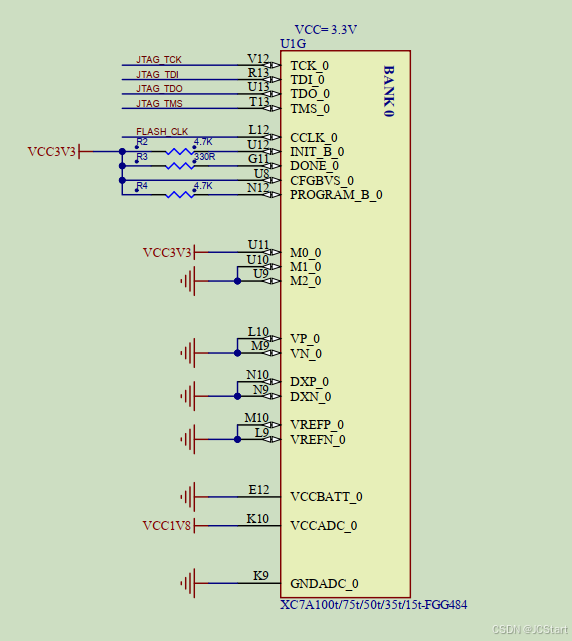

上拉电阻设计要点

• Xilinx FPGA:

• 推荐使用330Ω上拉电阻(非传统4.7kΩ)。

• 失效案例:若使用4.7kΩ电阻,在高速配置时钟下,DONE信号上升时间不足,可能导致GTS事件失败(I/O无法及时使能)。

关键设计总结

- DONE信号需外部上拉,阻值需根据FPGA厂商要求选择(如Xilinx的330Ω)。

- 避免因阻值过大导致信号上升时间过长,引发初始化异常或I/O使能失败。

- Altera的

CONF_DONE与Xilinx的DONE功能一致,需遵循类似设计规则。

参考设计

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?