一,FPGA配置引脚说明

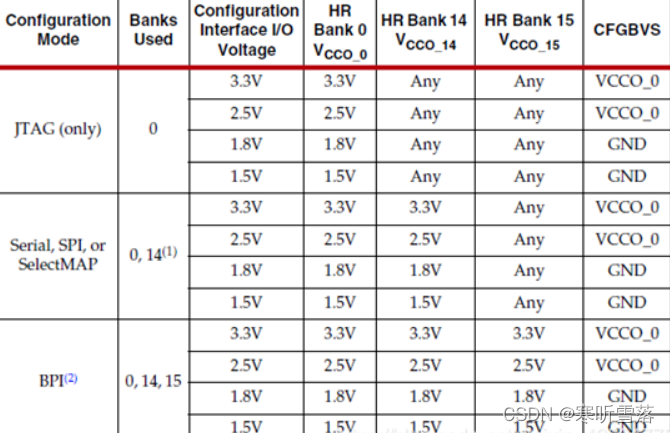

1,配置相关电源

如果VCCO0连接至2.5V或3.3V,CFGBVS连接至VCCO0。

如果VCCO0连接至1.5V或1.8V,CFGBVS连接至GND。

建议bank0、bank14、bank15的VCCO电压一致,避免出现I/O Transition at the End of Startup

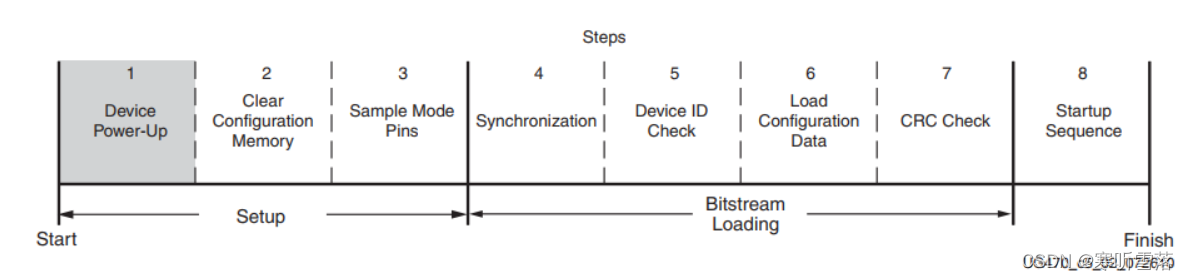

2,配置流程

二,FPGA开启启动加载的方式

二,FPGA开启启动加载的方式

1,上电自动加载:就是在FPGA完成上电初始化完成后,由FPGA主导从外部存储器读取位流,此时CCLK为输出;或者由其它主控制器来主导从外部存储器读取位流到FPGA中,此时CCLK为输入,从而完成上电自动加载。

本文详细介绍了ZYNQ FPGA配置加载流程,包括电源设置、启动方式等,并分析了加载失败的原因,如电源顺序、PUDC_B状态、配置状态管脚拉低等问题,提供了解决方案。

本文详细介绍了ZYNQ FPGA配置加载流程,包括电源设置、启动方式等,并分析了加载失败的原因,如电源顺序、PUDC_B状态、配置状态管脚拉低等问题,提供了解决方案。

订阅专栏 解锁全文

订阅专栏 解锁全文

3966

3966

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?