目录

1.AC/DC介绍及区别

70年代到1995年这段时间里,由于芯片的工作频率很低只有20-100M,scan测试只有DC SCAN,我们就能捕捉到所有std-logic的制造缺陷。但是1995年以后,测试科学家和工程师发现通过DC SCAN测试没有缺陷的芯片在高工作频率下使用会有问题。其根本原因是随着制造工艺向深亚微米迈进,芯片的工作频率也提高到200M-1G,原来的SCAN测试方法和模型不再能捕捉到所有的std-logic的制造缺陷。

下表给出了AC/DC测试的一些区别:

上面一段介绍摘自:

2.DC/AC mode

DC/AC的划分是根据输入激励的相对快慢来确定的。

DC (static)testing:测试激励比正常工作要慢很多的时钟(不仅仅包含stuck-at scan test)

AC testing (At-speed testing):测试激励使用正常时钟(不仅仅包含At-speed scan test)

DC/AC分类来自Digital systems testing and testable design ---Miron Abramovici

我们所说的DC testing 就是static testing或slow testing即慢速测试,测试频率是10M-30M ,在SCAN测试方法中就是DC scan test或normal scan test。

AC testing也就是at-speed testing (可能有称为fast test)即实速测试,测试频率与芯片真实工作频率是一样的。在scan测试中就是AC scan test或at-speed scan test。

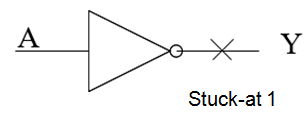

(a).DC scan

低速DC scan对Stuck-at缺陷有很好的覆盖率,所以也有称呼为stuck-at mode,主要检查我们平时常见的stuck-at 0/1错误。比如下图中的 inverter A端如果被接到了VSS端的话,就是一个stuck at 1的fault。

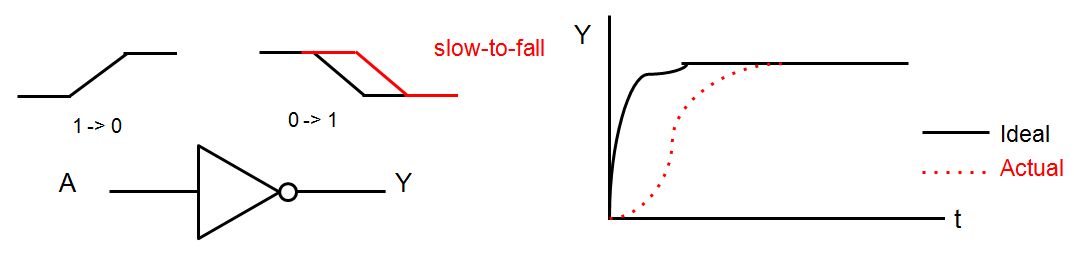

(b).AC scan

AC scan也被称为At-speed scan Test(ASST),是一种高速测试模式,主要测试芯片中的延迟故障,也就是transition。随着半导体制造工艺的不断发展,片上器件的几何尺寸越来越小。此时,由于制造工艺异常,材料纯度不够,环境杂质等因素影响所造成的随机缺陷,导致电路中某些信号transition time变长,如果这种变化造成关键路径上的延迟不满足最大延迟要求,那么整个电路就不能工作在正常频率下。我们称这种故障为延迟故障。如下图的inverter,如果它下降的transition time延迟,就会导致它整个propagation delay超出理想限定的范围。

现在高性能超大规模的芯片的故障也越来越多地表现为延迟故障,而不是传统的stuck-at 故障。因此这个ASST模式也是很重要的,通常会单独作为一个模式定义在mcmm环境中。

本文介绍了DC/AC测试在集成电路中的应用。DC SCAN测试主要用于检测stuck-at缺陷,适用于低频场景,而AC SCAN测试(At-speed testing)则针对高频下的延迟故障,确保芯片在实际工作速度下的可靠性。随着工艺发展,延迟故障变得更为重要,AC SCAN测试成为不可或缺的测试模式。

本文介绍了DC/AC测试在集成电路中的应用。DC SCAN测试主要用于检测stuck-at缺陷,适用于低频场景,而AC SCAN测试(At-speed testing)则针对高频下的延迟故障,确保芯片在实际工作速度下的可靠性。随着工艺发展,延迟故障变得更为重要,AC SCAN测试成为不可或缺的测试模式。

http://www.elecfans.com/dianyuan/570646.html

http://www.elecfans.com/dianyuan/570646.html

1313

1313

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?