sram除了setup/hold的检查,还需要进行min_period的检查。这个min_period是sram里给bitline进行预充电留足时间。如果两次读间隔period太近,那么第二次读就不能正确读出。

minPeriod是sram的bitCell器件预充电时间决定的,和clk的transition也有一定的关系。如下图:clk的transition影响较小。

SRAM中min_period的由来

摘自:

STA:SRAM中min_period的由来-腾讯云开发者社区-腾讯云

min_pulse_width

首先,min_pulse_width, 是检查时序逻辑中clock信号的高电平与低电平的宽度是否超过了规定的最窄宽度。

对于这个check,是不能够忽略的。理论上必须fix。但是由于在signoff是会加一些derating,uncertainty, 以及各种corner,因为存在一定的margin,所以,如果有违例,但是芯片回来却没有问题,也不必惊讶,那是因为这些违例尚在margin的覆盖范围之内。

强烈建议不要带着mpw违例进行signoff,而如果必须如此,需谨慎评估风险。

min_period

既然有了min_pulse_width, 为什么对于sram,还有个min_period的check?

这个要从sram的原理说起。

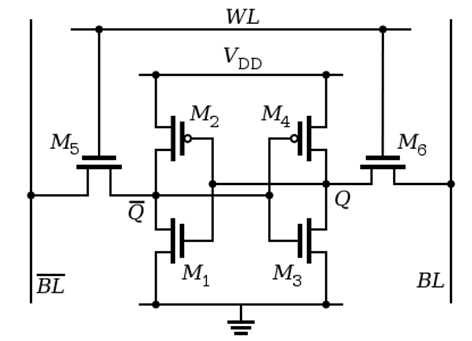

六管sram bitcell

对于一个常见的六管sram为例。

那么,对于这个bitcell的读取过程如下:

假定存储的内容为1, 即在Q处的电平为高. 读周期之初,两根位线预充值为逻辑1, 随后字线WL充高电平,使得两个访问控制晶体管M5与M6通路。第二步是保存在Q的值传递给位线BL在它预充的电位,而泻掉(BL非)预充的值,这是通过M1与M5的通路直接连到低电平使其值为逻辑0 (即Q的高电平使得晶体管M1通路). 在位线BL一侧,晶体管M4与M6通路,把位线连接到VDD所代表的逻辑1 (M4作为P沟道场效应管,由于栅极加了(Q非)的低电平而M4通路). 如果存储的内容为0, 相反的电路状态将会使(BL非)为1而BL为0. 只需要(BL非)与BL有一个很小的电位差,读取的放大电路将会辨识出哪根位线是1哪根是0. 敏感度越高,读取速度越快。

简单来说,SRAM在读取之前需要对BL BLB进行预充电(precharge), 然后打开WL,然后BL,BLB才是被送入sense amp进行比较。

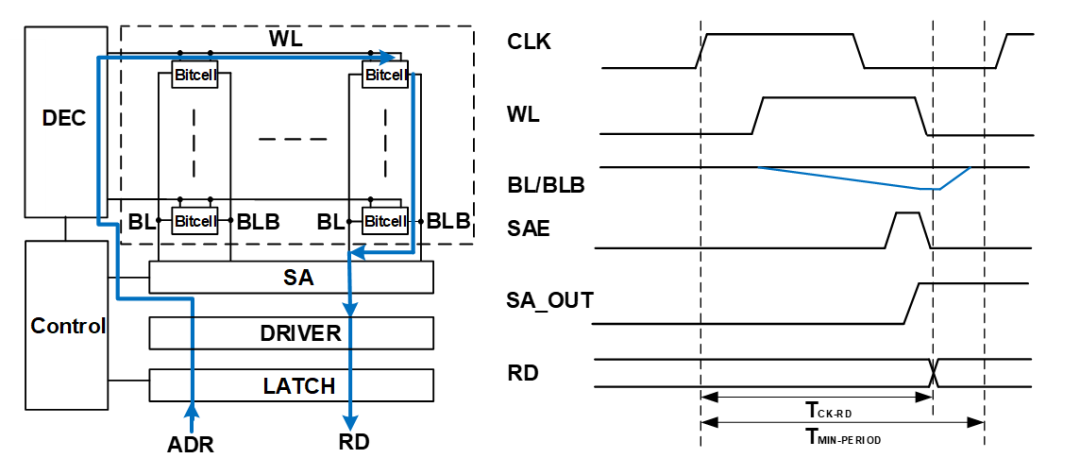

再来看时序图。

时序图

当sram读取之后,BL/BLB需要再次重新进行预充电,以便进行下一次读取。

那么这个min period,就是SRAM本身的delay(CLK->RD)再加上BL/BLB预充电的时间。

因此回到最初的问题。

为什么sram有个min_period的check。

答案是为了给sram的bitline进行预充电留足时间。

鸣谢

感谢群中好友 陈锋, Antenna的解答。

附件

SRAM的操作

SRAM的基本单元有3种状态:standby (电路处于空闲), reading (读)与writing (修改内容). SRAM的读或写模式必须分别具有"readability"(可读)与"write stability"(写稳定).

Standby

如果字线(Word Line)没有被选为高电平, 那么作为控制用的M5与M6两个晶体管处于断路,把基本单元与位线隔离。

由M1 – M4组成的两个反相器继续保持其状态,只要保持与高、低电平的连接。

Reading

假定存储的内容为1, 即在Q处的电平为高. 读周期之初,两根位线预充值为逻辑1, 随后字线WL充高电平,使得两个访问控制晶体管M5与M6通路。

第二步是保存在Q的值传递给位线BL在它预充的电位,而泻掉(BL非)预充的值,这是通过M1与M5的通路直接连到低电平使其值为逻辑0 (即Q的高电平使得晶体管M1通路).

在位线BL一侧,晶体管M4与M6通路,把位线连接到VDD所代表的逻辑1 (M4作为P沟道场效应管,由于栅极加了(Q非)的低电平而M4通路).

如果存储的内容为0, 相反的电路状态将会使(BL非)为1而BL为0.

只需要(BL非)与BL有一个很小的电位差,读取的放大电路将会辨识出哪根位线是1哪根是0.

敏感度越高,读取速度越快。

Writing

写周期之初,把要写入的状态加载到位线。

如果要写入0,则设置(BL非)为1且BL为0。

随后字线WL加载为高电平,位线的状态被载入SRAM的基本单元。

这是通过位线输入驱动(的晶体管)被设计为比基本单元(的晶体管)更为强壮,使得位线状态可以覆盖基本单元交叉耦合的反相器的以前的状态!

clock min period check

摘自:

论STA | clock min period check-腾讯云开发者社区-腾讯云

有时候,问题的来去也会扎堆,周二跟某几位小朋友讨论过clock min period check, 今天又跟某小猪讨论了一遍。

按照惯例从lib 说起,通常RAM 的lib 里都会定义min_period 的timing check, 至于为什么RAM 需要check min_period 而其他时序逻辑不需要,驴还没搞清楚,请教各位予以指导。

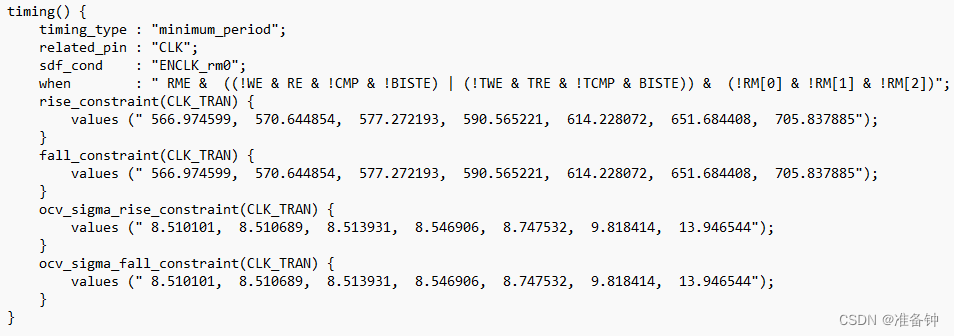

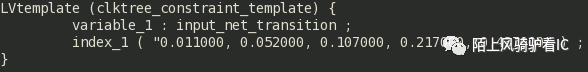

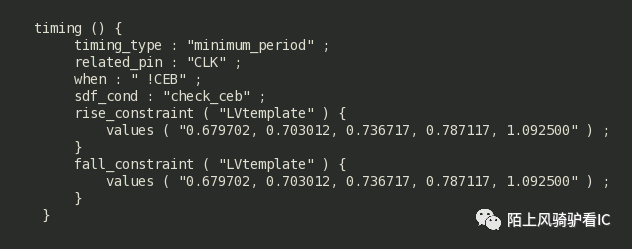

老工艺,min_period 在RAM 的lib 里是一个定值;新工艺,min_period 在RAM 的lib 里定义为index 是CLK pin transition 的一张一维表,在lib 里会先定义一个如下图所示的Lookup table , index_1 里列出的值是CLK pin 的transition 值。

在CLK pin 上会定义如下的minimum_period 的timing check. Values 的值即为对应transition 所要求满足的min_period. 显然,输入transtion 越大,min_period 要求越大。

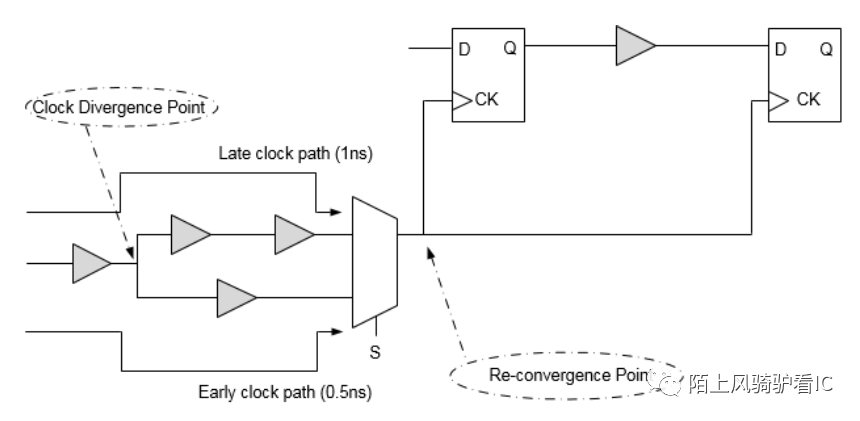

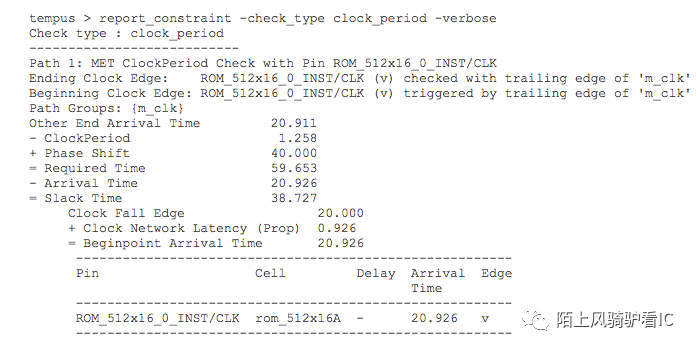

搞清楚lib 的定义之后再来对着具体电路看,老驴懒得画图,从Tempus 的user guide 里找了一张比较典型的图,假装后面的寄存器是RAM. 所谓的clock min period check, 就是先计算电路中到达RAM CLK pin 真实的clock period 值,然后跟lib 中定义的值比较。

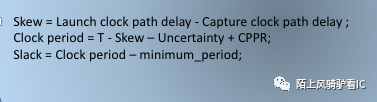

要计算电路中到达RAM CLK pin 真实的clock period, 首先要明白都要考虑哪些因素:

- SDC 中定义的clock period: T;

- Clock lunch path 跟Capture path 上的derate 值;

- Clock uncertainty.

- Clock path 上的crosstalk.

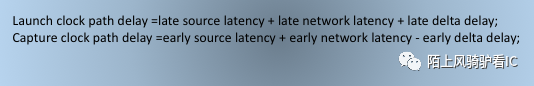

对于示例电路,Clock 在到达RAM 的CLK pin 之前就有了分叉,按照惯例, 此处从clock root 点到clock 分叉点的delay 称为source latency; 从clock 分叉点到RAM CLK pin 的delay 称为network latency, 那么在考虑串扰的情况下可得:

如果设置了OCV 或读入了AOCV/ SOCV 文件,并且enable 了对应的计算,工具在计算latency 的时候会自动将derate 值计算在内,对于source latency 需要减去CPPR. 因为Clock period 计算的是不同沿clock 的delay 所以CPPR 中只减掉Derate 部分,cross talk 引起的delta delay 不会被减掉。故,clock period 的计算为:

在memory 选型的时候,clock min period 是一个重要指标,需要根据电路实际的工作频率, clock 的uncertainty, Crosstalk, 工艺的Variation 来选定。

在STA 阶段如果有clock min period 的violation, 可以做:

- check 是否有clock 的分叉点,如果有是否可以尽量把分叉后的path 做短;

- 修clock transition, 更小的transition 对应的clock min period 要求更小。

- check clock path 上是否有crosstalk, 如果有,修干净。

如果以上事情都做好了,依然meet 不了clock min period 的需求,说明memory 选型时考虑不周全,可以尝试换low VT 的memory , 再不行就需要推倒重来。

再贴一个Tempus report 的示例:

2122

2122

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?