今天我们来介绍如何来修复ECO阶段的min pulse width violation(最小脉冲宽度违例)。首先,我们来介绍一下什么是min pulse width。

min pulse width,全称为最小脉冲宽度检查。这也是一种非常重要的timing arc check,经常用在时序器件或者memory上面。

一般情况下,由于cell本身有变异,rise和fall delay不相同,这样可能会造成时钟信号脉冲宽度减小。

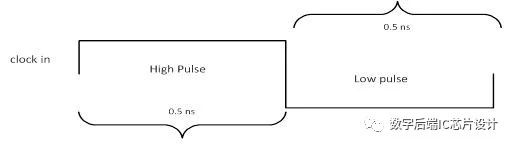

如下图一个周期为1ns,duty cycle 为50%的clock信号

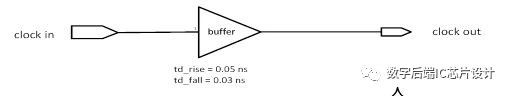

在经过一个buffer(rise delay: 0.05, fall delay:0.03)

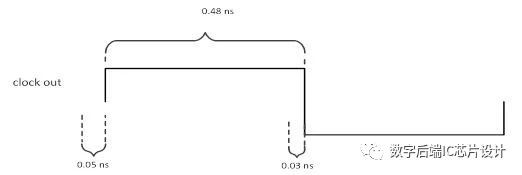

clock信号波形变成如下图所示:

因此,可以知道,如果某个cell的rise delay大于fall delay,那么输出时钟的脉冲宽度要比输入时钟小。如果时钟信号经过一系列相同类型的单元,则时钟信号的脉冲宽度将会持续减小。如果小于某个最小宽度,可能会导致器件不能正常的捕获数据。

因此,在做timing分析时,我们是必须对cell的pin做min pulse width检查。通常有两类方法:

1) sdc里面定义

set_min_pulse_width 2.0 [get_clocks CK1]

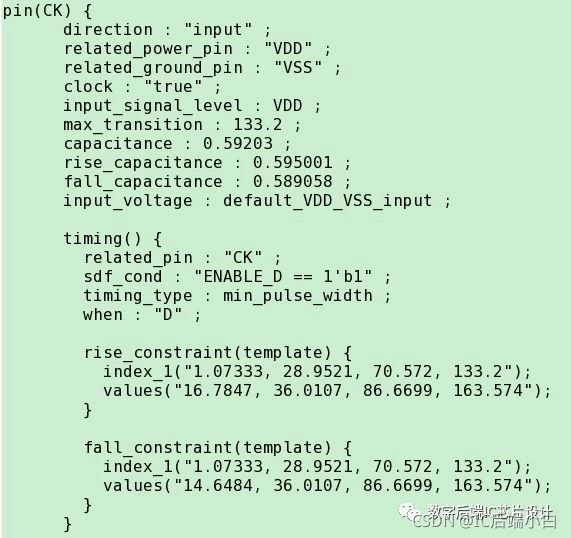

2)library里面定义

那我们如何去修复min pulse width的violation呢?

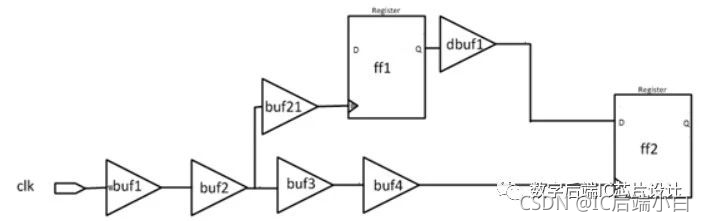

首先,我们来看min pulse width的计算方式,如下电路图,我们想要计算ff2的clock pin的min pulse width check

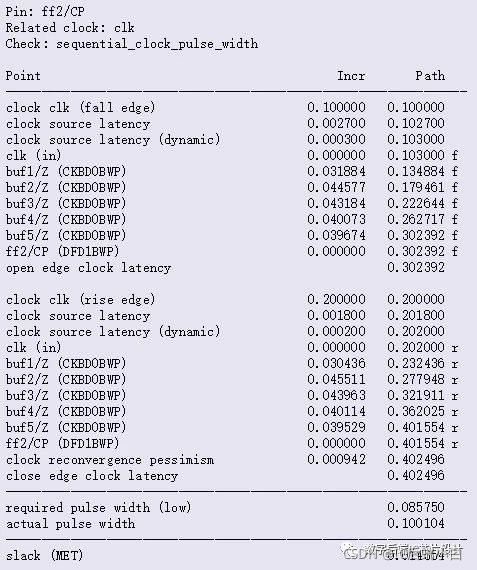

采用report_min_pulse_width -path_type full_clock_expanded [get_pin ff2/CP],得到下面path路径slack图。

从上面的timing slack图,我们也可以从cell和net这两个角度来修复min pulse width。

首先是从cell角度,由于普通buffer上升和下降的delay不一样,如果经过一连串的buffer的话,有时候会发生min pulse width的violation。因此,如果采用上升下降沿较为均衡的clock buffer则有助于改善violation的产生。可以想象一下,上面这timing path中,如果上半部分fall edge和下半部分rise edge上的buffer delay都相等,那两者的差值,即require pulse width就很小,slack很容易met。

另外我们更加推荐采用clock inverter来取代buffer,相比buffer来说,inverter的上升和下降时间会相互补偿,这样就更容易避免min pulse width violation的产生。大家可以想象上面这个timing path中,如果fall edge和rise edge上的偶数位instance交错互换,这样得到的actual pulse width会更小。

然后,实际设计中,min pulse width violation的产生基本上并不来自cell本身,而是由于net上的noise影响。上述这个timing path中,如果加上有一些比较严重的SI影响,使得fall edge的delay更大,rise edge的delay更小,这样就比较容易造成min pulse width violation。因此,通常情况下,我们修复min pulse with 的第一要点就是修复这段path中一些比较大的noise。如何修noise? 可以参考下面文章。

本文介绍了如何解决电子设计自动化(EDA)中的minpulsewidthviolation问题,这是一种常见的时序分析问题。minpulsewidth涉及时钟信号脉冲宽度的最小要求,若低于此值可能导致器件无法正常工作。修复方法包括选择上升下降延时均衡的clockbuffer或使用clockinverter,以及消除路径中的噪声。此外,文章强调了修复网络噪声对于解决minpulsewidthviolation的重要性。

本文介绍了如何解决电子设计自动化(EDA)中的minpulsewidthviolation问题,这是一种常见的时序分析问题。minpulsewidth涉及时钟信号脉冲宽度的最小要求,若低于此值可能导致器件无法正常工作。修复方法包括选择上升下降延时均衡的clockbuffer或使用clockinverter,以及消除路径中的噪声。此外,文章强调了修复网络噪声对于解决minpulsewidthviolation的重要性。

5773

5773

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?