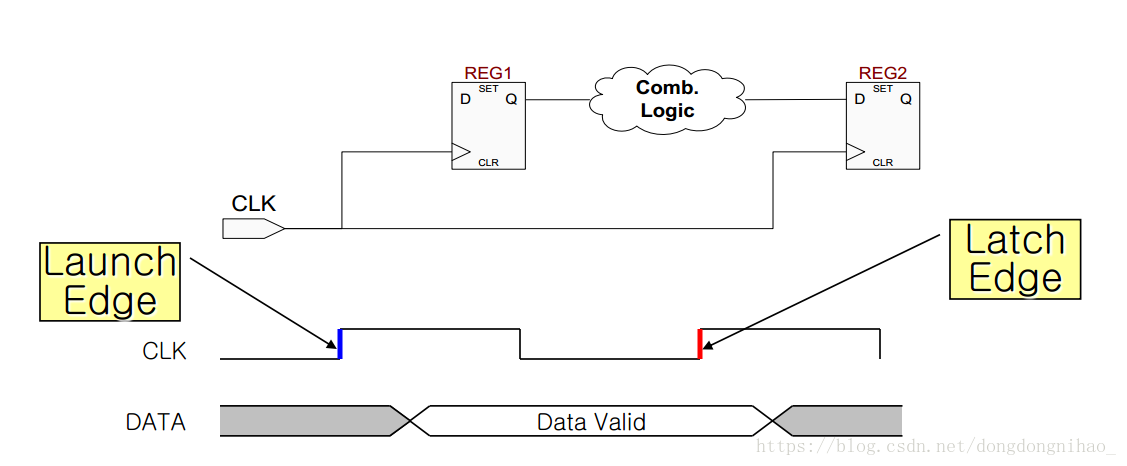

前面的博客里面有讲解建立时间Tsetup和保持时间Tholdon的概念以及要满足的和时钟之间的关系,这里不再重复,在了解建立时间裕量和保持时间裕量之前我们先来了解一下触发沿Launch Edges 和锁存沿Latch Edges。

一般认为Launch edge为 T=0;

Launch Edge: the edge which “launches” the data from source register

Latch Edge: the edge which “latches” the data at destination register (with respect to the launch edge, selected by timing analyzer; typically 1 cycle)

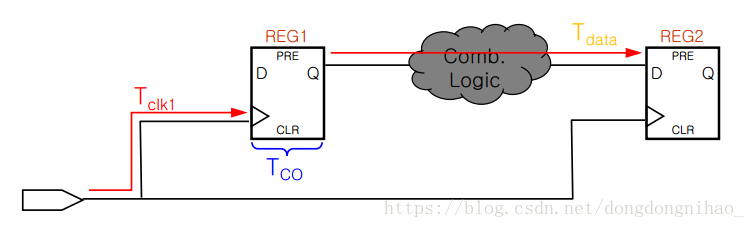

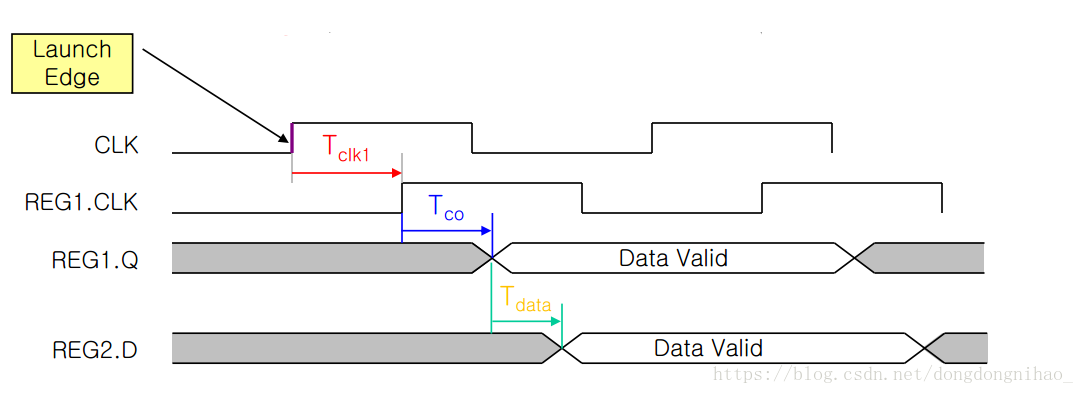

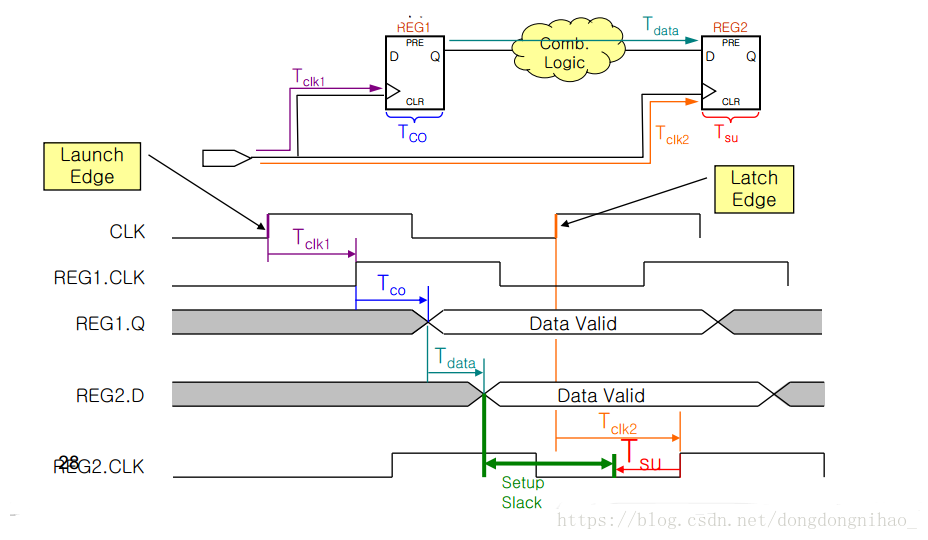

数据到达时间:(到达哪里?到达目的寄存器)

概念:The time for data to arrive at destination register’s D input

数据从触发沿开始到达目的寄存器的D端需要的时间,

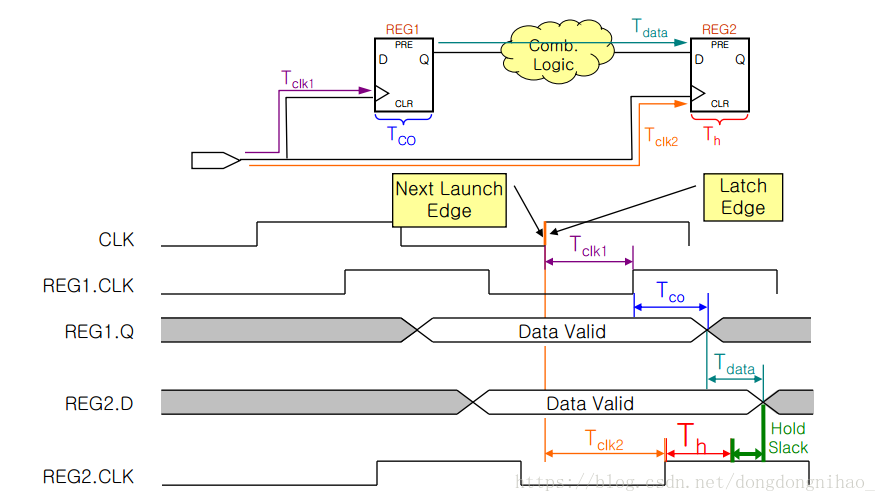

通过这个图片可以清楚的知道 Data arrival time = launch edge(0) +Tclk1 + Tco +Tdata

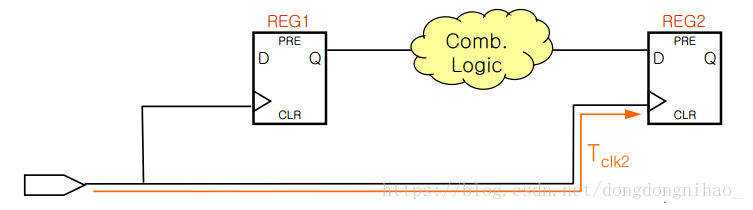

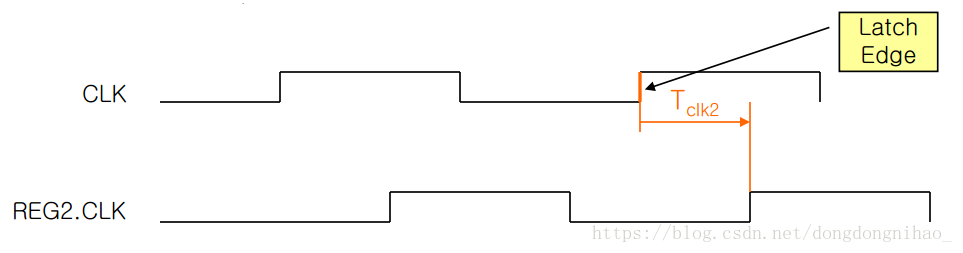

时钟到达时间:(到达哪里?到达目的寄存器)

概念:The time for clock to arrive at destination register’s clock input

由图可以知道,时钟到达时间:Clock arrival time = Latch edge + Tclk2 (为什么是锁存沿+Tclk2 ?看Latch edge的定义就可以知道(latch edge:从源寄存器“启动”数据的边缘在目的地寄存器“锁存”数据的边沿,相对于发射边缘,由定时分析器选择;通常为1个周期))

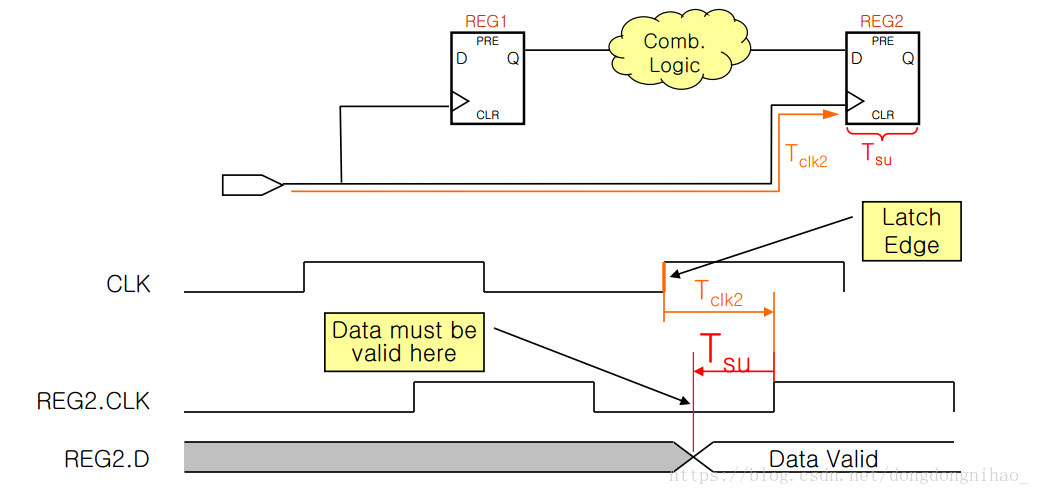

数据要求时间:

概念:数据锁存到目标寄存器所需的最短时间

setup:

Data Required Time = Clock Arrival Time - Tsu

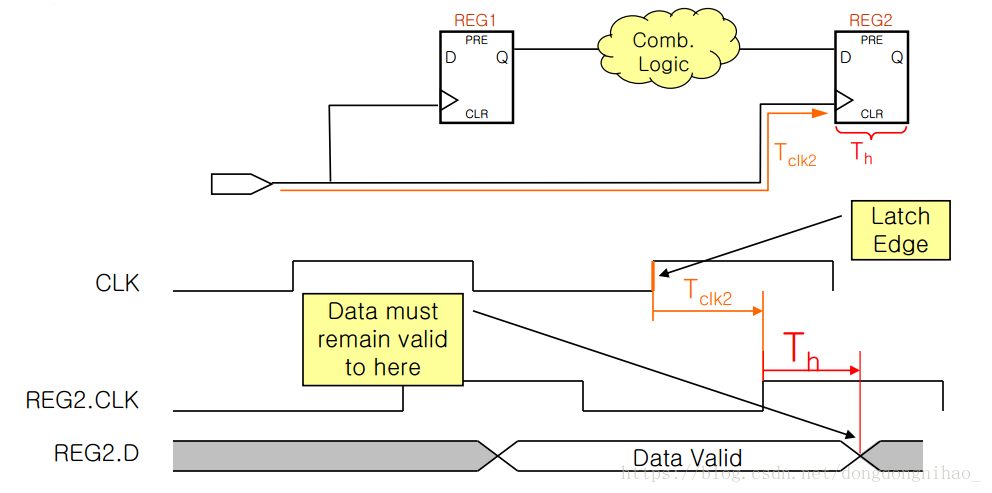

Hold:

Data Required Time = Clock Arrival Time + Th

建立时间裕量:满足设置时序要求的余量。 它确保启动的数据及时到达,以满足锁定要求。

Setup Slack = Data Required Time(Tperiod+Tskew-setup) – Data Arrival Time (Current)

【Tcap + T period > Tclk1 + Tco + Tdata 】: 时钟捕获沿来之前数据就要保持稳定。

保持时间裕量:

Hold Slack = Data Arrival Time (Next)– Data Required Time

【T cap_clk < T clk1 + T co + T data】:时钟发起沿到来以后数据仍要保持的时间

ps:建立时间裕量保持时间裕量的计算可以借鉴讲建立时间保持时间那片博客。

补充说明:这里的Tsu 和 Thd都是以REG2为分析对象;同时Data_arrival_time (Next)和(current)是一样的,没有区别。

补充理解保持时间裕量图:

REG1第一拍:

数据由灰色——>白色,这个过程用来分析Tsu,组合逻辑不能太长,不然建立时间会不满足

REG1第二拍:

数据由白色——>灰色,这个过程用来分析Thd,第一拍送过来的data此时在REG2的D端保持着,REG1在第二个cycle lunch edge采样后,经过Tco+Tdata时间送到了REG2的D端,REG2的D端数据需要在满足Thd之后再改变(白色变灰色),那么这个Tco+Tdata不能太短,否则不能满足Thd。

综上:Tsu不能满足是由于REG1和2之间组合逻辑太长Tdata过大导致

Thd不能满足是Tco+Tdata太小导致的,经过查询得知绝大部分SOC的保持时间可以做到0ns。对于soc后端来说常规的处理方法是在reg通路上插入buff,而且要说明的是Thd不满足和clk频率无关!

本文深入解析了时序分析中的关键概念,包括触发沿与锁存沿的定义,数据及时钟到达时间的概念,并详细阐述了建立时间裕量与保持时间裕量的计算方法及其重要性。

本文深入解析了时序分析中的关键概念,包括触发沿与锁存沿的定义,数据及时钟到达时间的概念,并详细阐述了建立时间裕量与保持时间裕量的计算方法及其重要性。

2187

2187

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?