激光雷达作为一种高精度、高性能的传感技术,广泛应用于自动驾驶、机器人导航、工业自动化、无人机等应用领域。激光雷达控制板可以很好的满足这些领域中对于精准控制和数据处理的需求。

基于FPGA的激光雷达控制板主要是用于控制线阵激光器,并高效地采集和处理大量的激光点云数据,具备强大的数据处理能力和高速数据传输接口,以确保系统能够准确地感知周围环境。

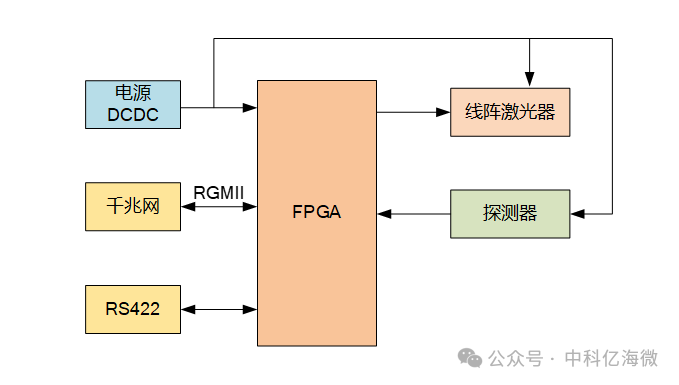

图 激光雷达控制板框图

本方案由FPGA处理单元、千兆网接口单元、RS422接口单元、线阵激光器驱动单元以及探测器回波接收单元组成。FPGA处理单元主要完成线阵激光器控制、回波信号接收、距离与空间坐标解算以及点云数据输出功能。网络接口单元采用PHY芯片通过RGMII接口与FPGA相连,实现千兆网接口,完成点云数据发送功能。选用隔离RS422芯片实现RS422通信接口,接收外部指令实现通信功能。

方案优势

(1)高精度数据处理:激光雷达控制板具有强大的数据处理能力,能够高效地处理激光雷达传感器采集到的大量数据,并实现高精度的距离测量和环境感知。

(2)稳定性和可靠性:FPGA方案具有良好的稳定性和可靠性,能够在各种复杂环境下稳定运行,确保激光雷达系统的正常工作。

(3)灵活的控制功能:可以实现对激光器的多种参数设置和调整,满足不同应用场景的需求。

(4)良好的系统集成性:激光雷达控制板将激光器驱动、探测器回波接收、信号解算、点云输出等组件有效集成,提升了整个系统的性能和效率。

典型应用

激光雷达控制板在多个领域有着广泛应用:

-

自动驾驶技术:激光雷达控制板在自动驾驶汽车中起着关键作用,通过控制激光雷达传感器的扫描和数据处理,实现车辆对周围环境的感知和定位,从而实现自动驾驶功能。

-

智能交通系统:在智能交通系统中,激光雷达控制板可以用于车辆和行人的检测、交通流量监测、道路状况评估等应用,提高交通管理的效率和安全性。

-

工业自动化:在工业自动化领域,激光雷达控制板可以用于机器人导航、物料处理、仓储管理等任务,实现生产线的自动化和智能化。

-

环境监测:激光雷达控制板可以应用于环境监测领域,如大气污染监测、水质监测、地质勘探等,实现对环境参数的高精度测量和监测。

-

安防监控:在安防监控系统中,激光雷达控制板可以用于建筑物周界的监控、入侵检测、人员跟踪等功能,提高安防系统的监控效率和准确性。

-

无人机领域:可用于障碍物检测与避障、地形建模与测绘、目标跟踪与识别、导航与定位以及三维重建与建筑检查等任务。

790

790

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?