提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档

前言

无意间发现了JTAG to AXI Master IP核,发现这个东西对于FPGA单独调试应该比较有用,故而来研究了一番,发现这个东西切实很好用而且也比较简单。想起我之前为了构造一个指令系统专门写了一个UART2BUS,如果当时我知道使用JTAG to AXI Master IP核,那我肯定直接使用这个了,所以说真的是要不停的学习才能不会落伍呀

用法

很多FPGA工程都是通过总线寄存器来进行时序的控制,参数的传递等等。那JTAG to AXI Master IP就提供了一种这样的便捷的方法,而且只需要JTAG接口就可以了,这个接口对于每一个FPGA板卡来说肯定是必备的,而且调试环境也是Vivado现成提供的。在项目初期,FPGA单独进行开发的时候(或者软件部分还没有参与进来的时候),利用JTAG to AXI Master IP 相关调试的工作就可以不需要软件人员的配置而继续进行下去。

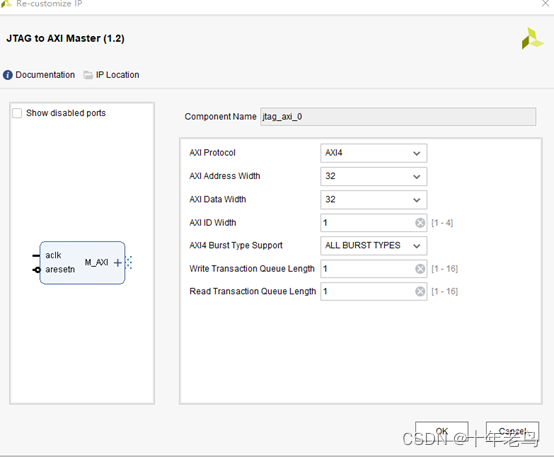

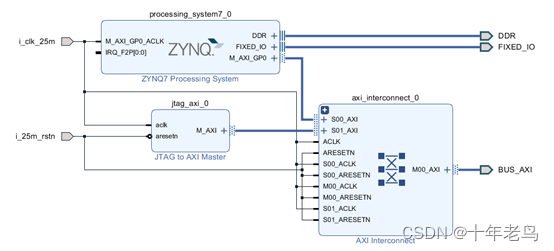

这里我套用我的博文《ZYNQ开发系列——使用AXI4LITE接口进行PS和PL交互》中的工程,在其基础上将JTAG to AXI Master IP添加上去

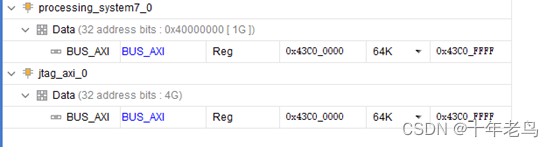

基地址和地址区间设置为与PS相同的,这样相当于不仅仅ARM可以对BUS_AXI进行操作,JTAG_AXI_0这个IP核也是可以对BUS_AXI进行操作

就是这么简单,什么手册都没看,看着端口名字就知道怎么连接了。

Tcl指令

我们可以打开vivado界面通过按钮来找到FPGA器件后,然后再输入tcl指令,而在这里,我为了以后使用的便利性,我就不打开vivado了。直接打开vivado tcl shell输入指令来操作,为后面的操作脚本化来做准备。

open_hw

connect_hw_server

open_hw_target

current_hw_device [get_hw_devices xc7z030_1]

refresh_hw_device -update_hw_probes false [lindex [get_hw_devices xc7z030_1] 0]

proc ReadReg { address } {

create_hw_axi_txn read_txn [get_hw_axis hw_axi_1] -address $address -type read

run_hw_axi read_txn

set read_value [lindex [report_hw_axi_txn read_txn] 1];

delete_hw_axi_txn read_txn

set tmp addr=0x

append tmp $address

append tmp , data=0x

append tmp $read_value

return $tmp

}

proc WriteReg { address data } {

create_hw_axi_txn write_txn [get_hw_axis hw_axi_1] -address $address -data $data -type write

run_hw_axi write_txn

set write_value [lindex [report_hw_axi_txn write_txn] 1];

delete_hw_axi_txn write_txn

}

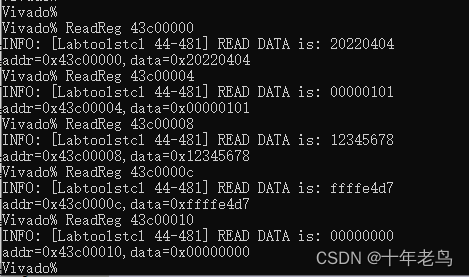

读地址测试:

ReadReg 43c00000

ReadReg 43c00004

ReadReg 43c00008

ReadReg 43c0000c

ReadReg 43c00010

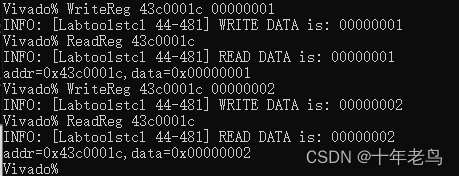

读写测试:

WriteReg 43c0001c 00000001

ReadReg 43c0001c

WriteReg 43c0001c 00000002

ReadReg 43c0001c

大功告成!!

展望

这确实是一个比较方便的调试手段,不需要额外增加其他硬件资源,而JTAG下载线是FPGA调试所必备的。这种调试手段确实能够提升效率,后续我要研究下如何使用我的vb.net的上位机来进行操作,通过上位机来控制,做到每个寄存器地址的实时扫描以及解析,将又不失为一种更为高效的调试手段。

我在网上看到有一篇《JTAG to AXI Master的API函数读写操作》,看起来似乎不错,准备研究和尝试一下,同时或者我自己将tcl指令封装起来也不失为另外一种实现方法。下一篇见

2594

2594

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?