器件支持性

JESD209-5B中,link-ecc仅仅是一个可选的功能; 另外,即使器件支持link-ecc功能,在WCK小于等于1.6GHz(≤ 3200Mbps)的情况下,也没必要支持(从这个描述可以看出,link-ecc主要是用来解决链路传输失效)。

linkecc 主要内容

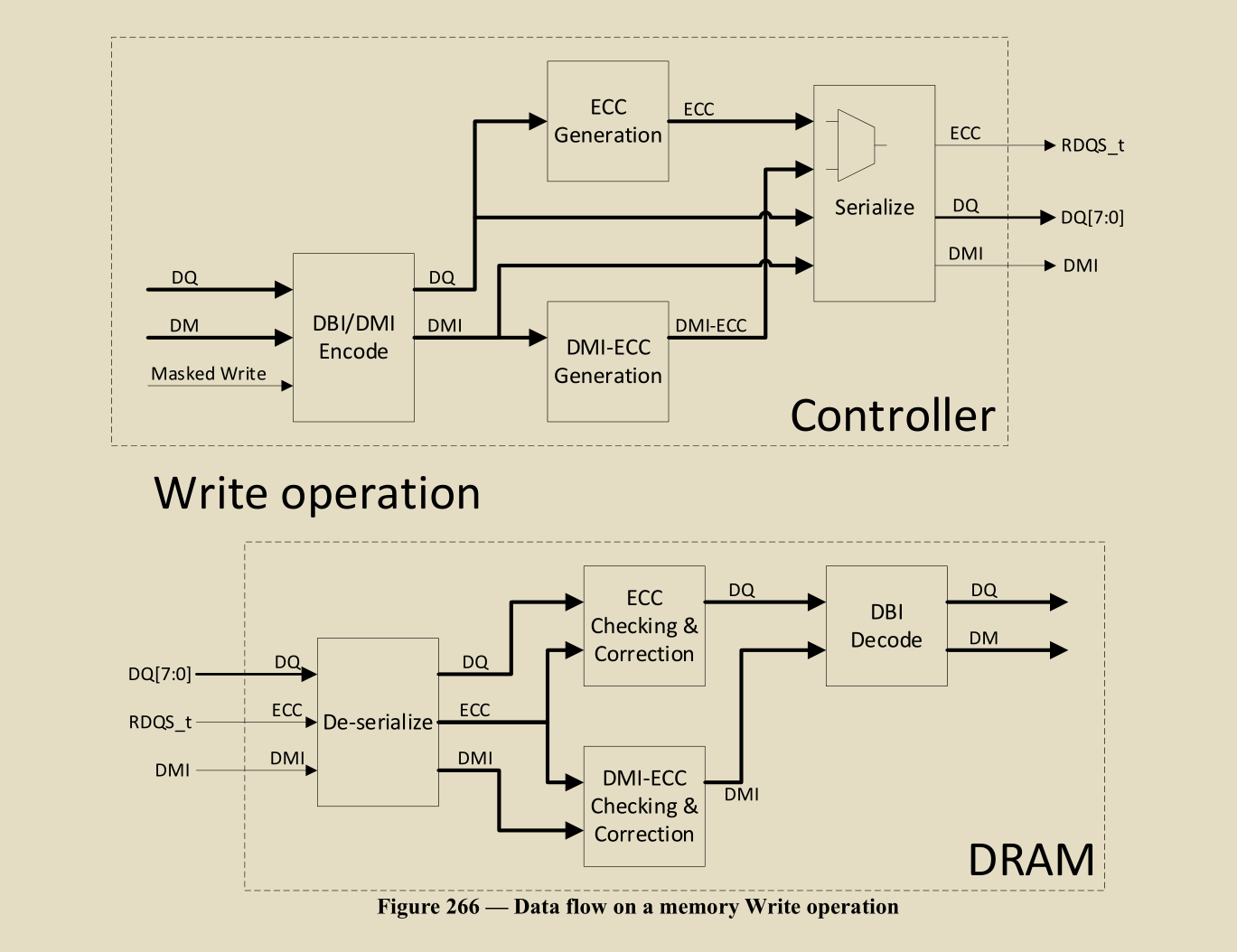

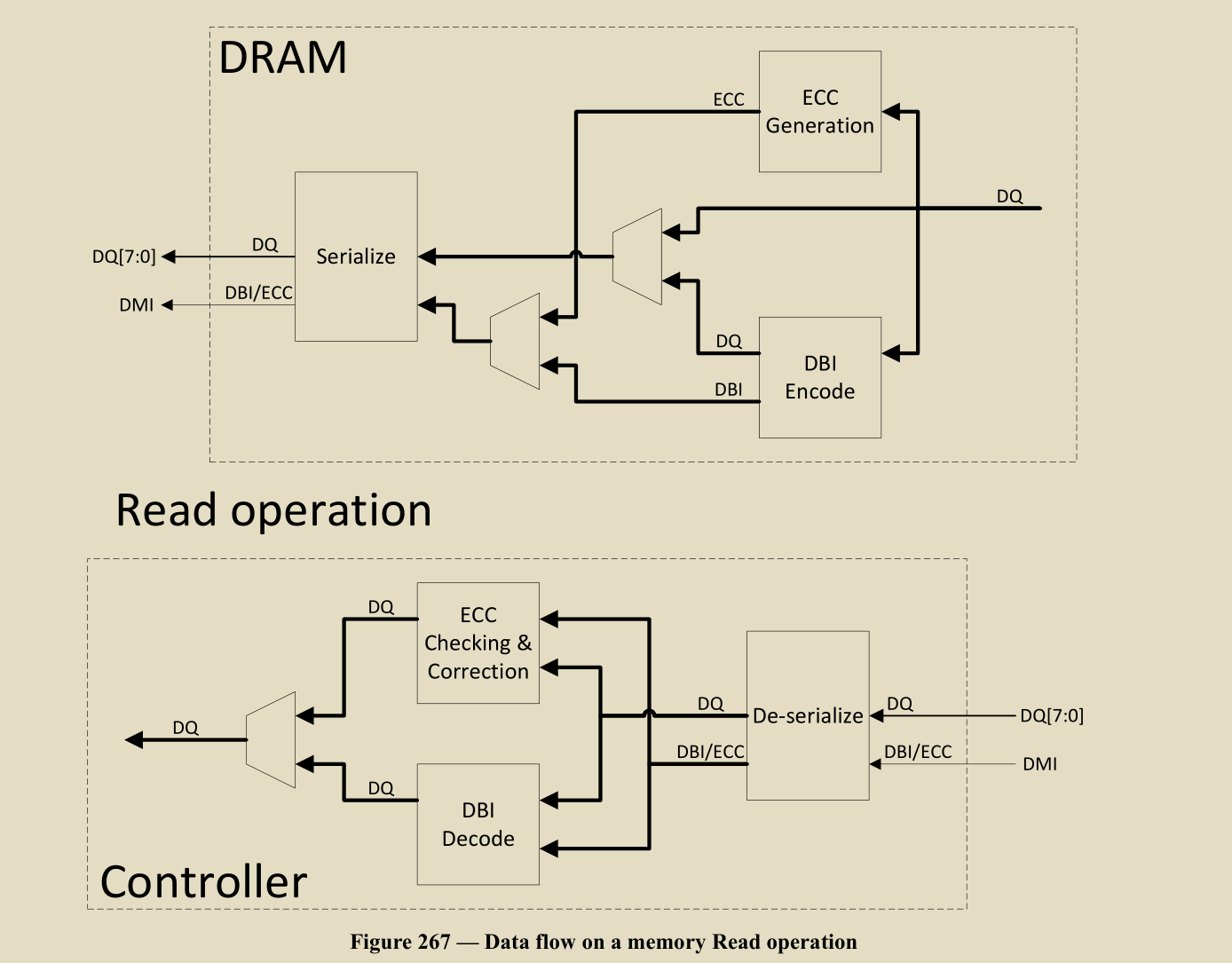

- linkecc模式下,128bit数据生成9bit ECC parity; 16bit DMI生成6bit ECC parity(从数据-parity bit数来看,使用的SECDED算法);

- linkecc模式下,协议要求必须使用DBI编码数据,因为DM会导致数据被误纠(这里描述的很不清晰,看起来不存在关DBI且关DM并且使能linkecc的情况);

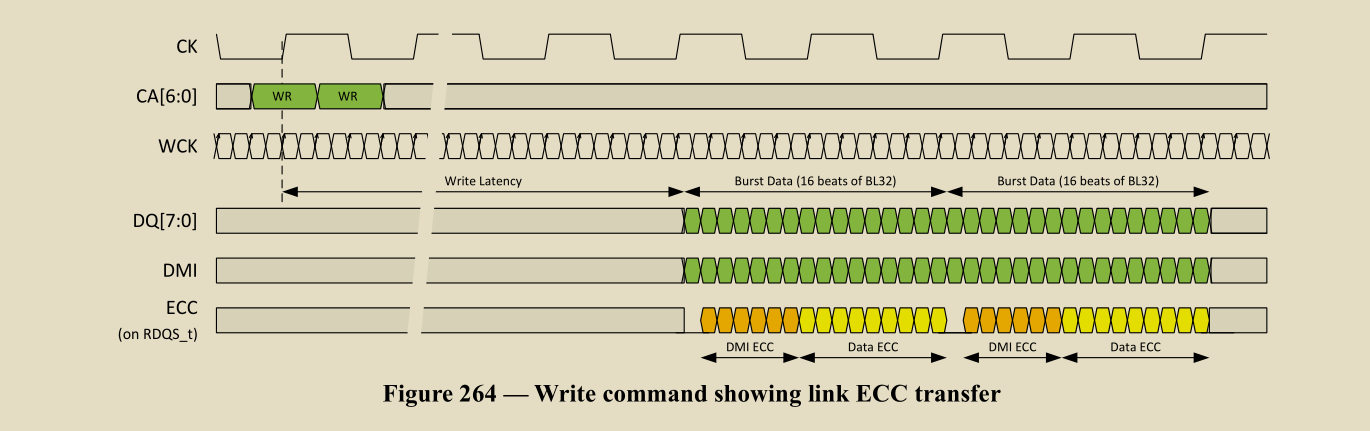

- linkecc是基于8bit DQ而言的;每8bit DQ对应1bit DMI,8bit DQ burst32会产生2个128bit数据,同时会产生2个16bit DMI数据(姑且也称之为数据);

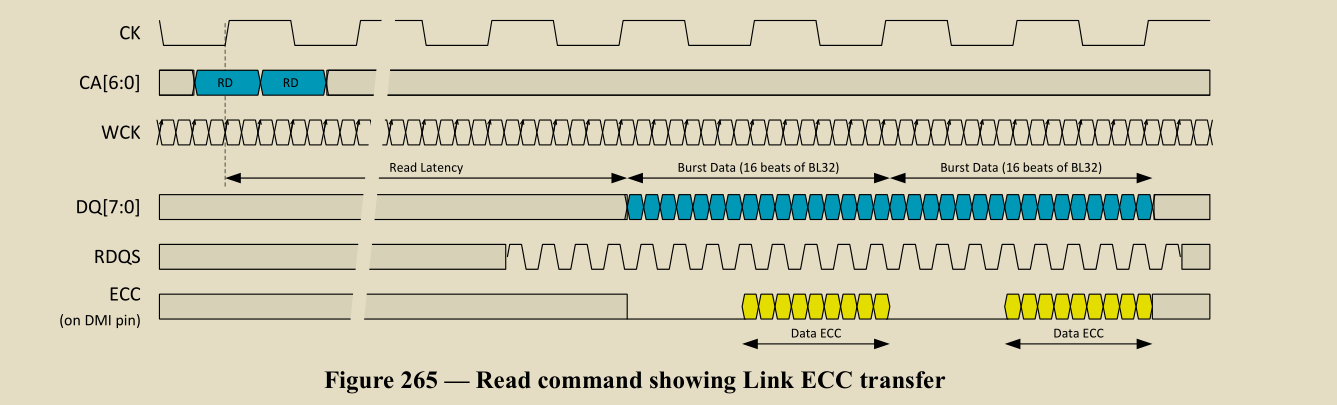

- linkecc的parity,写方向通过RDQS_t传输,读方向通过DMI传输;

- 对于写方向,RDQS_t第一个数据空着,后面传6bit DMI的parity,再传9bit data的parity;

- 对于读方向,DMI空7bit的时序,然后传9bit的data parity;

- 对于读方向,linkecc和RDBI是互斥的,因为都需要使用DMI传输有效信息;因此读的时候,parity无需考虑DBI;

- 对于读方向,CAS B3必须是0(因为数据需要BL16对齐,参见2.2.6 burst sequence章节);

- 对于读方向,linkecc和read data copy功能互斥;

- 对于BL32, 一笔burst对应2套ECC数据单元(128 data + DBI + parity);对于BL16,一笔burst数据对应1套ECC数据单元(128 data + DBI + parity);

写方向时序图

读方向时序图

写方向数据流

读方向数据流

1333

1333

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?