对于DDR4协议,大家都知道,由于BG的引入,DDR4协议增加了tCCD_L和tCCD_S的时序参数,其对应相同BG/不同BG列操作的间隔。但是大家有没有想过这种区别的本质原因是什么?

首先,从逻辑上讲,DDR协议中绝对时间的时序参数,往往都和器件或者工艺物理因素有关系,比如tREFI是依照电容器漏电时间而定的,tRFC是器件刷新电容器的物理时间而定的;

对于tCCD_S,其固定等于4nCK,这个很容易理解,因为DDR4数据传输是burst8为单位,也就是4nCK才能传完数据,所以tCCD_S必须>=4nCK,否则读数据就多驱了。

对于tCCD_L, 其值是一个可变的值:

| 时序参数 | DDR4 1600 | DDR4 1866 | DDR4 2133 | DDR4 2400 | DDR4 2933 | DDR4 3200 | DDR5 3200 | DDR5 3600 | DDR5 4000 | DDR5 4400 | DDR5 4800 | DDR5 5200 | DDR5 5600 | DDR5 6000 | DDR5 6400 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| tCCD_L | max(5 nCK, 6.250 ns) | max(5 nCK, 5.355 ns) | max(5 nCK, 5.355 ns) | max(5 nCK, 5 ns) | max(5 nCK, 5 ns) | max(5 nCK, 5 ns) | Max(8nCK, 5ns) | Max(8nCK, 5ns) | Max(8nCK, 5ns) | Max(8nCK, 5ns) | Max(8nCK, 5ns) | Max(8nCK, 5ns) | Max(8nCK, 5ns) | Max(8nCK, 5ns) | Max(8nCK, 5ns) |

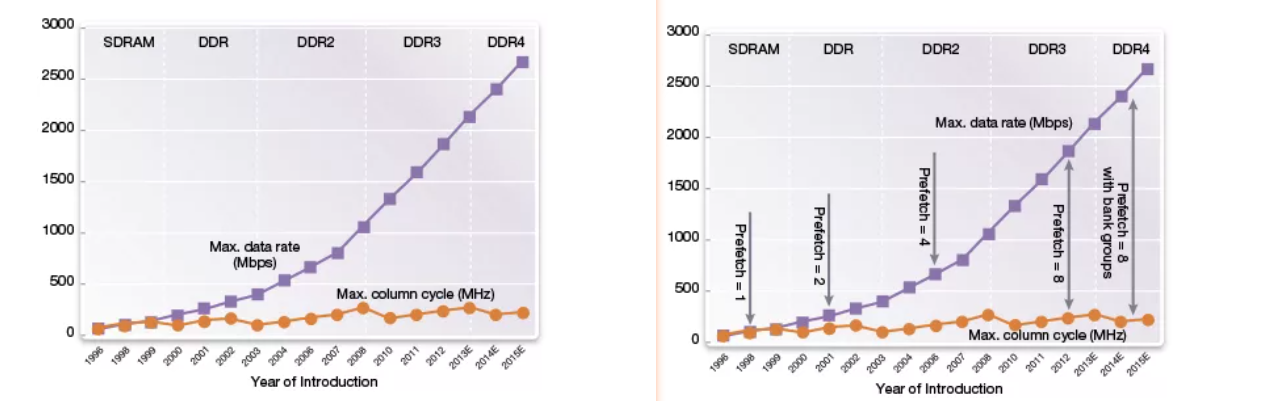

上表可以看出,DDR协议基本上所有频点都有一个5ns的绝对时间要求,对于1600这种低频(core 时钟频率也更低)来说,绝对时间更大,我们可以看出,这是由于DRAM core内部的一些处理达不成4nCK的要求导致的。

这里借用synopsys的一张图:随着DDR协议的发展,接口速率(频率)越来越高,但是core工作频率,受电容器本身充放电时间的限制,始终工作在200Mhz左右。

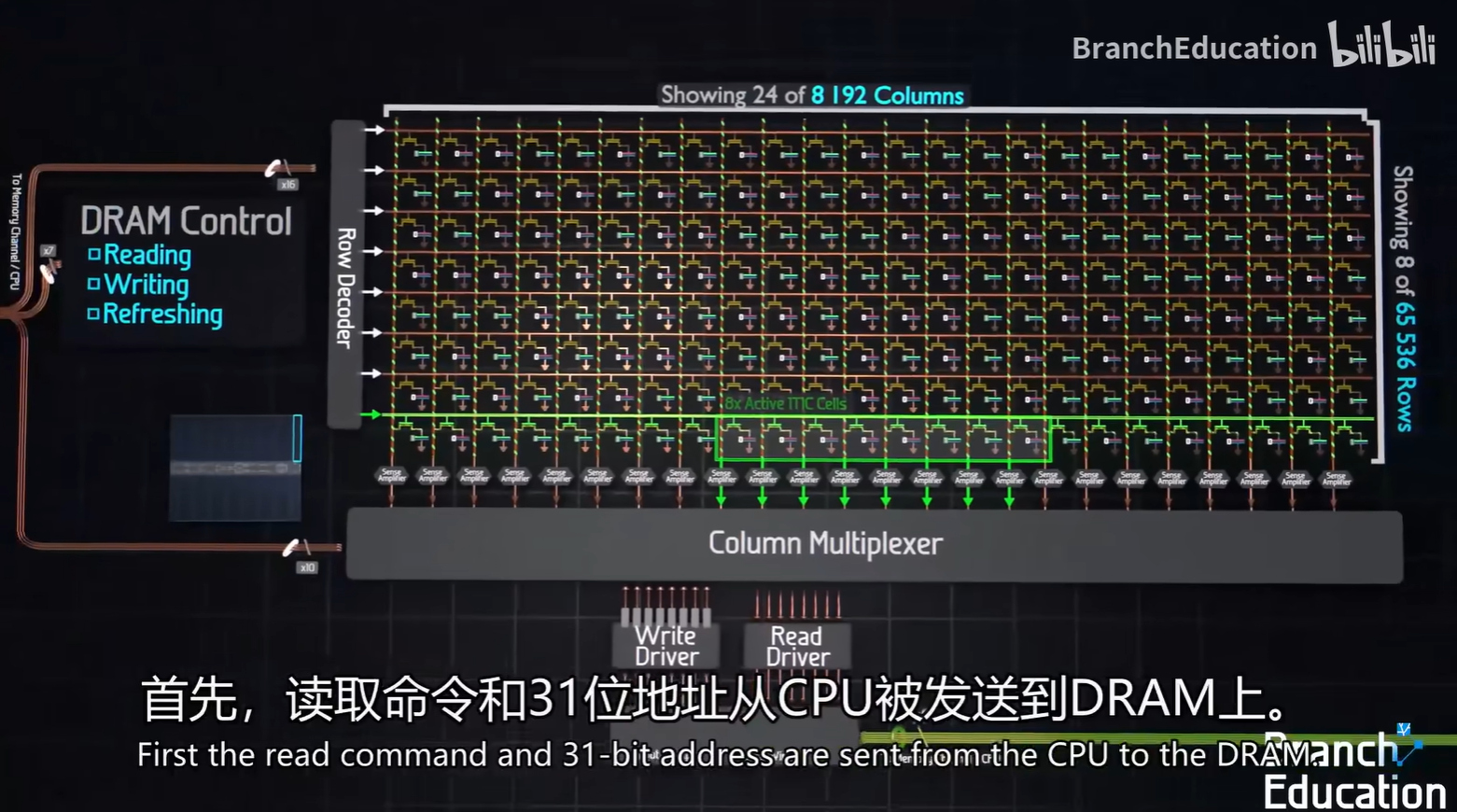

OK,那我们就更深入到DRAM底层实现,来看看相同bank到底哪里拖了后腿;

下面是一个bank的结构:

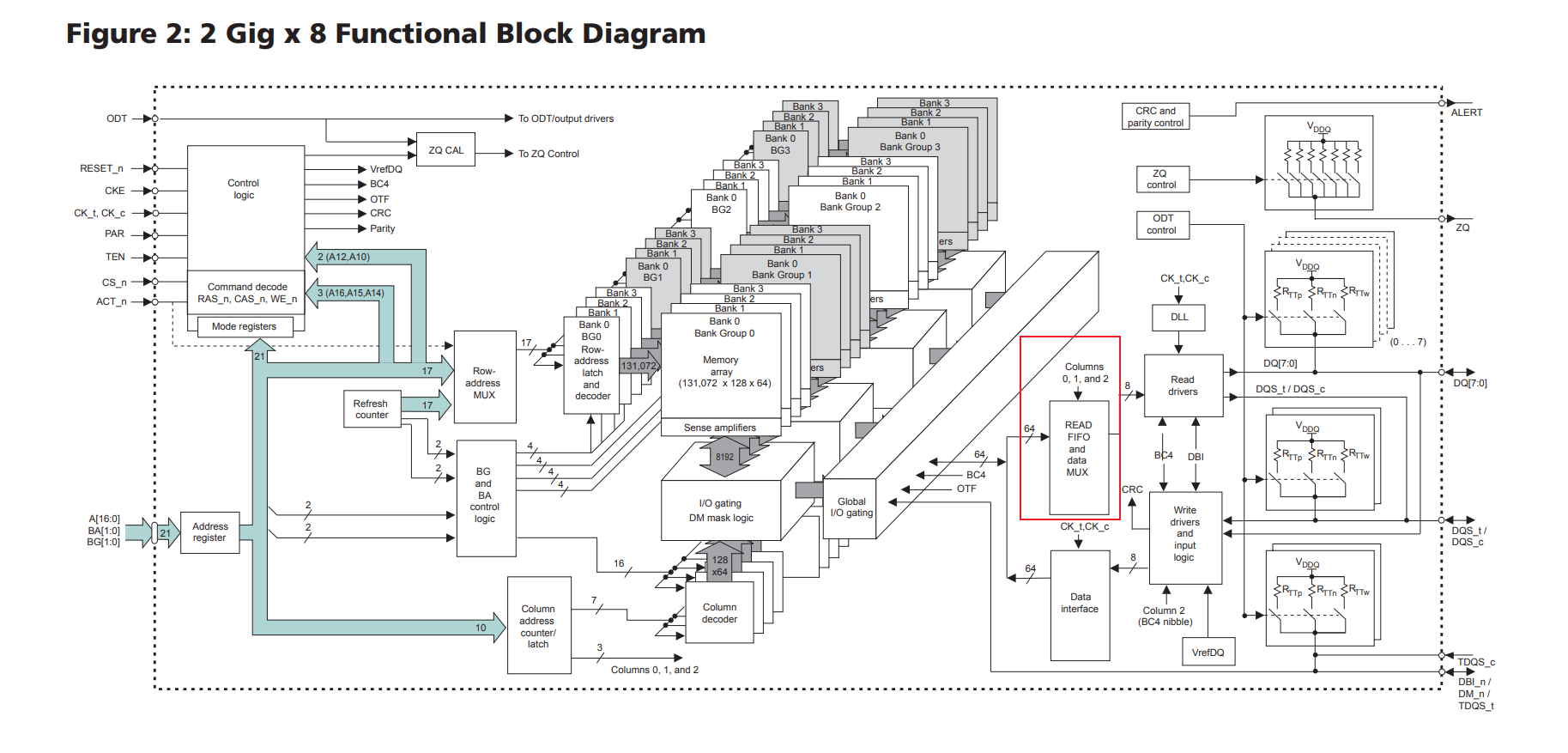

下面是一个DDR4 器件的结构:

以上图M厂家datasheet,读操作为例:

- 当前已经是active的状态,行地址线被选中,所有(2^10)的列地址线已经被放大器依照电容存储的电荷,置位成0或者1电平;

- 读操作到来时,BG的IO gating从连接到他的8192bit数据(一个row)中选出8列送到DEMUX(burst buffer)处;这里的时间开销,导致了DDR协议的RL,这里记作t_latency;

- BG内共享的IO gating状态复原,等待下次读操作,这个时间记作t_recovery;

- burst buffer排空,耗时4nCK,此步骤和上一步并发;

- 下一个读操作到来,再次选出列地址内容送入burst buffer中;

上面t_latency不管多大, 都不会影响到数据的流水;但是t_recovery如果大于4nCK, 就会导致两次读命令的数据产生气泡,也就造就了tCCD_L这个参数;

不过上面也有一些细节的问题:burst buffer填充,为什么不消耗时间?

一种可能是M家器件手册这个图只是示意图,实际上burst buffer是BG内部的bank共享的,这样t_recovery对应burst buffer填充的时间,一切都比较合理起来。

另一种可能是,burst buffer的数据内容,本身就是IO gating送出来的wire线直连,所以不需要消耗时间;这样burst buffer中的数据没有传完,IO gating送出来的数据不能有变化;所以t_recovery是4nCK数据传输时间 + IO gating重新列选择的时间。

但是具体器件的实现方案,我不知道,上面这些都是个人的揣测,只有在vendor工作过才能知道这些实现细节。

参考资料:

https://www.bilibili.com/video/BV1vP411c7pt/?spm_id_from=333.337.search-card.all.click&vd_source=d8270383a9fea174fee8b8db5953aeb9

https://media-www.micron.com/-/media/client/global/documents/products/data-sheet/dram/ddr4/16gb_auto_ddr4_z32d.pdf?rev=a20dfa7ff44c48a99ff49edc32b07bd1

https://www.synopsys.com/designware-ip/technical-bulletin/ddr4-bank-groups.html

本文探讨了DDR4协议中tCCD_L和tCCD_S时序参数的区别,重点解释了tCCD_L随频率变化的原理,以及它如何受到核心工作频率限制的影响。文章还引用了Synopsys的技术信息和实际设备结构来说明这一现象。

本文探讨了DDR4协议中tCCD_L和tCCD_S时序参数的区别,重点解释了tCCD_L随频率变化的原理,以及它如何受到核心工作频率限制的影响。文章还引用了Synopsys的技术信息和实际设备结构来说明这一现象。

609

609

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?