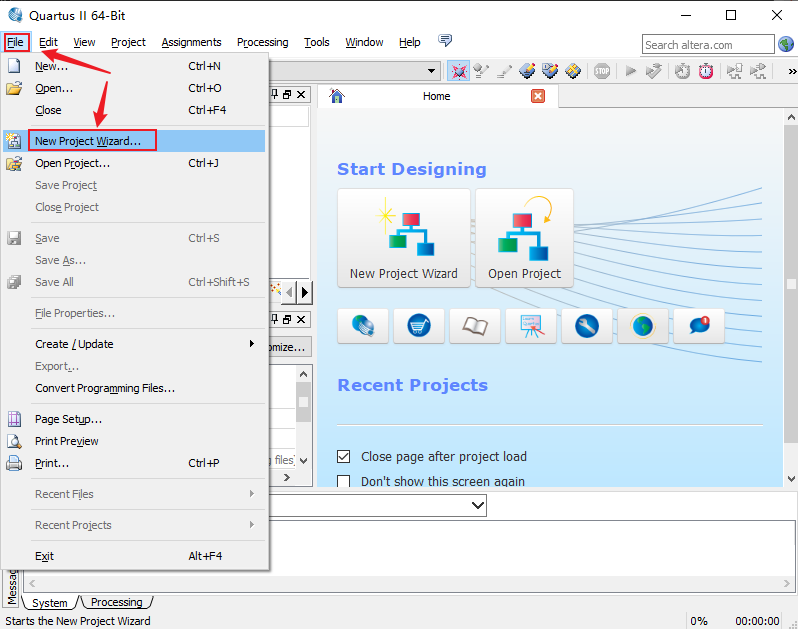

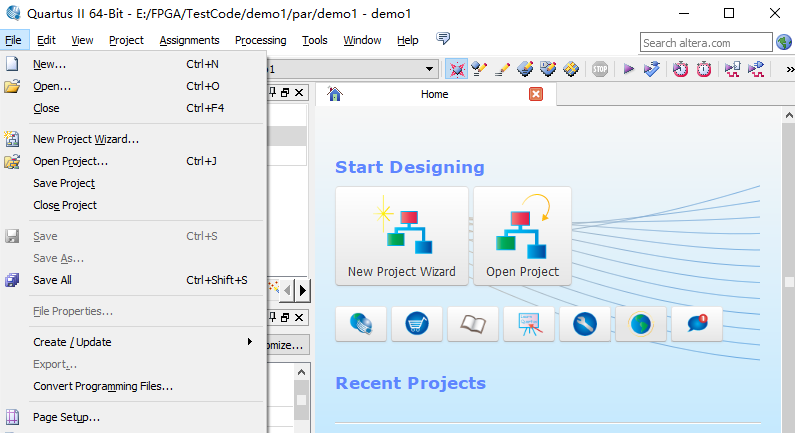

一、新建工程导航流程

在菜单栏 “File -> New Project Wizard…”

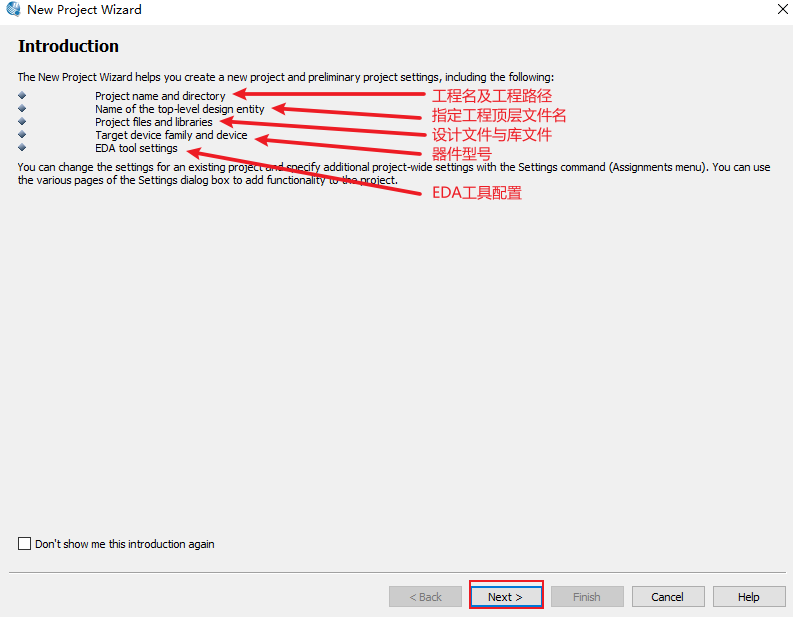

1、导航配置内容简介

- 工程的命名以及指定工程的路径;

- 指定工程的顶层文件名

- 添加已经存在的设计文件和库文件

- 指定器件型号

- EDA工具设置

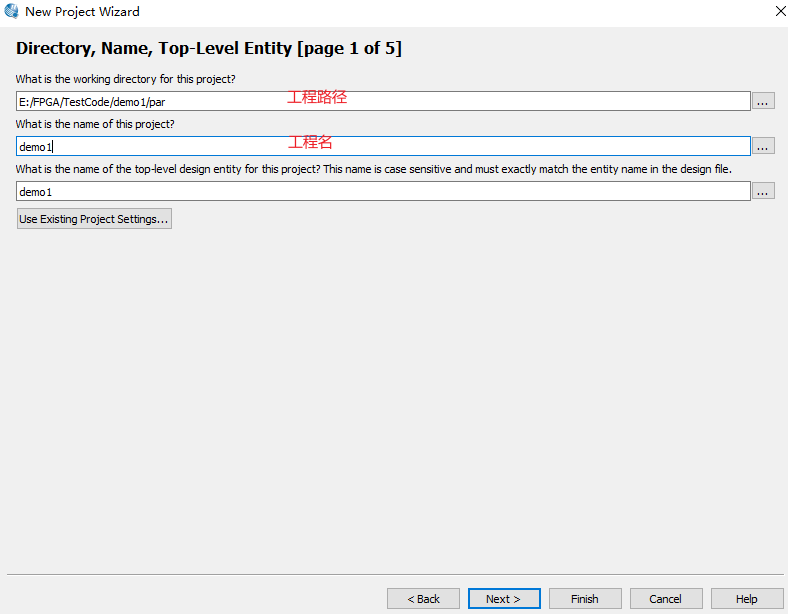

2、工程名以及工程路径

- 工程的路径;

- 工程名(使用顶层文件名)

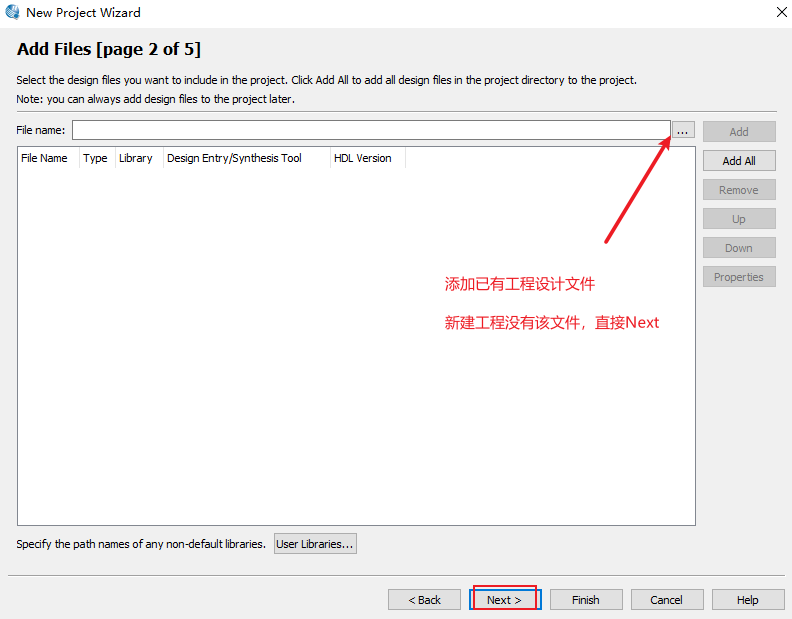

3、添加工程设计文件

Verilog / VHDL文件,新建工程,跳过。

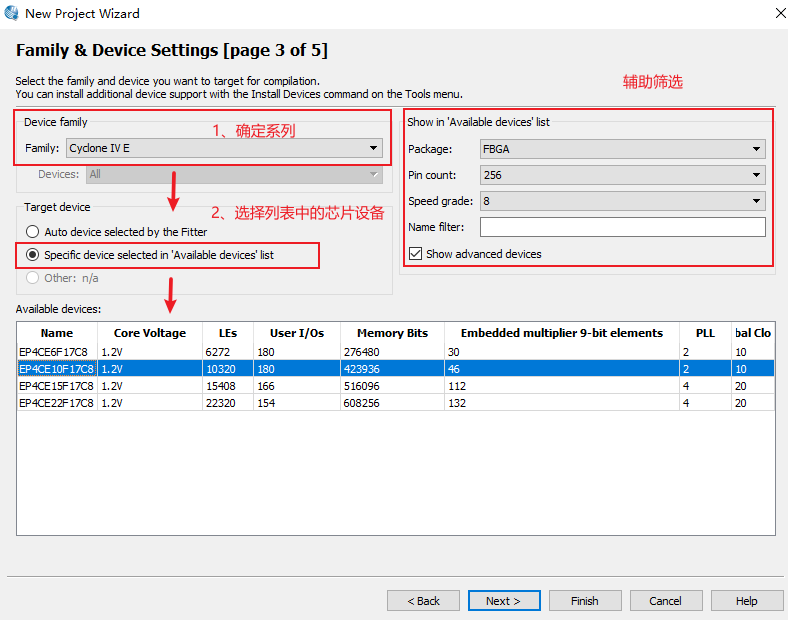

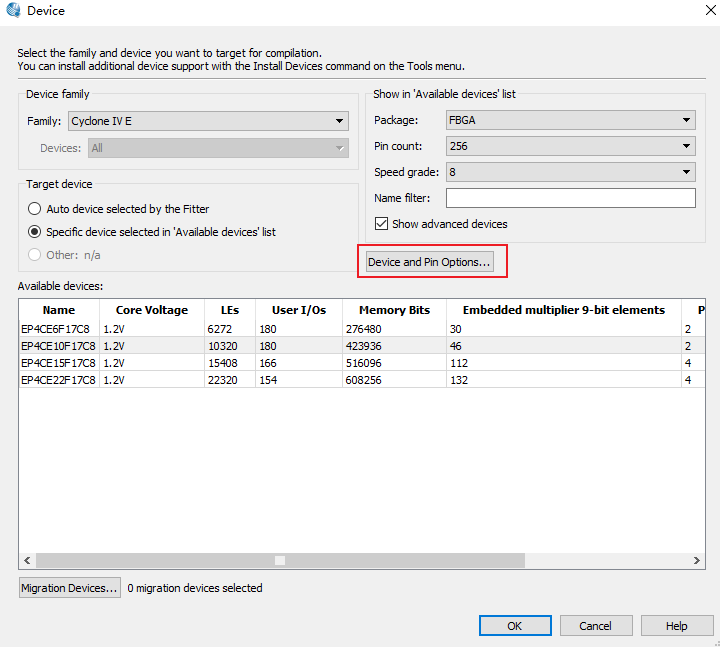

4、选择FPGA芯片

选择芯片系列,结合筛选条件,确定使用芯片

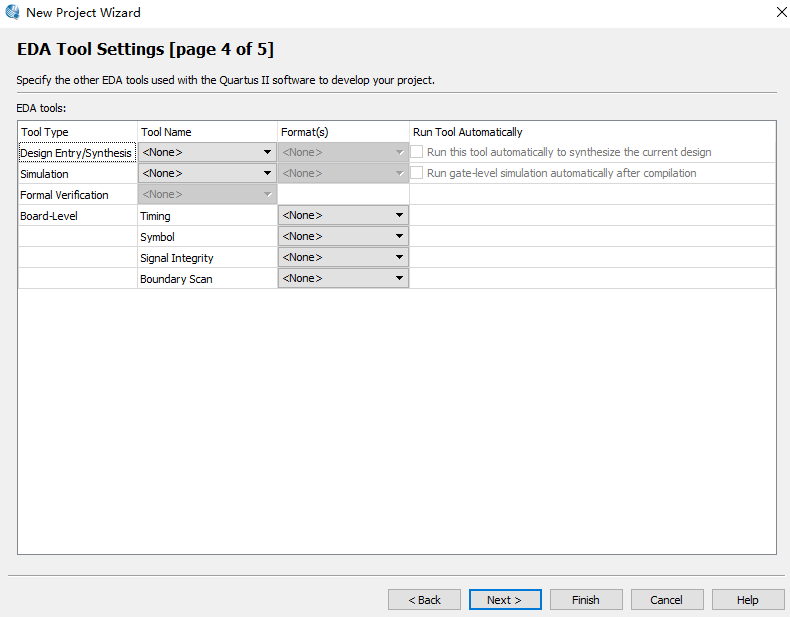

5、EDA配置

根据情况自己配置,若不使用仿真、综合分析等第三方工具,也可以跳过不配置。

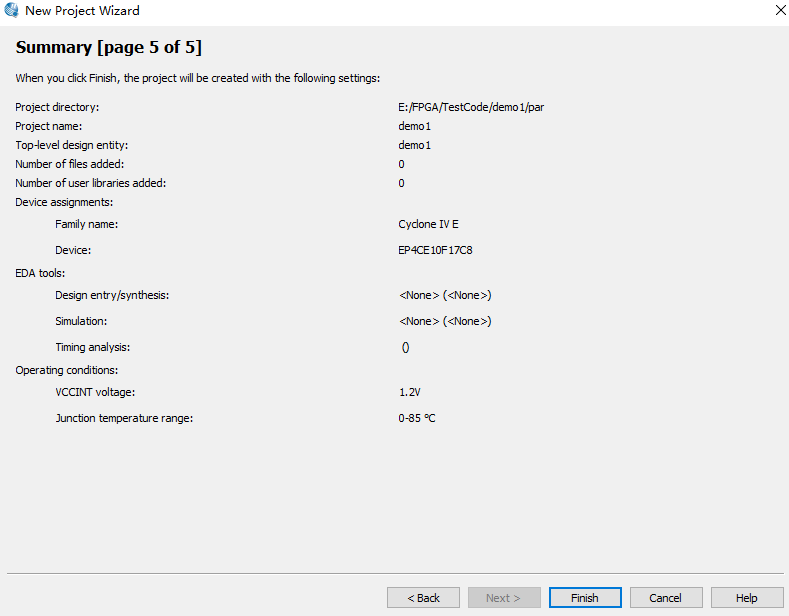

6、工程信息总览

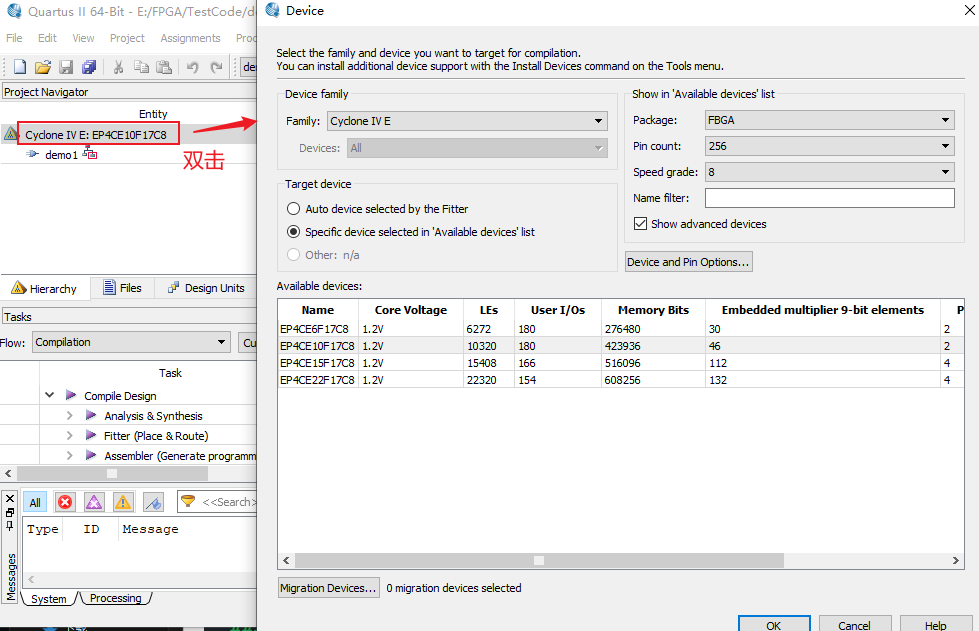

#、工程中修改芯片

双击工程文件导航中的芯片,进入修改窗体。

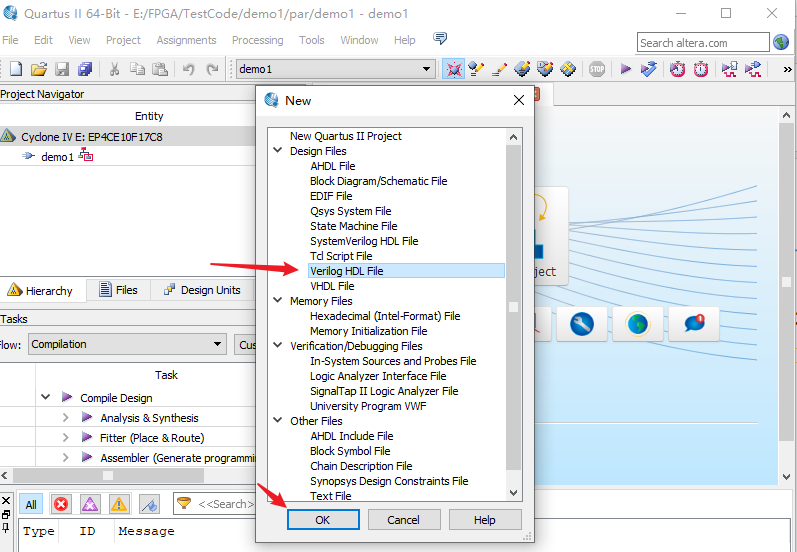

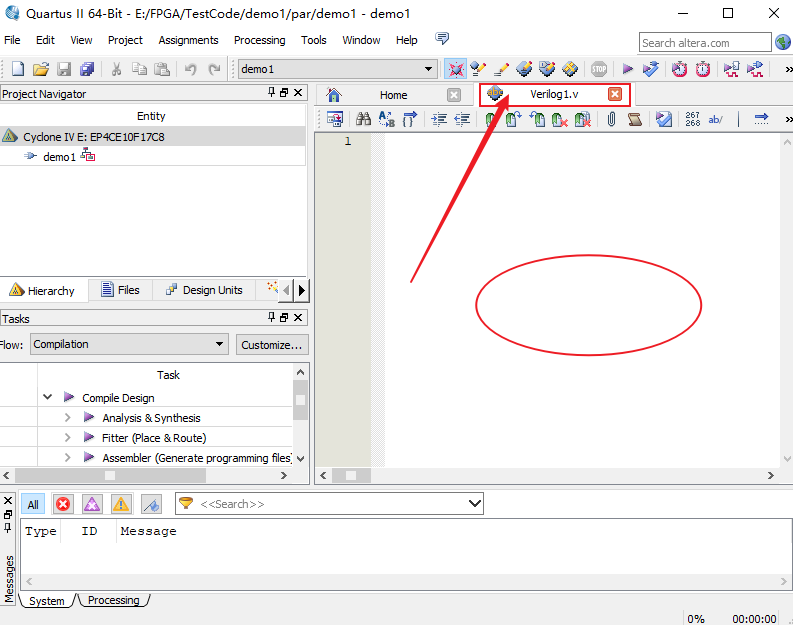

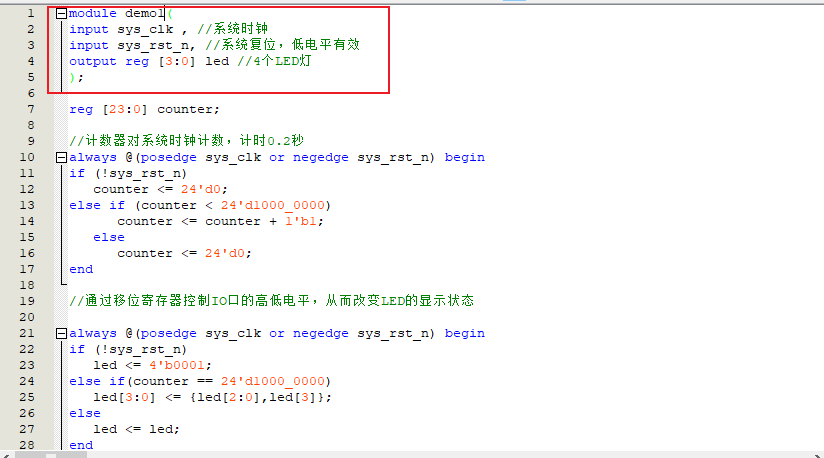

二、创建顶层文件

在新建工程基础上添加顶层文件,编辑代码

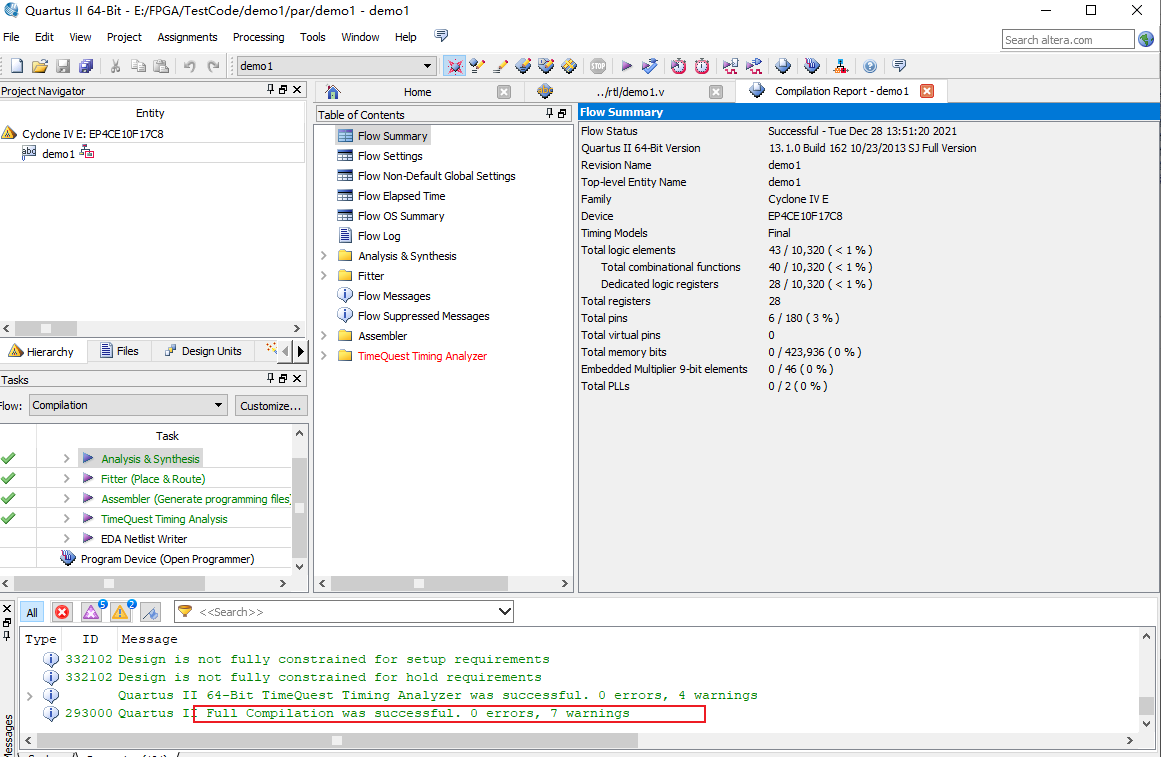

三、工程配置与编译

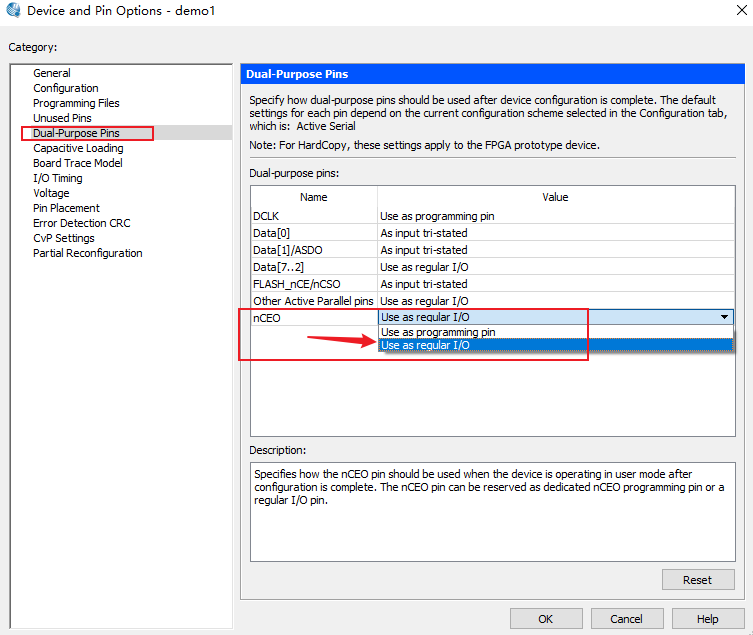

1、配置引脚

Dual-Purpose Pin中nCEO改为Use as regular I/0

注意文件进入点:一般与工程名一致,此处为demo1

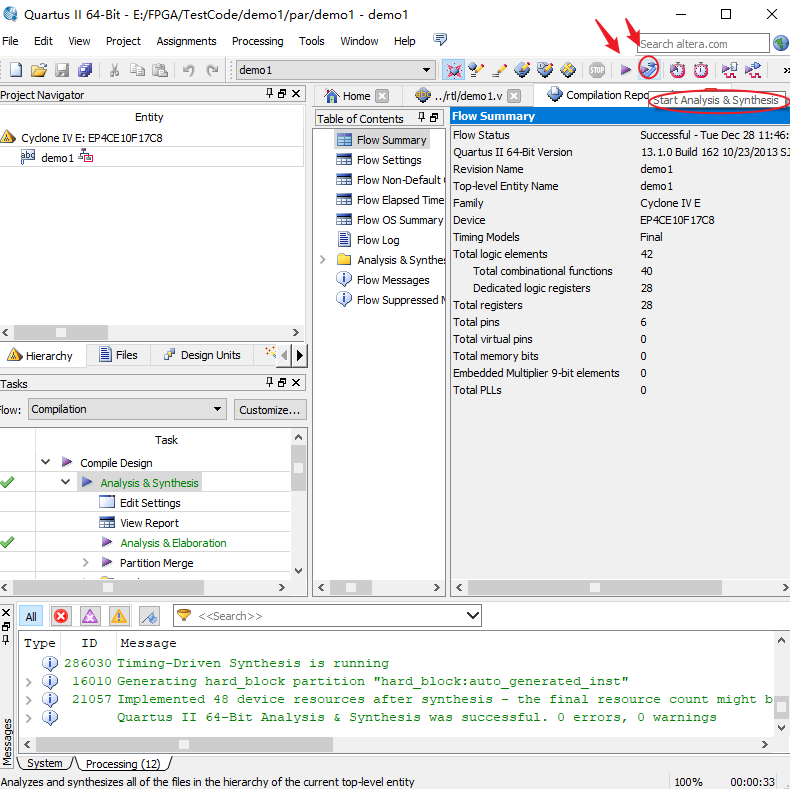

2、编译工程

检查语法 :Start Analysis & Synthesis

全编译 :Start Compilation

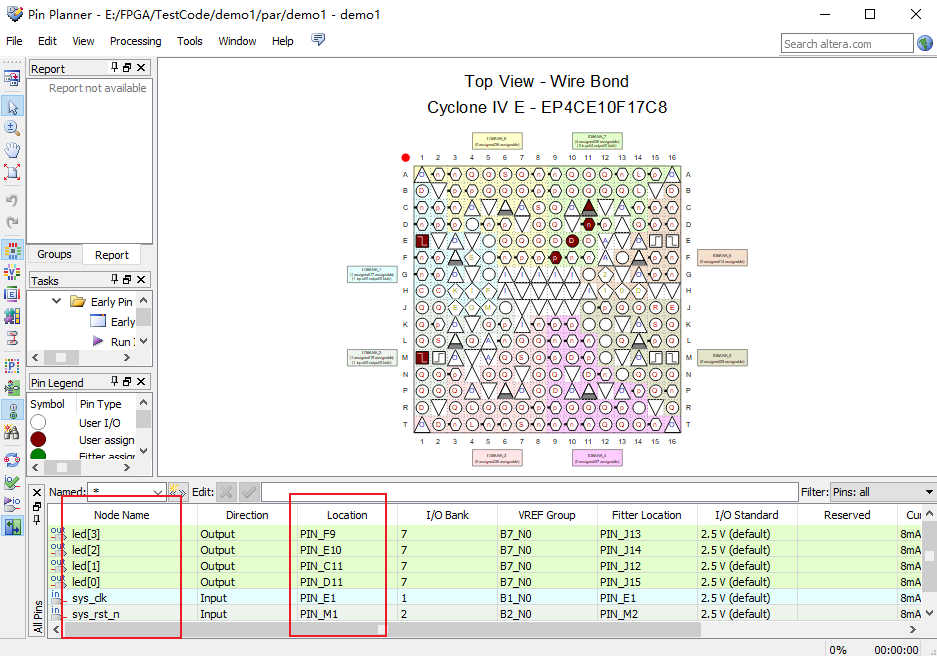

3、分配引脚

编译通过后,需要对输入输出端口进行管脚分配。

“菜单栏 -> Assignments -> Pin Planner”

完成分配后,在编译工程。

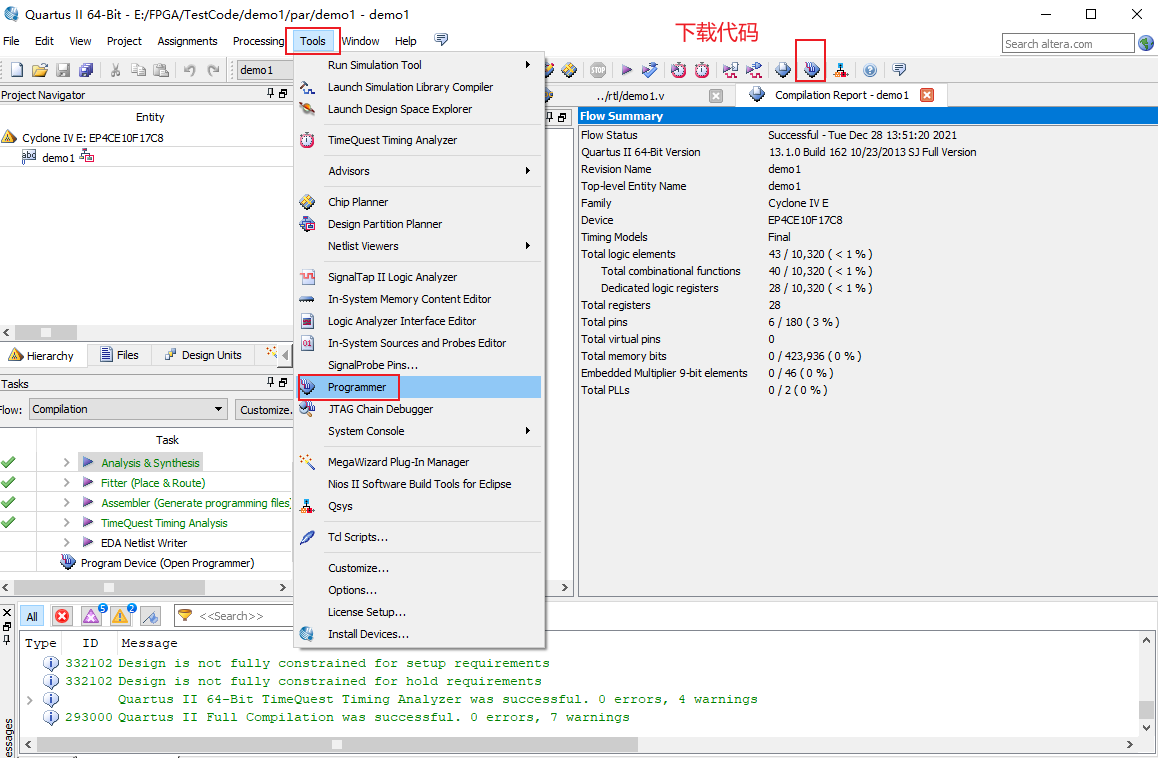

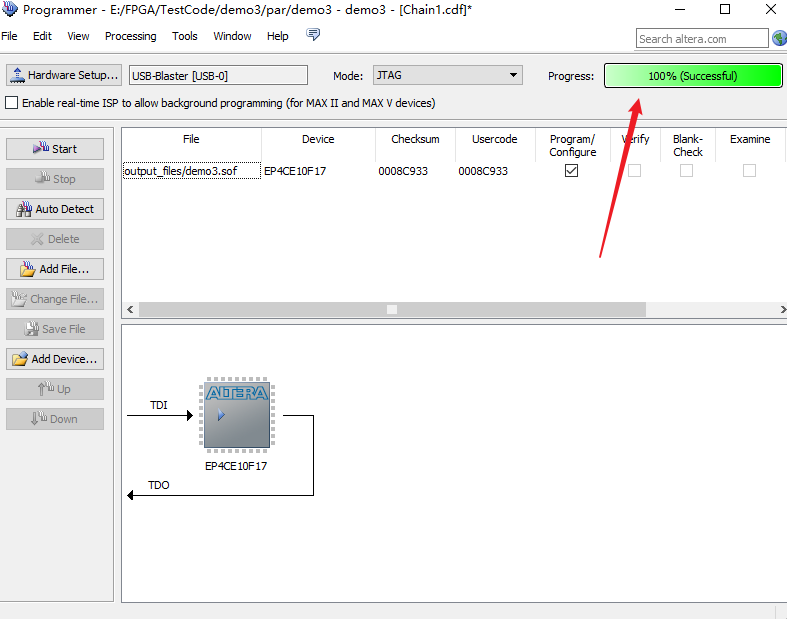

四、下载程序

1、进入烧录界面

2、选择烧录工具

“Hardware Setup” -> USB Blaster

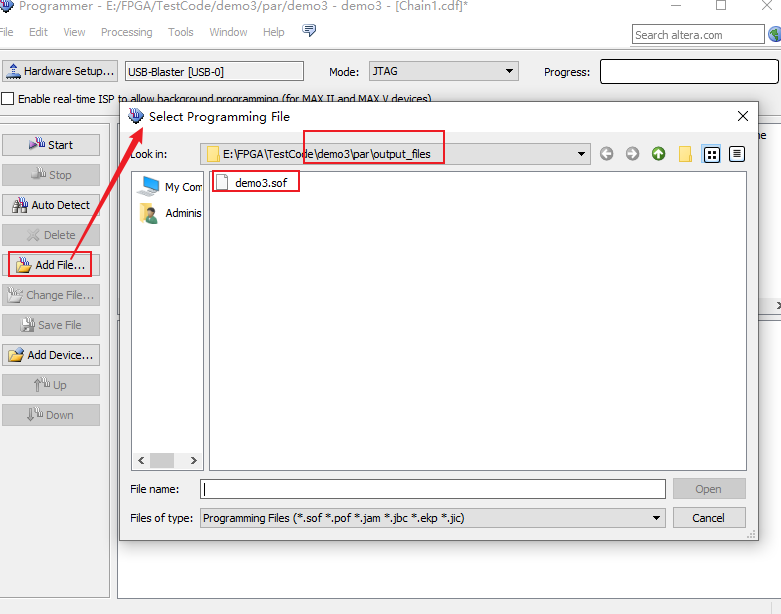

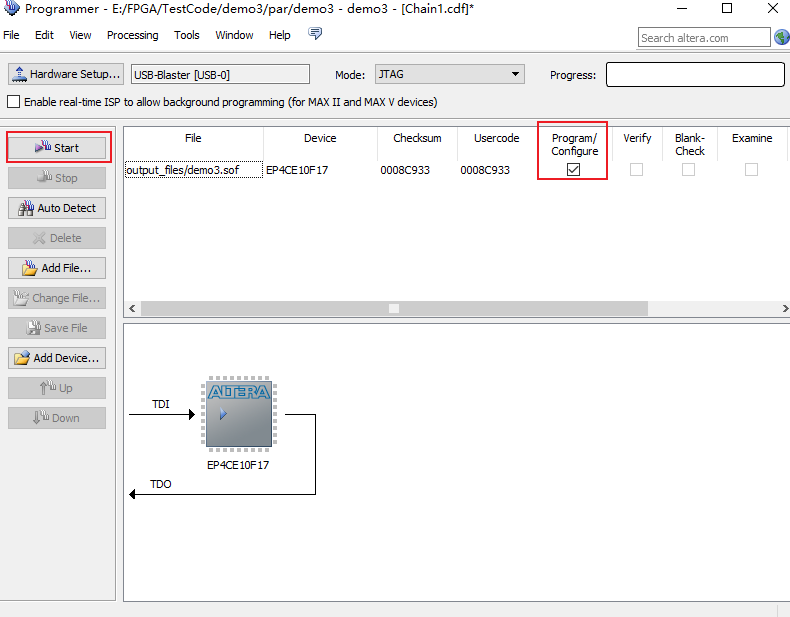

3、烧录sof文件(掉电不保存)

选中sof文件后,点击start,Program进度条满格。

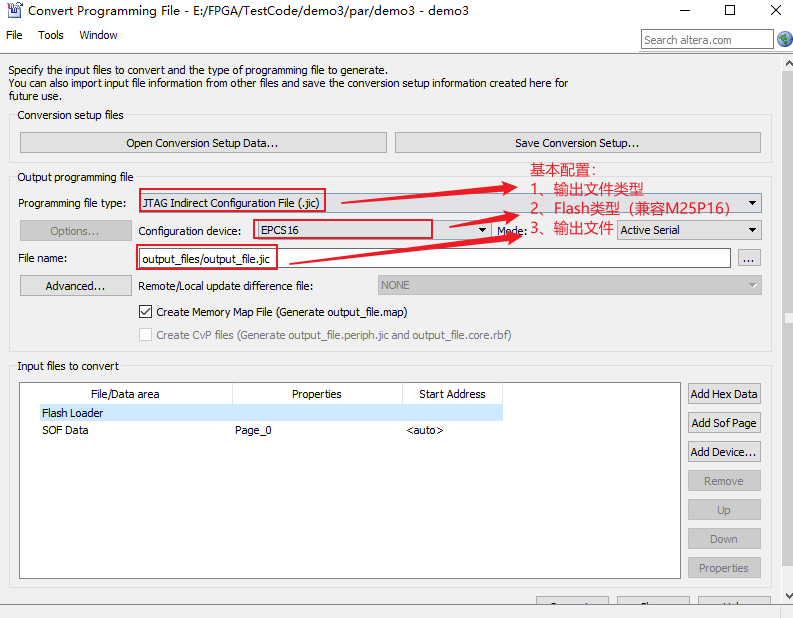

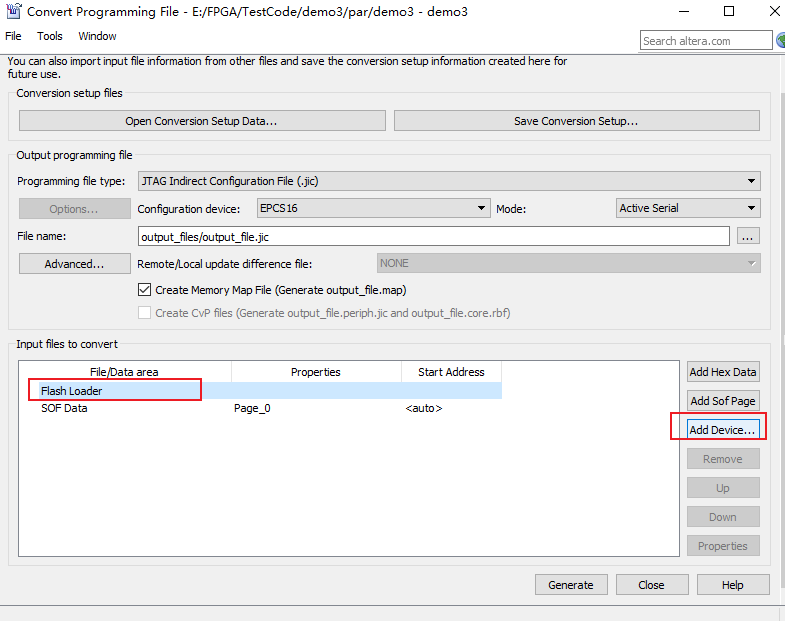

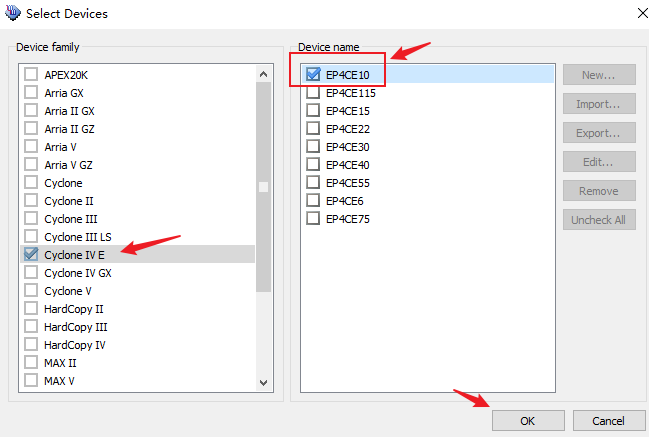

4、固化程序(掉电保存)

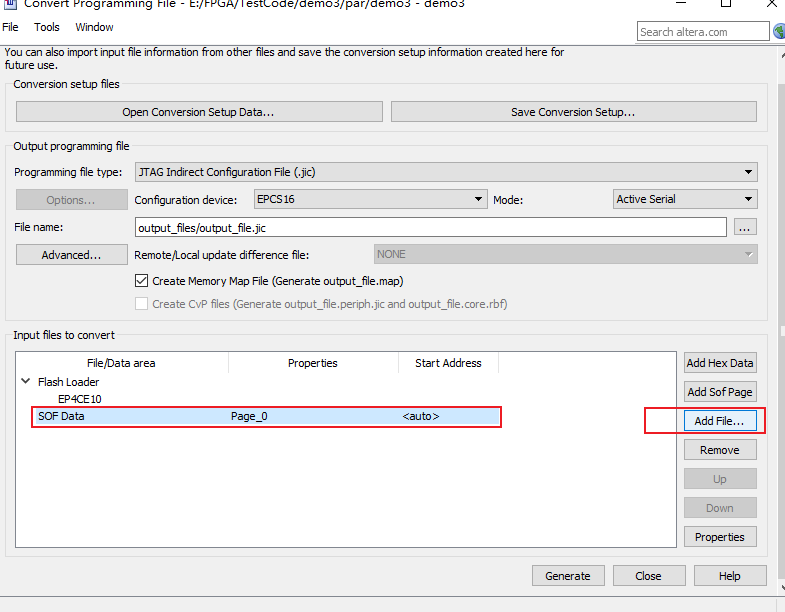

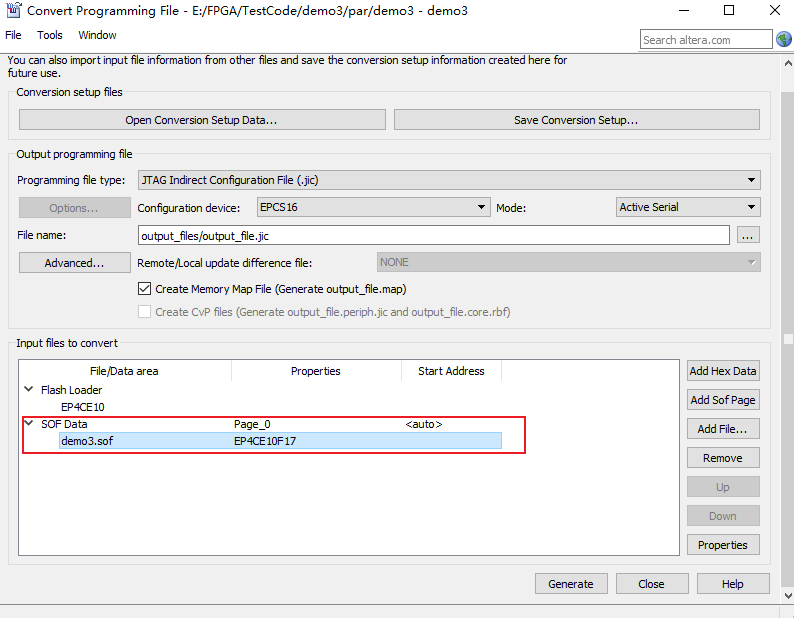

使用JTAG,转换为“.jic文件”

-

基本文件配置

-

选择目标芯片

-

选择待转换的.sof文件

-

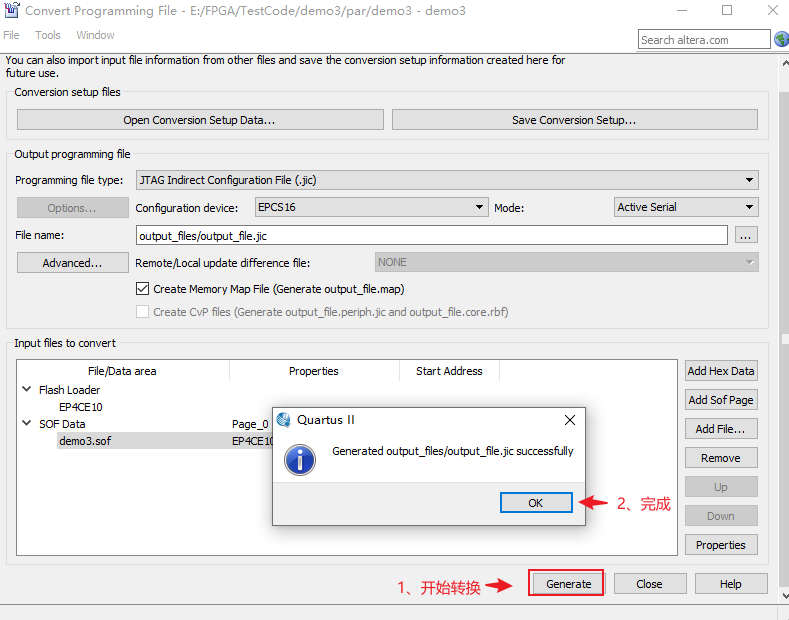

开始转换文件

-

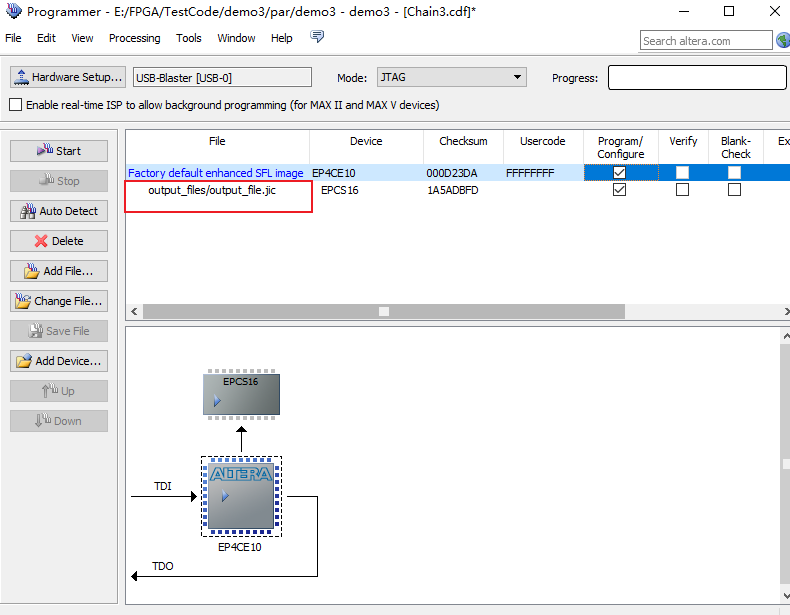

下载.jic文件

仿照“四、下载程序”烧录流程,烧录.jic文件即可

4269

4269

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?