前言

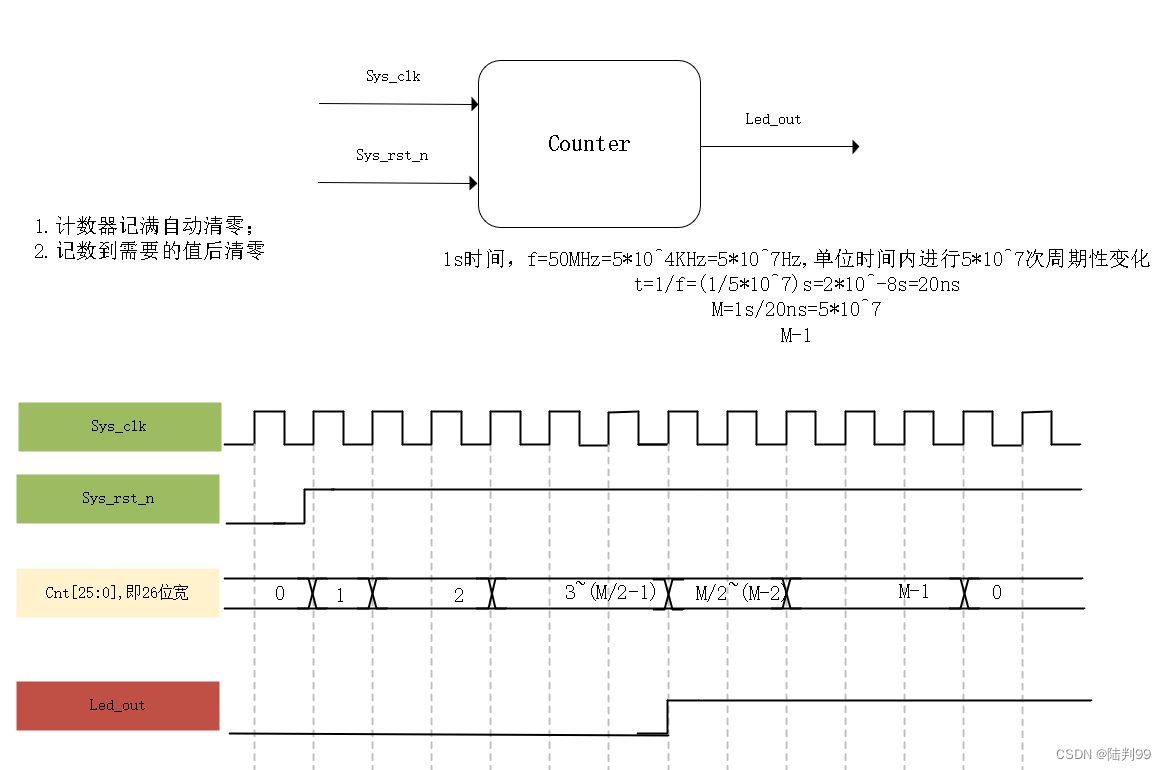

当cnt为49_999_999位时,转换为二进制26位宽。

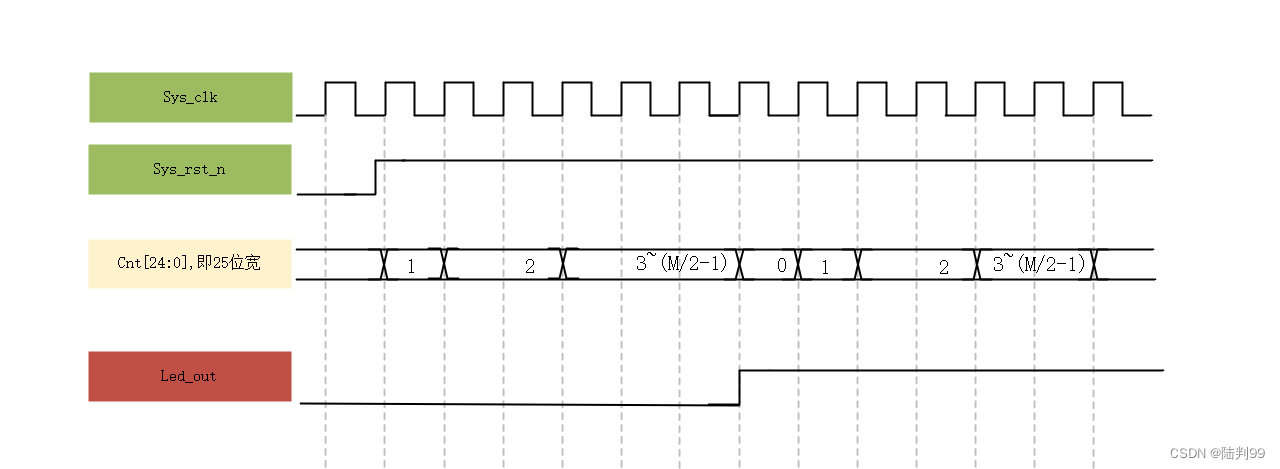

当cnt为29_999_999位时,转换为二进制25位宽,后续都采用第二种。

一、代码

1.rtl代码

代码如下(示例):

module counter

#(

parameter CNT_MAX =25'd24_999_999//不仅可以写在模块内部,还可以写在模块名称之后

)

(

input wire sys_clk,

input wire sys_rst_n,

output reg led_out

);

/* parameter CNT_MAX =25'd24_999_999;//不仅可以写在模块内部,还可以写在模块名称之后

localparam CNT_MAX =25

文章介绍了使用Verilog语言实现一个24,999,999位的计数器模块,该模块在计数值达到特定宽度时会重置,并提供了测试代码进行仿真验证。RTLViewer显示了设计的逻辑视图,仿真结果展示了计数器的正确功能。

文章介绍了使用Verilog语言实现一个24,999,999位的计数器模块,该模块在计数值达到特定宽度时会重置,并提供了测试代码进行仿真验证。RTLViewer显示了设计的逻辑视图,仿真结果展示了计数器的正确功能。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

4万+

4万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?