一、Transceiver Native PHY概述

Intel 的

FPGA Intel Cyclone 10 GX

器件提供多达

12

个收发器通道,集成了先进的高速模拟信号调理和时钟数据恢复技术。

Intel Cyclone 10 GX 器件包含可支持高达

12.5 Gbps

和高达

6.6 Gbps

数据速率的收发器通

道,分别应用于芯片到芯片与芯片到模块的通信和背板通信。通过过采样

(oversampling)

可以实现

低于

1.0 Gbps

的传输和接收数据速率。

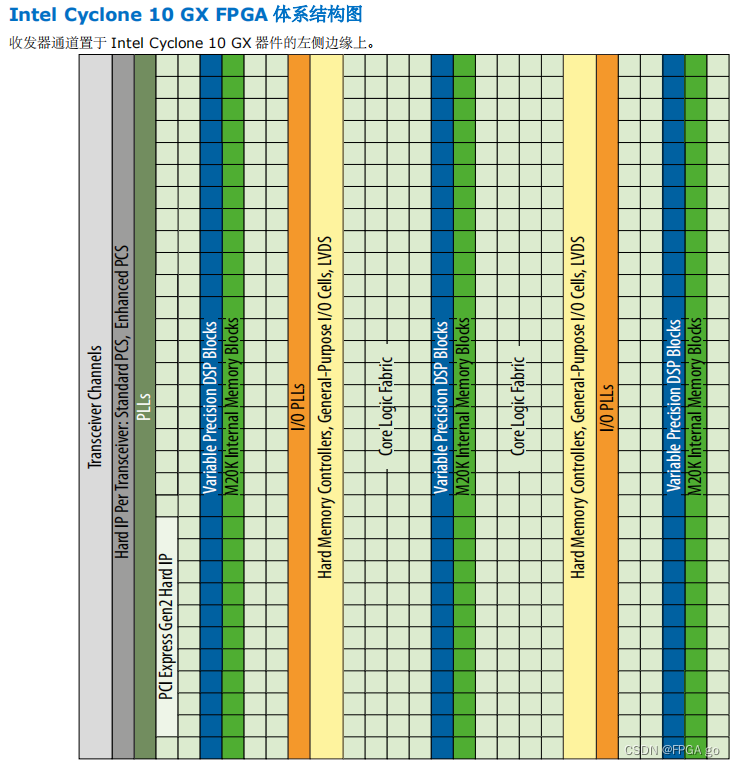

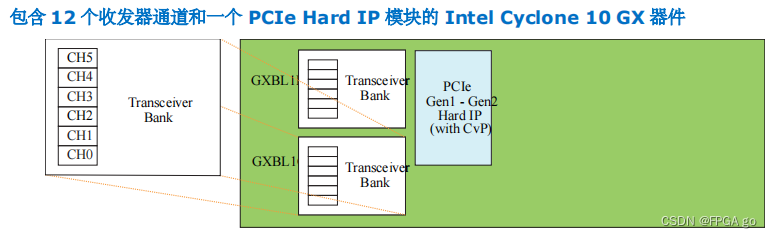

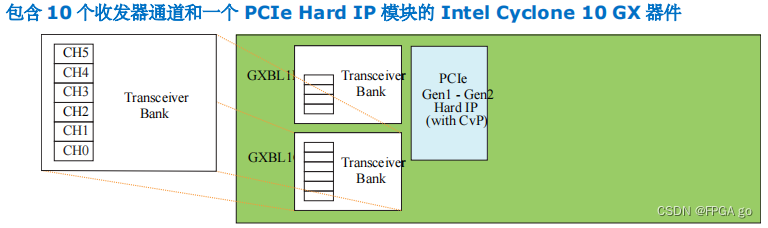

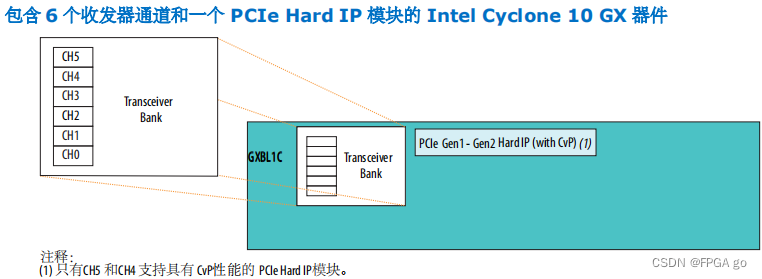

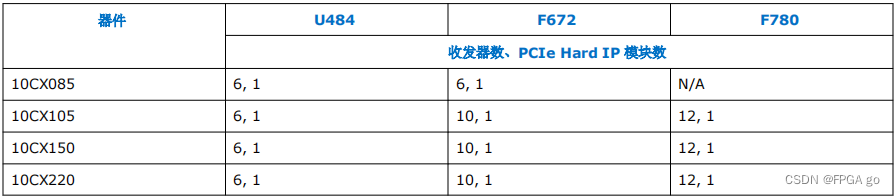

二、器件收发器布局

Intel Cyclone 10 GX 器件提供

6

,

10

或

12

个收发器通道。每个收发器

bank

有高达六个收发器通道。 Intel Cyclone 10 GX

器件还有一个嵌入式

PCI Express Hard IP

模块。

下图显示了

Intel Cyclone 10 GX GX

器件系列的不同收发器

bank

布局。

不同器件封装详情如下图:

三、收发器PHY体系结构概述

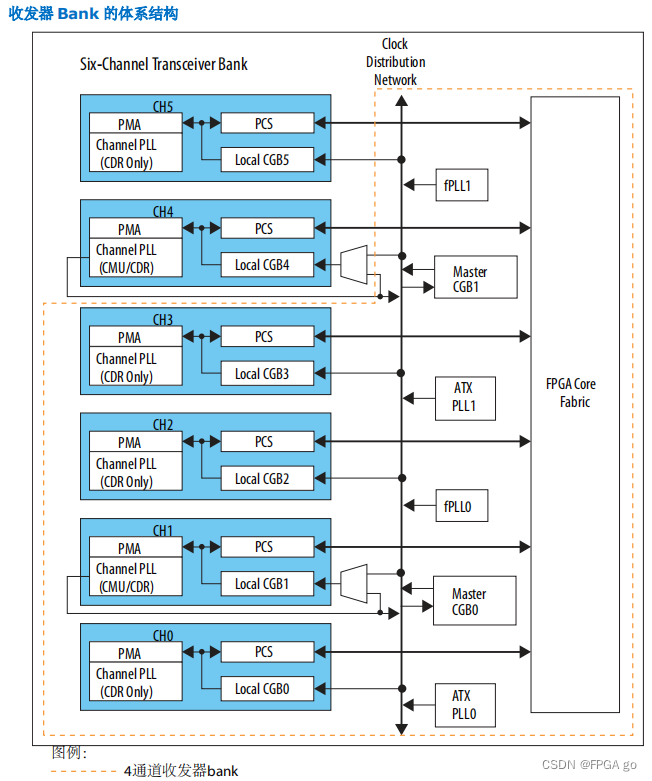

1.收发器bank体系结构:

收发器

bank 是一个基础单元,包含与器件的高速串行收发器相关的所有功能模块。 在所有器件中,每个收发器

bank 均包含四个或六个收发器通道。

下面几张图显示了在每个

bank

中可用锁相环

(PLL)

和时钟生成模块

(CGB)

资源的收发器

bank

的体系结构;

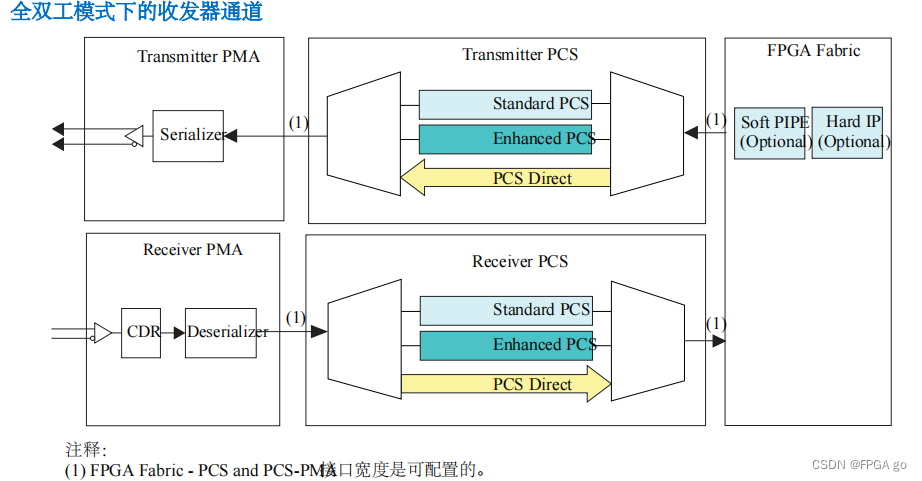

2.PHY层收发器组件:

Intel Cyclone 10 GX

器件中的收发器在物理

(PHY)

层既支持物理介质附加子层

(PMA)功能,也支持物理编码子层

(PCS)

功能:

PMA

是收发器用来与物理介质进行交互的电气接口。收发器

PMA

包含多个标准模块,例如:

• 串化器/

解串器

(SERDES)

• 时钟和数据恢复 PLL

• 模拟前端发送驱动器

• 模拟前端接收缓冲器

通过使用

PCS Direct

配置可旁路

PCS

。

PMA

模块和

PCS

模块均通过由高性能

PLL

驱动的多个时钟网络来馈送数据。在 PCS Direct

配置中,数据会流经

PCS

模块,但所有内部

PCS

模块都会被旁路。在这种模式下,PCS

功能在

FPGA

架构中实现。

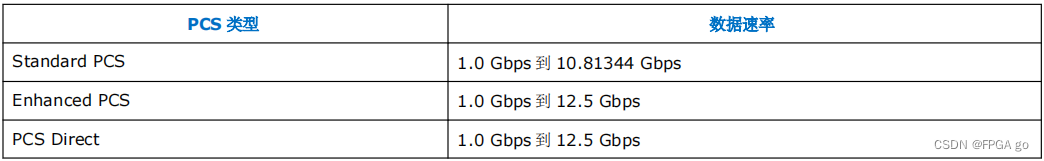

收发器通道:

Intel Cyclone 10 GX

收发器通道有三种类型的

PCS

模块,可支持介于

1.0 Gbps

与

10.81344

Gbps

之间的连续数据速率。

收发器通道所支持的PCS类型如下表

3.收发器锁相环

Intel Cyclone 10 GX

器件内的每个收发器通道都可以直接访问三种类型的高性能

PLL

:

• Advanced Transmit (ATX) PLL

• Fractional PLL (fPLL)

• Channel PLL / Clock Multiplier Unit (CMU) PLL

这些收发器

PLL

与

Master

或者

Local Clock Generation Blocks (CGB)

共同驱动收发器通道。

高级发送(ATX)PLL

高级发送

(ATX) PLL

是一种高性能

PLL

,只支持整数频率综合。

ATX PLL

是收发器通道的主要发送

PLL

。它能够以高数据速率应用场合所需的各种支持的数据速率运行。

小数分频 PLL (Fractional PLL (fPLL))

小数分频

PLL (fPLL)

是一种备用发送

PLL

,为高达

12.5 Gbps

数据速率的应用生成时钟频率。

fPLL

既支持整数频率综合,也支持精细分辨率小数频率综合。与

ATX PLL

不同的是,

fPLL

可用于

综合各种可通过

FPGA

架构时钟网络来驱动内核的频率。

通道 PLL (CMU/CDR PLL)

通道

PLL

位于本地的每个收发器通道中。它的的主要功能是在

PLL

用于时钟和数据恢复

(CDR)

模式时对收发器通道内的时钟和数据进行恢复。当通道 1

和通道

4

的通道

PLL

在时钟乘法器单元

(CMU)模式下配置时可用作发送 PLL

。通道

0

、

2

、

3

和

5

的通道

PLL

不能在

CMU

模式下配置,因此不能用作发送 PLL

。

4.时钟生成模块(CGB)

在

Intel Cyclone 10 GX

器件中,有两种类型的时钟生成模块

(CGB)

:

• Master CGB(主

CGB)

• Local CGB(本地

CGB)

包含六个收发器通道的收发器

bank

有两个主

CGB

。主

CGB1

位于收发器

bank

的顶端,主

CGB0位于收发器 bank

的底端。主

CGB

会将

bonded

时钟划分并分配到一个

bonded

通道组中。它还会将 non-bonded 时钟分配到整个 x6/xN 时钟网络中的 non-bonded 通道中。

收发器

每个收发器通道都有一个本地 CGB

。该本地

CGB

用于将

non-bonded

时钟划分并分配到它自己的PCS 和

PMA

模块中。

四、校准

Intel Cyclone 10 GX FPGA

包含一个用来补偿过程偏差

(process variations)

的专用校准引擎。该校准引擎可校准收发器的模拟部分,从而使发送器和接收器都能以最佳性能运行。

CLKUSR

管脚对校准引擎提供时钟。为了成功完成校准和实现最佳的收发器性能,所有收发器参考时钟和 CLKUSR

时钟都必须在

FPGA 配置开始时是自由运行的并保持稳定。(CLKUSR 电气特征参阅Intel Cyclone 10 GX 器件数据表、

Intel Cyclone 10 GX

内核架构和通用

I/O 手册、

Intel Cyclone

10 GX

器件系列管脚连接指南

)

990

990

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?