【转载】掌握了CDC,你听说过RDC吗 - 极术社区 - 连接开发者与智能计算生态 (aijishu.com)

【重点标出】

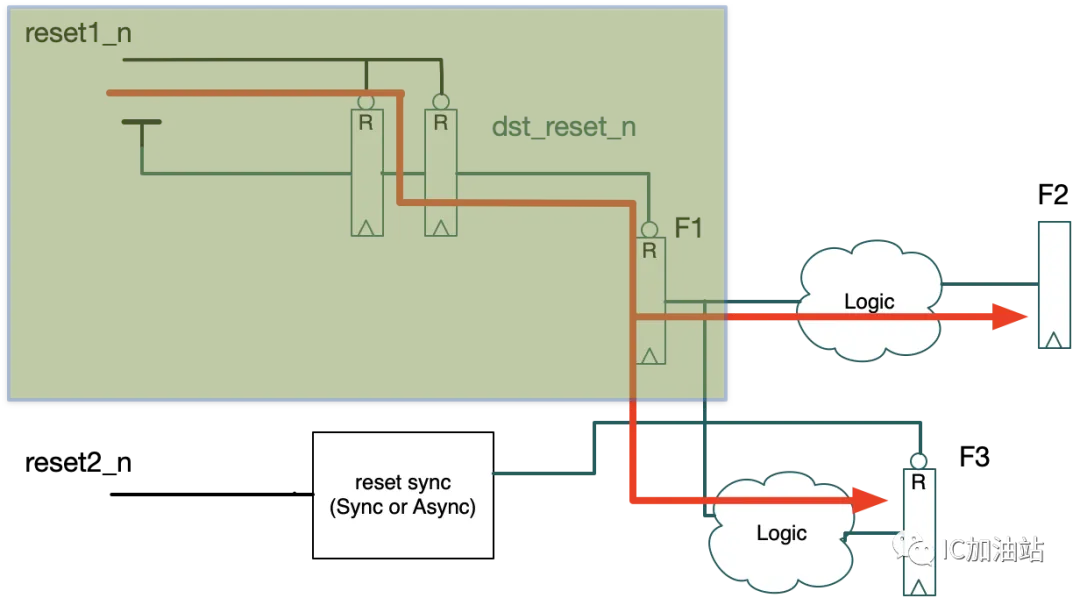

在上面这个图中,我们有2个reset,分别是reset1_n和reset2_n。其中flop F1是被reset1_n给异步reset的。而F3是被reset2_n给异步reset的。F2可能是被同步reset给复位,也可能没有reset。而这其中,F1是F2和F3的控制逻辑的fan-in,也就是说F1的变化会影响到F2和F3的值。

那么考虑这种情况,reset1_n assert了,但是reset2_n并没有assert,F3和F2依然工作在正常模式,并没有被复位,那么会发生什么情况呢?结果可能很糟糕,即F2和F3会产生metastability,导致芯片发生逻辑错误。你可能会说,老李不对啊,这里又没有跨时钟域,哪来的metastability? 注意看,因为reset1_n对F1是异步reset,也就是说,当reset1_n assert,F1立马会被reset,F1的Q立刻会发生变化。而我们说,asynchronous reset 的assertion是可以在任何时间的,不然就不叫asynchronous 了,它和时钟沿没有关系,甚至与有没有时钟都没有关系,换句话说,F1的Q变成reset值可以发生在任何时候!那么F2和F3的D输入经过那一堆组合逻辑,就可能在任何时候产生变化,如果这个变化恰好落在F2和F3的setup/hold window里,那不就导致了setup/hold time violation, 从而产生了亚稳态吗?

你可能还是有点将信将疑,难道F1的Q和F3的D,F1的Q和F2的Q之间不是有STA来做timing check的吗?在timing都满足的情况下怎么还会有setup/hold timing violation? 你没有说错,如果F1, F2, F3确实都处在同一个时钟域,STA的确会做register to register的timing closure,但是注意,STA能够做的,是分析从F1的Tclk2q 再加上Tcombo是不是满足register to register的setup/hold。STA 是无法做reset to q 再加上Tcombo的check的,还是那个原因,asynchronous reset的assertion是可以任何时间来的,所以没有办法做STA。(注意,reset de-assertion是和时钟沿对齐的,所以reset de-assertion是会做STA的)。也就是说,图上红色的timing path其实是unconstrained。

1533

1533

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?