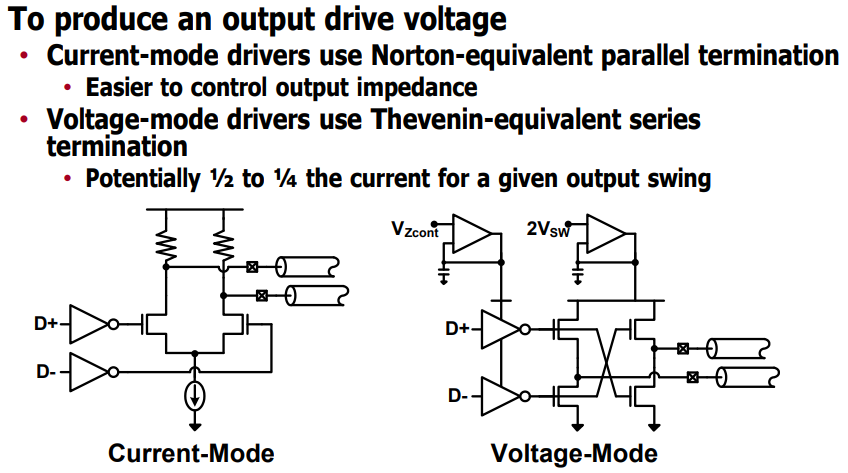

1、Current-mode drivers VS Voltage-mode drivers

2、CML(Current Mode Logic)

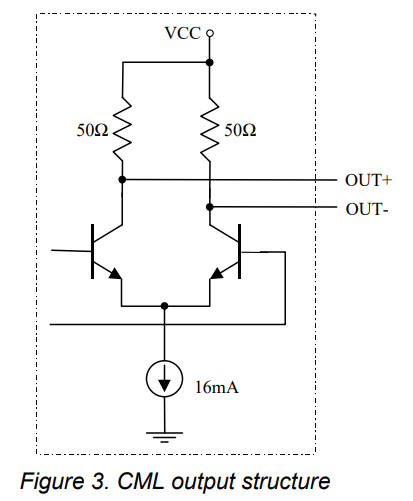

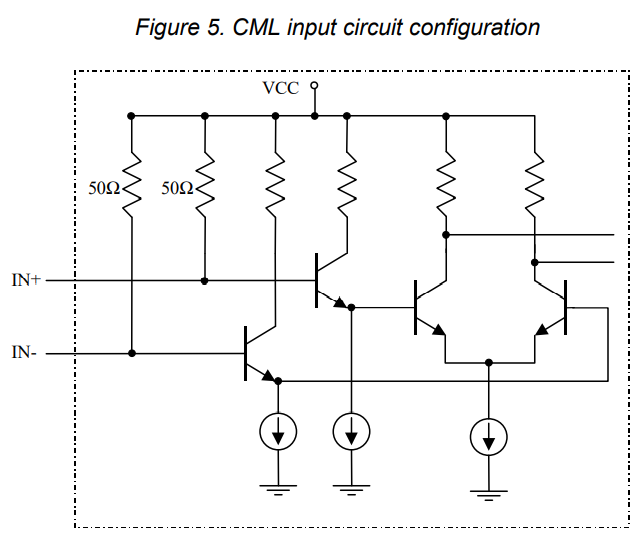

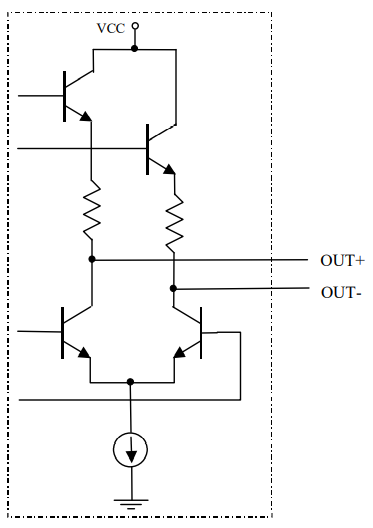

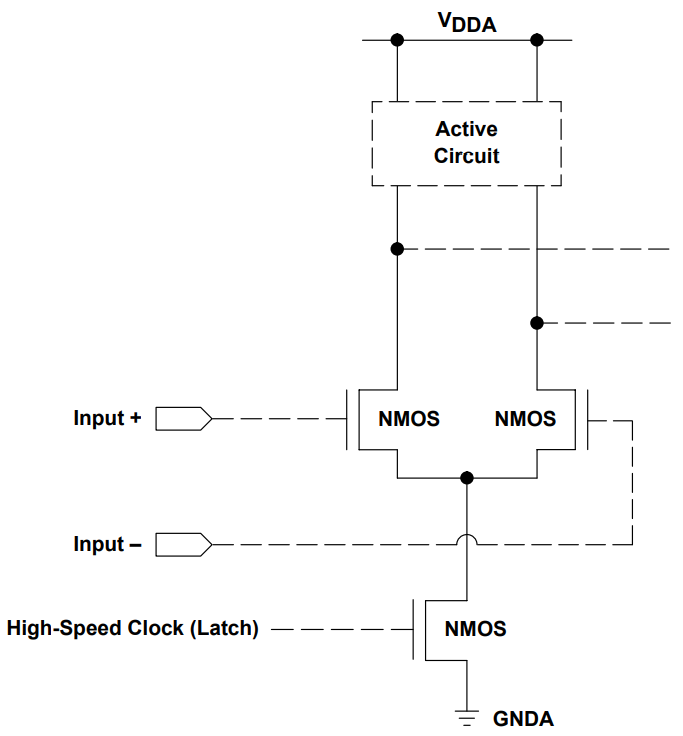

CML drivers that are built from an open-drain differential pair and a voltage-controlled current source using NMOS transistors.

The outputs (Output+ and Output–) require pullup resistors to VDD because the NMOS transistor can drive only falling edges efficiently and needs the pullups to help drive rising edges.

The output voltage swing is load dependent.

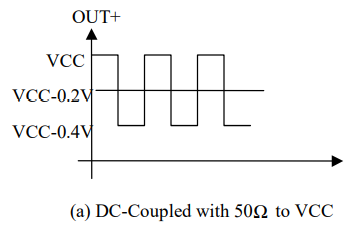

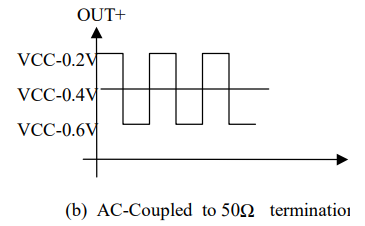

| 单端P或N: 高电平:VCC 低电平:VCC - 16mA *(50//50)= VCC - 0.4V Note:输出端和输入端50欧姆并联。 差分P-N: 高电平:VCC - (VCC - 0.4V) = 0.4V 低电平:(VCC - 0.4V) - VCC = - 0.4V 摆幅Swing = 0.4 - (-0.4) = 0.8V |

| 交流耦合的偏置电压取决于输入端,传过去的只是摆幅 所以,左图只是一个个例! |

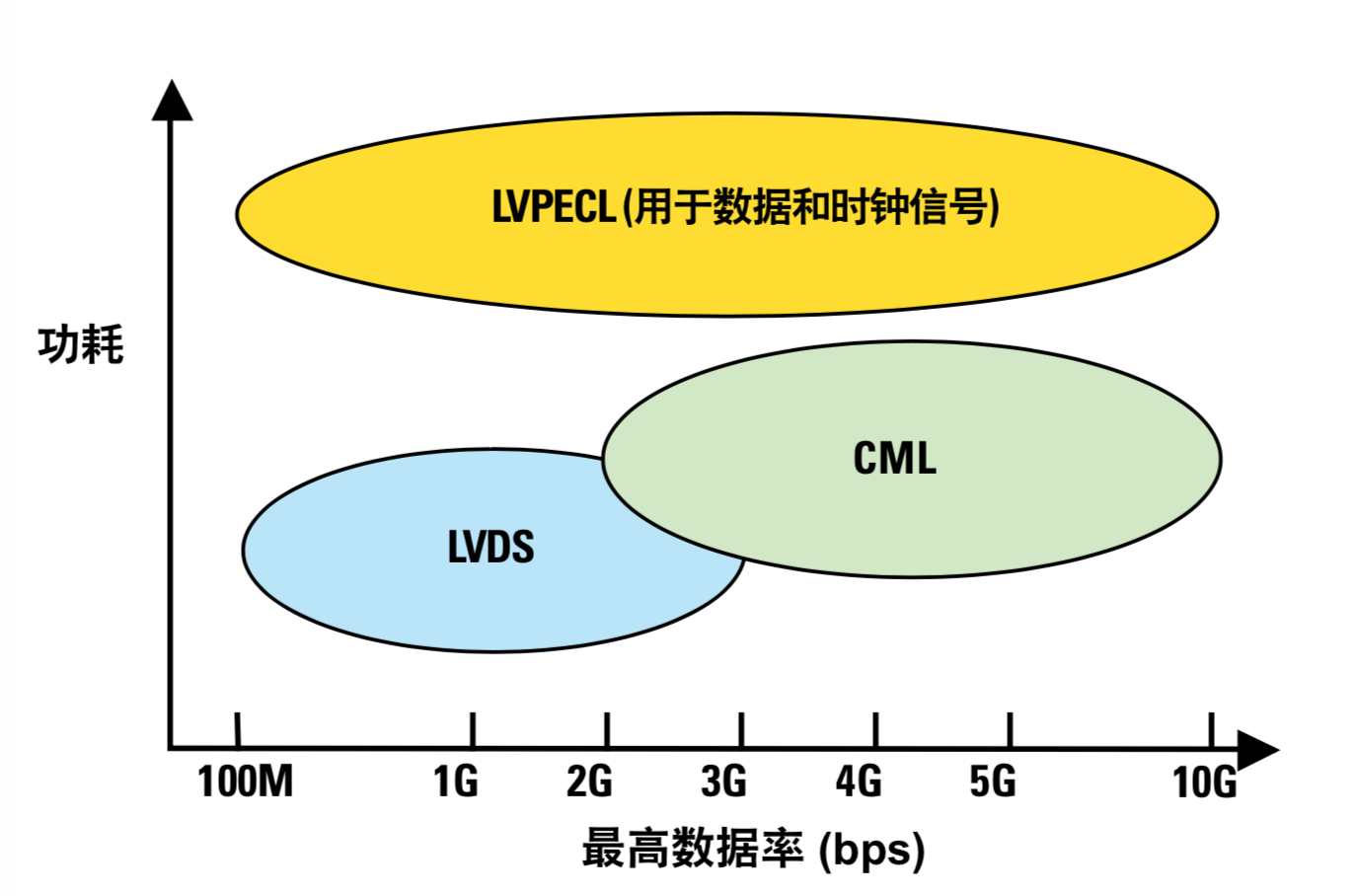

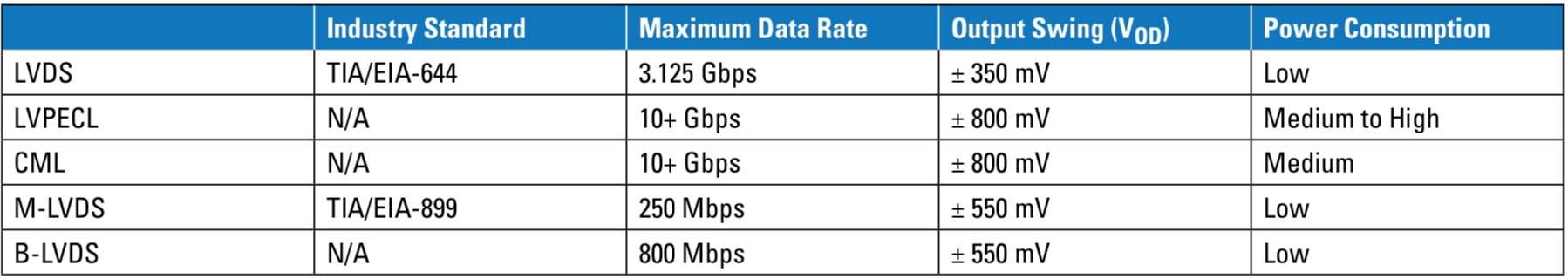

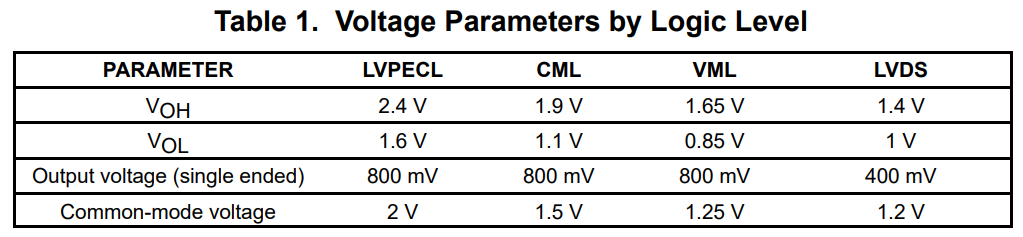

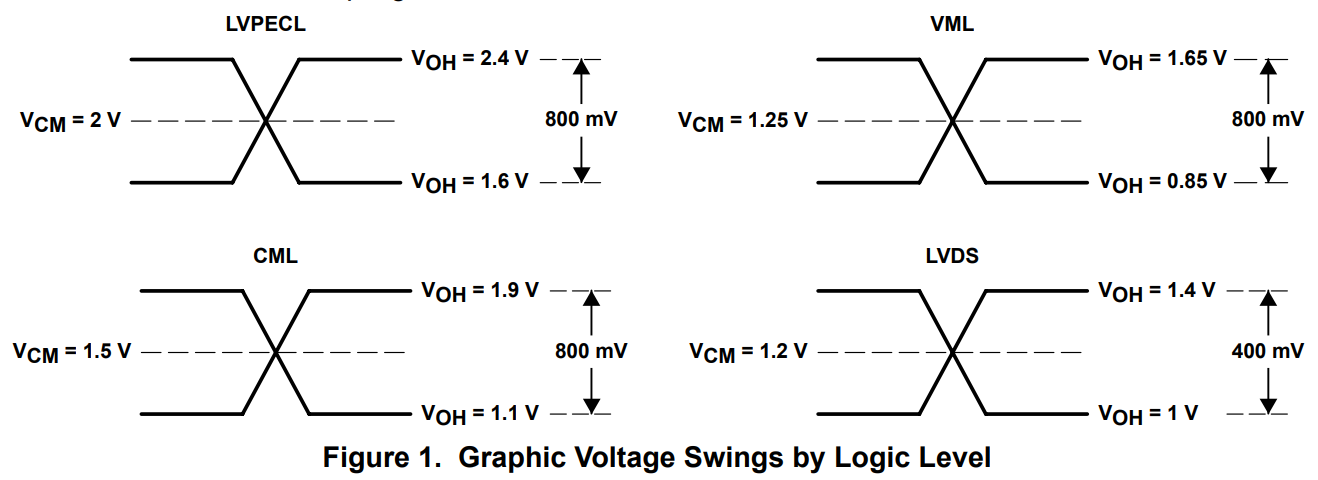

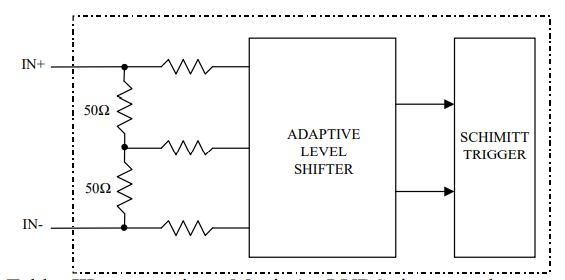

3、LVDS(Low Voltage Differential Signals)

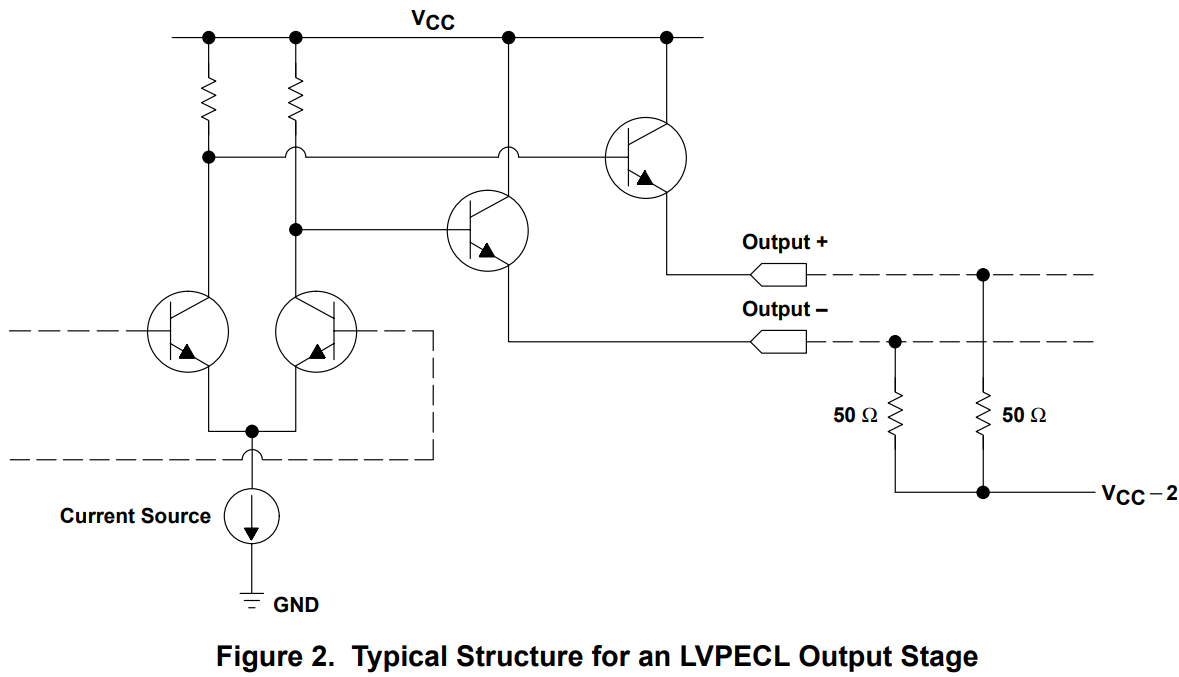

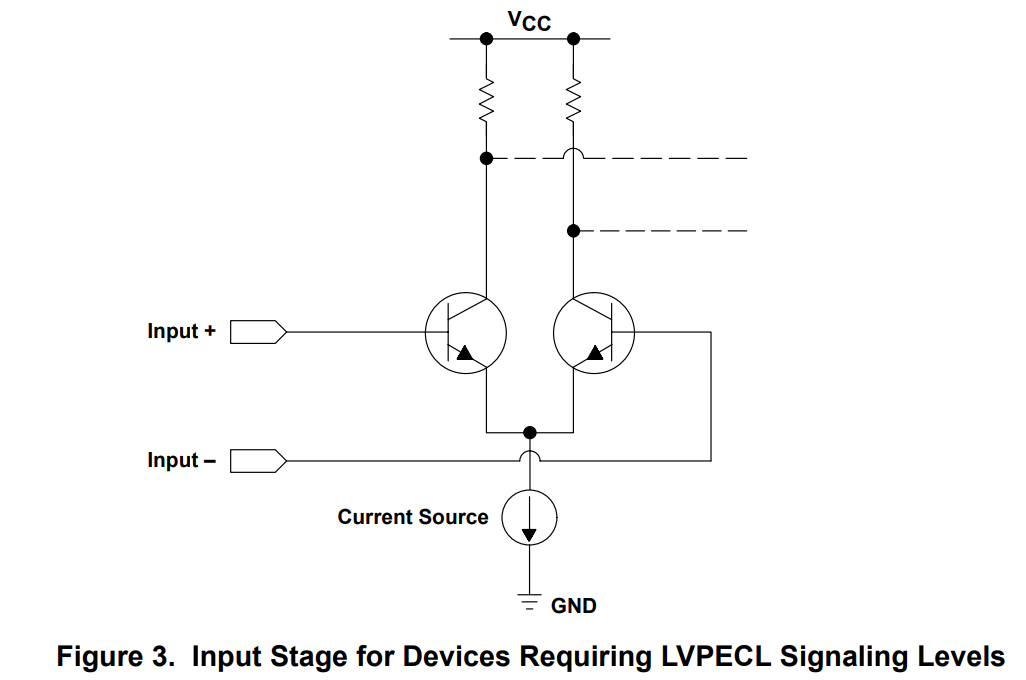

4、LVPECL(Low Voltage PECL)

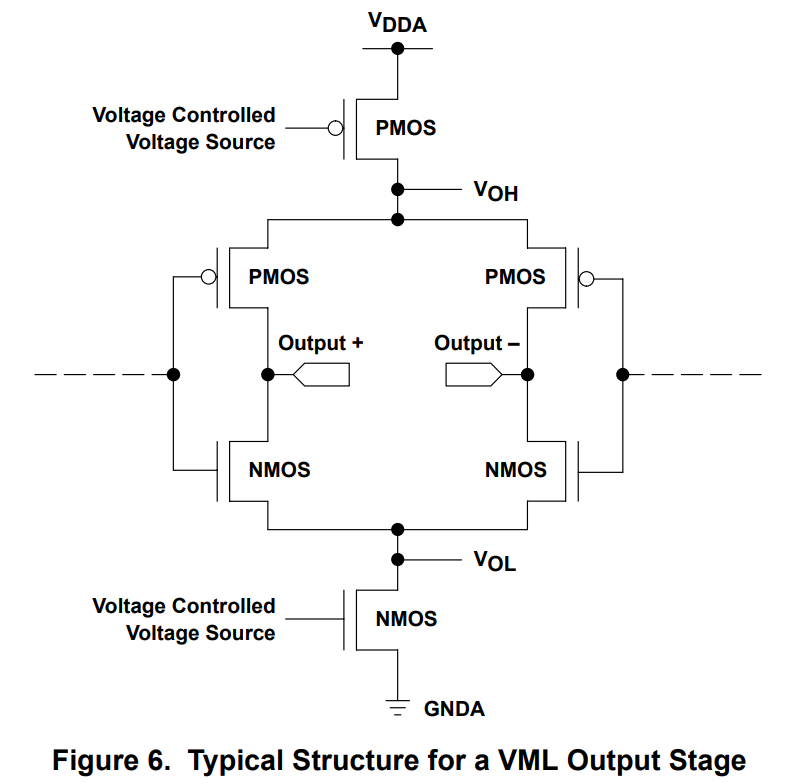

5、VML(Voltage Mode Logic)

The output swing of VML interfaces is independent of the load impedance.

6、互连

6.1、DC Coupling

6.2、AC Coupling

本文介绍了电流模式驱动器(CML)和电压模式驱动器(VML)的区别,CML驱动器依赖于NMOS晶体管和上拉电阻来驱动信号。LVDS、LVPECL和VML接口的输出摆幅不受负载阻抗影响。在互连技术中,讨论了直流耦合和交流耦合的应用。文章还涉及了在不同逻辑电平(如LVPECL、VML、CML和LVDS)之间的接口问题。

本文介绍了电流模式驱动器(CML)和电压模式驱动器(VML)的区别,CML驱动器依赖于NMOS晶体管和上拉电阻来驱动信号。LVDS、LVPECL和VML接口的输出摆幅不受负载阻抗影响。在互连技术中,讨论了直流耦合和交流耦合的应用。文章还涉及了在不同逻辑电平(如LVPECL、VML、CML和LVDS)之间的接口问题。

3万+

3万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?