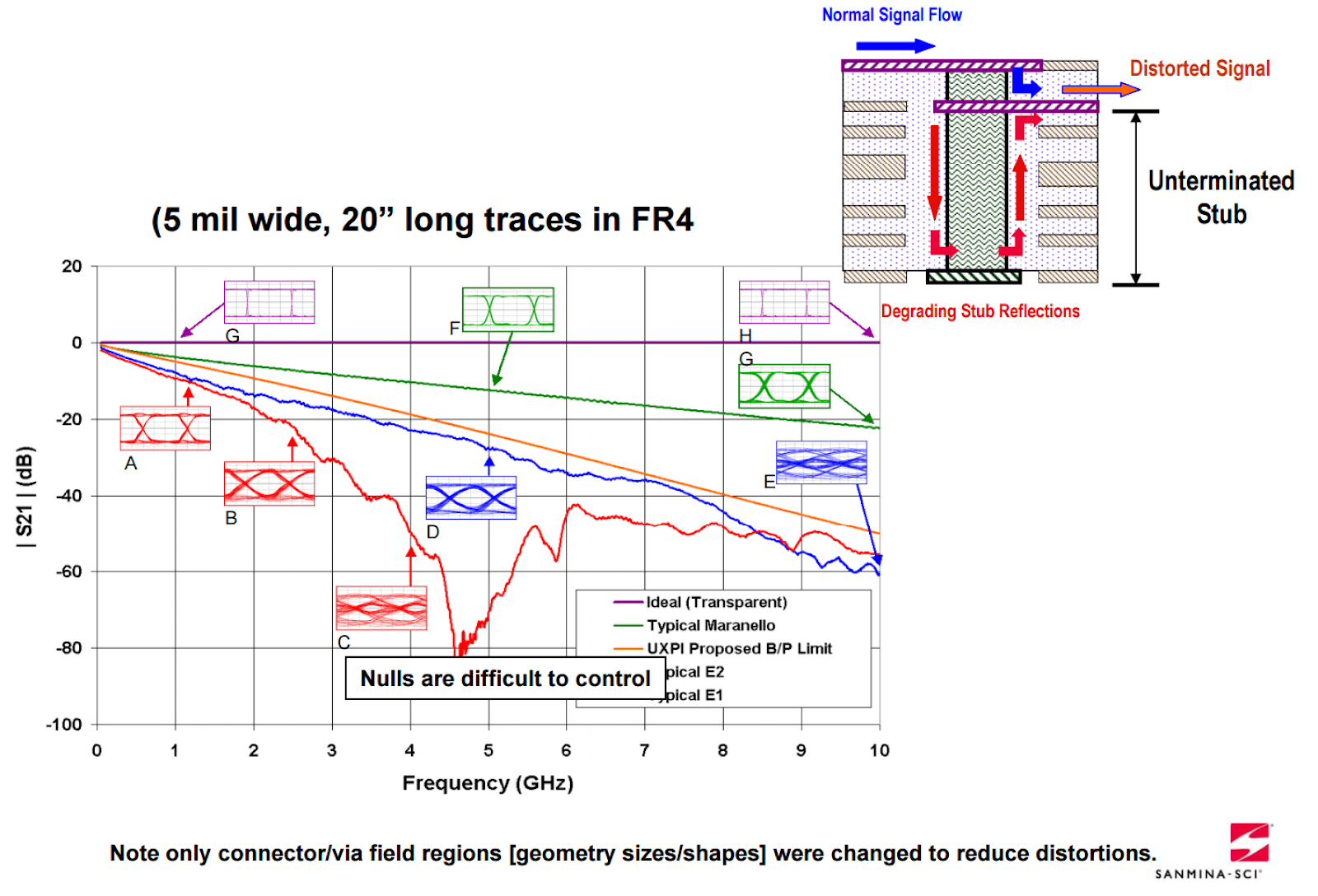

多年来,工程师们已经开发出多种方法来处理印刷电路板背钻设计中可能扭曲高速数字信号完整性的噪声。随着我们的设计不断突破新的界限,我们应对新挑战的技术复杂性也在不断提高。如今,数字设计系统的速度以 GHz 为单位,这一速度带来的挑战比过去更为突出。由于边缘速率为皮秒,任何阻抗不连续、电感干扰或寄生电容都会对信号完整性和质量产生不利影响。虽然有各种来源可能导致信号干扰,但有一种特定的来源有时会被忽视,那就是通孔。请继续阅读以了解有关如何减少 PCB 信号失真的更多信息。

简易通道中的隐患

高密度互连 (HDI)、高层数印刷板和厚背板/中板中的过孔信号可能会遭受额外的抖动、衰减和更高的比特误码率 (BER),从而导致接收端对数据进行误解。

以背板和子卡为例。当谈到阻抗不连续性时,电路板的焦点通常是它们与主板之间的连接器。通常情况下,这些连接器的阻抗匹配得很好,不连续性的实际来源是 PCB 设计通孔。

随着数据速率的增加,镀通孔 (PTH) 过孔结构引入的失真量也会增加 – 通常呈指数增长,远高于相关数据速率的增加。例如,6.25 Gb/s 数据速率下镀通孔产生的失真效应通常是 3.125 Gb/s 的两倍多。

底部和顶部的不必要的短截线延伸到其最后连接的层之外,使通孔看起来像低阻抗不连续点。工程师克服这些通孔额外电容的一种方法是尽量缩短它们的长度,从而降低它们的阻抗。这就是背钻的作用所在。

利用背钻进行备份

背钻是一种广泛接受的简单有效方法,通过移除过孔短截线来最大限度地降低通道信号完整性。这种技术被称为受控深度钻孔,使用传统的数控 (NC) 钻孔设备。这种技术可以应用于任何类型的电路板,而不仅仅是背板等厚电路板。

背钻工艺需要使用直径略大于原始通孔直径的钻头来去除不需要的导电短线。该钻头通常比主钻头大 8 密耳,但许多制造商可以满足更严格的规格。

必须记住,走线和平面间隙必须足够大,这样背钻过程才不会钻穿靠近背钻通孔的走线和平面。为避免钻穿走线和平面,建议间隙为 10 mil。

一般来说,通过背钻减少过孔残端长度有许多优点,包括:

-

将确定性抖动降低几个数量级,从而降低 BER。

-

由于阻抗匹配改善而减少信号衰减。

-

减少来自短截线端和信道带宽放大器的 EMI/EMC 辐射。

-

减少谐振模式的激发和通孔到通孔的串扰。

-

与顺序层压相比,以更低的制造成本最大限度地减少设计和布局影响。

-

背钻横截面

背钻横截面传达背钻意图

随着背钻技术在高密度互连和高速设计应用中越来越频繁地使用,这种做法带来的可靠性问题也越来越多。导致这种情况的一些问题包括缺乏设计指南、制造公差以及确保在制造包中将设计意图很好地传达给制造商。

那么,您如何确保制造商拥有成功背钻电路板上所有目标过孔和 PTH 元件所需的全部信息?您如何在整个设计过程中跟踪多层背钻规范?

您需要的是一个集成到设计规则中的简单、可视化的配置工具,它使您能够为选定的对象指定不同的背钻配置。之后,您只需让软件为您完成工作,了解哪些过孔需要背钻。看看 Altium Designer ®中的背钻是多么简单。

参考:

[1] Dudnikov, George 和 Vladimir Duvanenko。“匹配终端短截线 VIA 技术可实现线路卡和背板中的更高带宽传输。”所有商标和注册商标均归其各自所有者所有。摘要 (nd):n. 页。匹配终端短截线 VIA 技术可实现线路卡和背板中的更高带宽传输。Sanmina - SCI,2008 年。网络。2016 年 9 月 9 日。

6095

6095

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?