当我们设计 PCB 时,我们首先在 EDA 工具中设置面向制造设计 (DFM) 规则。然而,信号完整性规则可能是我们最后考虑的事情。在本博客中,我们将探讨如何将面向信号完整性的设计 (DFSI) 纳入我们的 DFM 例程。

面向制造的设计

在讨论 DFSI 之前,让我们先回顾一下 DFM 标准。DFM 最重要的标准来自 PCB 的 IPC 分类:1 级、2 级或 3 级。IPC 1 级适用于只需整体工作的 PCB。可能会有裂缝或钻头放错位置,但如果能正常工作,那就没问题了。这类 PCB 可用于廉价手电筒、儿童玩具和车库门开启器等。IPC 2 级适用于不仅可以工作,而且可以连续使用几年的电子产品。这些类型的 PCB 可用于高端电子产品,如您的 Playstation 或 Xbox、用于网络的电子系统或 GPU 板。IPC 3 级适用于即使在恶劣环境下也必须工作的应用。这些包括军事应用、心脏起搏器等医疗设备或用于太空旅行的 PCB。

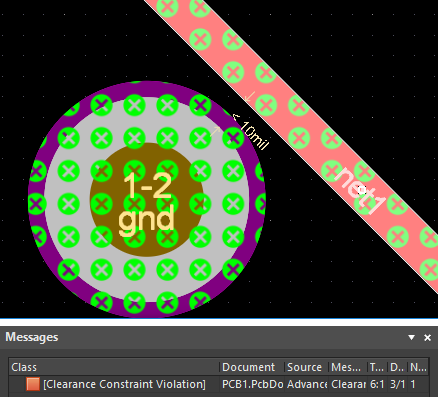

定义类别后,您就可以继续了解 DFM 规则。如果您想深入了解 IPC 文档,您可以在在线 IPC 商店 [1] 以合理的价格找到它。如果您只想了解要点,我个人最喜欢的 PCB 制造商之一 APCT 有一个电子表格,列出了 IPC 2 类和 3 类的最重要功能 [2]。但是,这些要求本身并没有太大用处。我们真正想要的是满足 ICP 类所需的尺寸,这就是我们了解 DFM 的核心内容。由于我已经提到了 APTC,我将再次引用它们。他们在此处发布了他们的 PCB DFM 要求 [3]。文档中的一些示例是最小铜线宽度和间距、钻孔到铜的距离以及通孔焊盘需要比钻孔尺寸大多少。这些是输入到您的 EDA 工具中的尺寸,当您遇到问题时,您会得到清晰的错误标记(图 1)。

图 1. 因违反许可而产生的错误标记(左)和更正后的图稿(右)。

因此,您将使用这些规则来布线电路板,一切都应该没问题,对吗?也许可以,但也可能不行。如果您尝试运行 10Gb/s 或更高的串行数据,如果您在设计电路板时没有考虑信号完整性,事情可能会出错。就像 IPC 分类一样,每个高速通信协议都有与之相关的电气通道标准。14 Gb/s 及以下的通道具有必须满足的 S 参数掩码才能确保通信。25Gb/s 及以上的通道具有需要满足的 S 参数掩码和通道操作裕度标准。关于如何定义 PCB,您可以将这些标准视为 IPC 分类的类比。标准不会为您提供达到目的的手段,而只会提供您需要实现的要求。就像 PCB 供应商有符合 IPC 标准的设计标准一样,我们希望设计标准能够满足信号完整性标准。那么,让我们开始吧!

信号完整性设计

连接器

通道中最明显的限制因素是连接器。幸运的是,当涉及到高速互连时,连接器公司已经为您完成了所有工作。您只需访问您最喜欢的连接器公司的网站,选择数据速率和应用程序,就会找到可行的解决方案。连接器公司甚至会为您提供从连接器到电路板的精确几何形状。困难的部分是连接器之间该怎么做。

通过存根

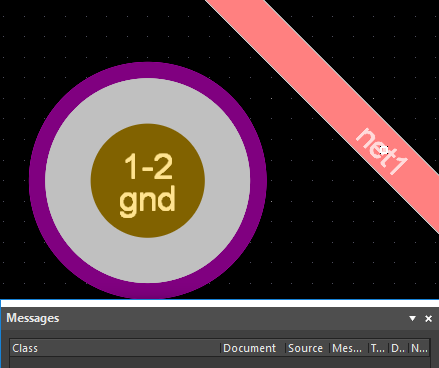

剩余的管筒从内部信号层延伸到 PCB 背面,形成一个过孔短截线(图 2)。短截线在其谐振频率下会产生大量能量损失,Q 值非常低。低 Q 值意味着它还会影响其谐振频率周围的一大段频率。

图 2. 使用 Altium 可视化的过孔短截线

过孔短截线造成的信号损失是连接器空间上出现的第一个问题。连接器公司有背钻建议,以避免过孔短截线造成的信号损失。背钻是一种工艺,在电镀后通过钻孔去除从信号层到连接器对面电路板一侧的剩余过孔。在 10 Gb/s 以下,使用过孔短截线是可以的。但是,在 10 Gb/s 之后,信号损失和短截线的额外反射将导致问题。因此,建议在 10 Gb/s 之后进行背钻。

走线损失

最终,如果信道损耗过多,链路将无法工作。IEEE 标准定义了各种数据速率的无源信道的损耗限制。10GBASE-KR 的长度仅限于 1 米(使用 Megtron 6 时损耗约为 13 dB),25GBASE-KR 在 12.9 GHz 时损耗限制为 35 dB,50GBASE-KR 在 13.28 GHz 时损耗限制为 30 dB [4, 5, 6]。信道损耗由趋肤效应衰减、表面粗糙度衰减和介电衰减引起。这些关系有些复杂,在《高速设计的高级信号完整性》[7] 中进行了很好的解释。假设 Megtron-6 PCB 材料、7 mil 走线和 8 um 表面粗糙度 (Rz),则可确定以下最大走线长度:10GBASE-KR 为 1m,25GBASE-KR 为 1.25m,50GBASE-KR 为 1.21m。这些数字不包括连接器和过渡介质的损耗。通道内的这些特征会缩短这些长度。

这只是一个估计值。为了获得更一致的结果,请在使用 [7] 中的指导创建电路板后从电路板中提取衰减系数。这将包括所有原位源,如果您需要重新旋转,将产生更好的结果。

差分走线

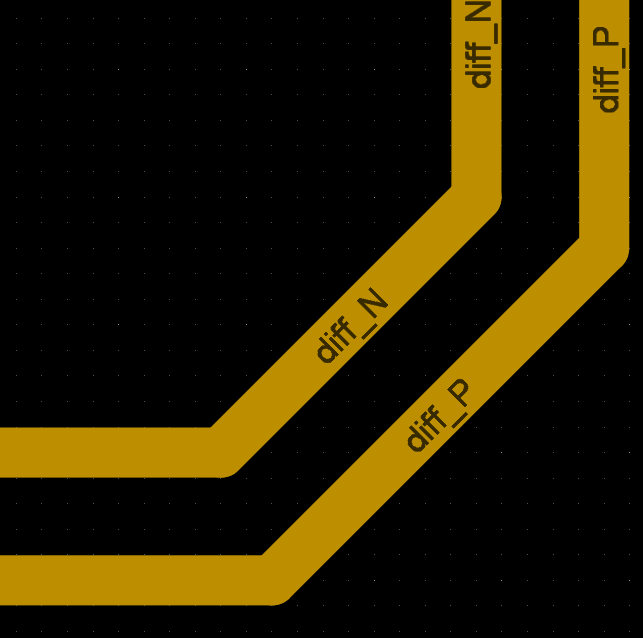

对于高达 5Gb/s 的信号,您可能可以使用单端迹线。单端迹线是行业术语,指承载串行数据流的单条迹线。超过 10Gb/s 时,您需要以差分方式布线。差分迹线是一对传输数据的导体,每条导体的数据相位相差 180 度(图 3)。这些迹线对噪声的免疫力更强,在应用中更容易实现干净的宽带性能。但是,差分对会受到偏移的影响。偏移是指对中的一半比另一半电气长度更长。偏移最好尽快纠正。但是,有些情况下偏移是不可避免的。在信号对有偏移的区域,辐射会更高。因此,在长度匹配之前,请保持迹线高度隔离。长度匹配后,请将迹线分开至少 5 倍迹线宽度。

图 3. Altium 中布线的差分对段。

我们可以量化偏移的影响,以确定线对中绝对最大长度差异。例如,假设 Megtron 6 材料中相位抵消造成的 1dB 额外损耗是偏移不可接受的。这导致:10 Gb/s 时为 23 mils,25 Gb/s 和 50 Gb/s (PAM4) 时为 9 mils。由于这是发生 1 dB 完整损耗之前的绝对最大值,因此将该数字除以二是合理的,以保证安全裕度。

走线的另一个重要方面是其阻抗。阻抗是瞬时电压与电流的比值。使用 Polar [9] 等工具可以轻松设计符合标称阻抗的走线。但是,PCB 制造商只能保证一定百分比内的阻抗。通常,这是 10%。许多电路板厂在批量生产时也提供 7% 和 5% 的容差。为了最大限度地减少 ISI 噪声,建议在 25 Gb/s 时使用 7% 的容差,在 50 Gb/s 时使用 5% 的容差。

如果您有时间和资源,实现目标阻抗的更好方法是构建一个复制您正在设计的电路板的测试电路板。布设多条宽度不同的走线,不要告诉 PCB 制造商保持阻抗。这样,您就可以使用最终应用中使用的堆叠和 PCB 制造商来查看哪种走线尺寸可以实现所需的阻抗。Wild River Technology 最近在 Design Con 2019 的小组讨论中展示了这项技术。

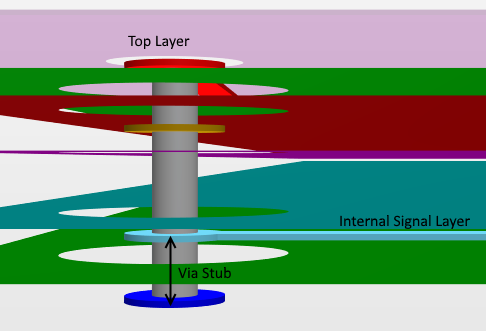

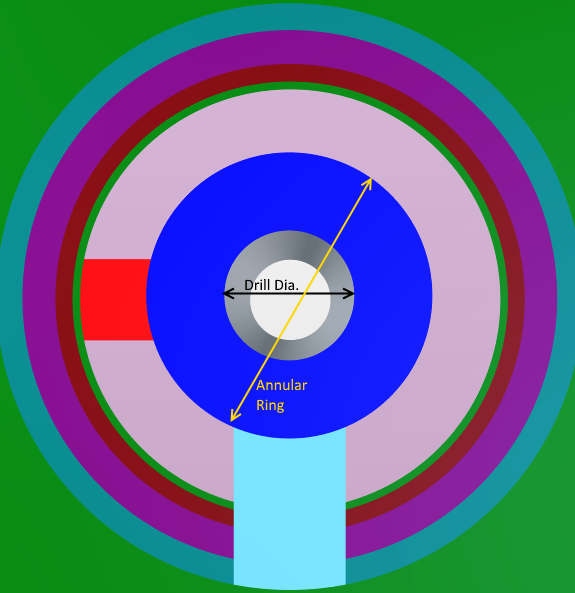

垫片

通孔焊盘可能是 PCB 设计中信号完整性最成问题的方面。虽然可以调整走线长度和短线以避免信号丢失,但通孔焊盘是不可避免的不连续性。大多数 PCB 制造商可以通过使用比钻孔尺寸大 12 mil 的通孔焊盘或环形环(图 4)(简称为正 12 mil)来满足 IPC 2 级要求。这种尺寸的焊盘会导致非常大的不连续性。对于 10Gb/s 及以下的数据速率,通常可以使用正 12 mil 的焊盘,因为较慢的上升时间可以滤除与此通孔相关的大部分噪声。对于 25 Gb/s 的数据速率,使用正 10 mil 而不是 12 mil 是明智的。对于 56Gb/s 及以上的数据速率,请使用尽可能小的焊盘,因为通孔不连续性会导致严重的眼图闭合。可能的最小通道通常为正 8 mil。对于许多制造商来说,在信号钻孔上方仅增加 8 毫米将难以满足 IPC 2 级标准。因此,请务必在下订单之前提前联系您的工厂并告知您的要求。

图 4. 使用 Altium 可视化的环形圈。

当环形环大于 8 mil 时,建议使用泪滴结构以避免切断走线和通孔之间的连接(图 5)。当走线与钻孔直径相同或更小且钻孔配准不准确时,可能会发生这种情况。此外,泪滴结构通常还有助于避免因通孔周围失去参考而产生的电感尖峰。

图 5. 具有 10 mil 钻孔的环形环、18 mil(加 8 mil)环形环和 10 mil 走线。

摘要表

可以为任何材料制作一个表格。在表 1 中,Megtron 6 具有 7 mil 宽的走线和 4 um

考虑了表面粗糙度。这是您 DFSI 的一个很好的起点。如果您有自己的 DFSI 标准,请随时在评论中留下它并帮助社区!

表 1. DFSI 规则

| 10GBASE-KR | 25GBASE-KR | 50GBASE-KR | |

| 数据速率 | 10.3125 Gb/秒 | 25.78125 Gb/秒 | 51.5625 Gb/秒 |

| 背钻 | 不要求 | 必需的 | 必需的 |

| 最大走线长度 (m) | 1 | 1.25 | 1.21 |

| 最大差分倾斜(mils) | 11.5 | 4.5 | 4.5 |

| 阻抗公差 | 10% | 7% | 5% |

| 通过环形环传输信号 | 钻孔 +12 mils | 钻孔 + 10 mils | 钻孔 + 8 密耳 |

参考:

[1] IPC-A-610 刚性印刷电路板鉴定和性能规范,2010 年 2 月、4 月。

[2] APCT IPC-6012D/DS 各产品类别要求差异,网址:https ://www.apctinc.com/wp-content/uploads/2018/04/APCT_Wallingford--IPC-6012D-Requirement-Oct2017.pdf

[3] APCT 企业制造能力,网址:https://www.apctinc.com/capabilities/

[4] IEEE 802.3ap 以太网在电气背板上的运行,2007 年 5 月

[5] IEEE 802.3bj 物理层规范和管理参数,用于背板和铜缆上 100 Gb/s 的运行,2014 年 6 月

[6] IEEE 802.3cd 50 Gb/s 和物理层的媒体访问控制参数以及

50 Gb/s、100 Gb/s 和 200 Gb/s 运行的管理参数,2018 年 12 月

[7] Janezic, MD, JA Jargon,“通过传播常数测量确定复介电常数”,IEEE 微波和指导快报,第 9 卷,第 2 期,(1999 年),第 76-78 页

[8] S. Hall、H. Heck,《高速数字设计的高级信号完整性》,Wiley 2011

[9] Polar Instruments,网址:PCB signal integrity, stackup and controlled impedance

3397

3397

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?