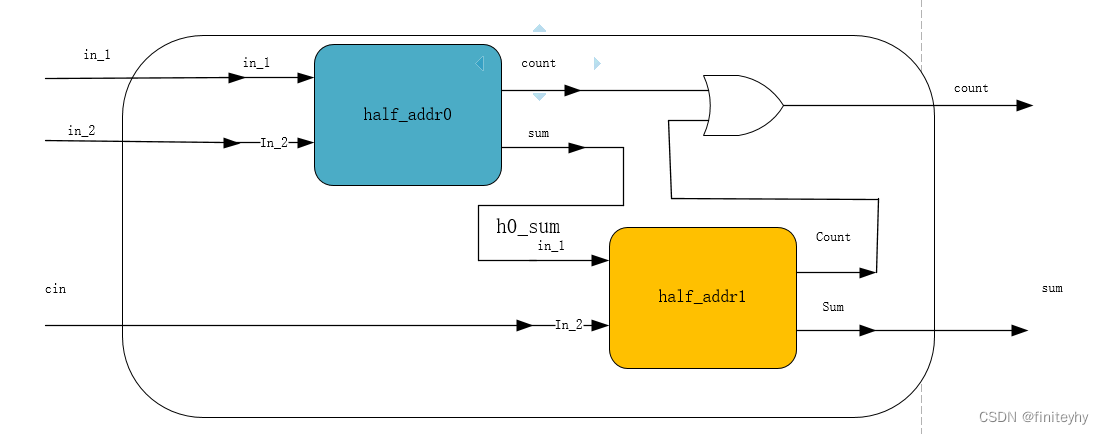

模块化 调用半加器模块 在全加器模块中对两个半加器分别进行实例化

用两个半加器实现全加器 ,用或门连接两个进位信号

module full_addr

module full_addr

(

input wire in1,

input wire in2,

input wire cin,

output wire sum,

output wire count

);

wire h0_sum;

wire h0_count;

wire h1_count;

half_addr half_addr_inst0

(

.in1(in1),

.in2(in2),

.sum(h0_sum),

.count(h0_count)

);

half_addr half_addr_inst1

(

.in1(h0_sum),

.in2(cin),

.sum(sum),

.count(h1_count)

);

assign count=(h0_count | h1_count)

endmodulemodule tb_full_addr

module tb_full_addr();

reg in1;

reg in2;

reg cin;

wire sum;

wire count;

initial

begin

in1 <= 1'b0;

in2 <= 1'b0;

cin <= 1'b0;

end

initial

begin

$timeformat(-9,0,"ns",6);

$monitor("time %t:in1 = %b,in2 = %b, cin = %b, sum = %b,count = %b",$time,in1,in2,cin,sum,count)

always #10 in1 <= {$random}%2;

always #10 in2 <= {$random}%2;

always #10 cin <= {$random}%2;

full_addr full_addr_inst

(

.in1(in1),

.in2(in2),

.cin(cin),

.sum(sum),

.count(count)

);

endmodule

打印信息

199

199

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?