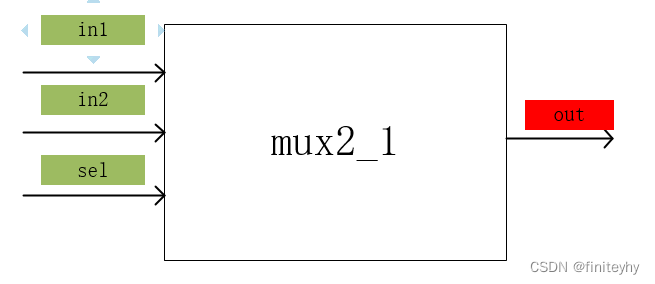

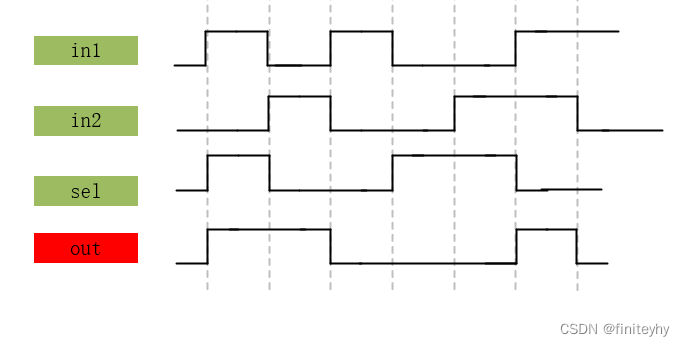

当位选信号sel为高电平,输出in1,低电平输出in2

module mux2_1

module mux2_1

(

input wire in1,

input wire in2,

input wire sel,

output wire out

);

case(sel):

1'b1: out <= in1;

1'b0: out <= in2;

default: out<=in1;

endcase

endmodulemodule tb_mux2_1

module mux2_1();

wire in1;

wire in2;

wire sel;

wire out;

initial

begin

in1 <=1'b0;

in2 <=1'b0;

sel <=1'b0;

end

always #10 in1 <= {$random}%2;

always #10 in2 <= {$random}%2;

always #10 sel <= {$random}%2;

mux2_1 mux2_1_inst

(

.in1(in1),

.in2(in2),

.sel(sel),

.out(out)

)

endmodule

541

541

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?