// 本文对应Design Compiler 2017.09 Lab1的学习

一、DC命令

alias:显示所有的简写,alias h:显示简写'h'的原型

check_library:检查逻辑库和物理库

link:链接设计中的实例化引用

a、如果例化的是与非门,从target_library中寻找;

b、如果例化的是ip,从ip的库中寻找;

c、如果例化的是模块,从内存中寻找,因为代码在read时已经读入内存中去了。基于每个独立的模块来看,如果存在语法错误,此时read就会有错误提示。

write -hierarchy -format ddc -output unmapped/TOP.ddc:保存unmapped文件,compile后的mapped文件也是相同的保存方式

write_icc2_files -output ./mapped/TOP_icc2:将设计保存为ICC2需要的文件格式,ICC2是synopsys自己的PR工具

list_designs/list_libs:列出设计和库清单

report_constraint -all_violators:报告所有违例的路径。max_leakage违例是因为默认的max_leakage约束为0

report_timing:报告每个时钟下的critical path

report_area:报告设计的面积

remove_design -designs:将设计从内存中移除

二、DV操作

- Schematic View中鼠标左键双击和

区别:双击相当于把某个模块内部细节呈现,但是其它模块仍然保留在当前视图。

区别:双击相当于把某个模块内部细节呈现,但是其它模块仍然保留在当前视图。 时只关注当前模块,其它模块被忽略。

时只关注当前模块,其它模块被忽略。

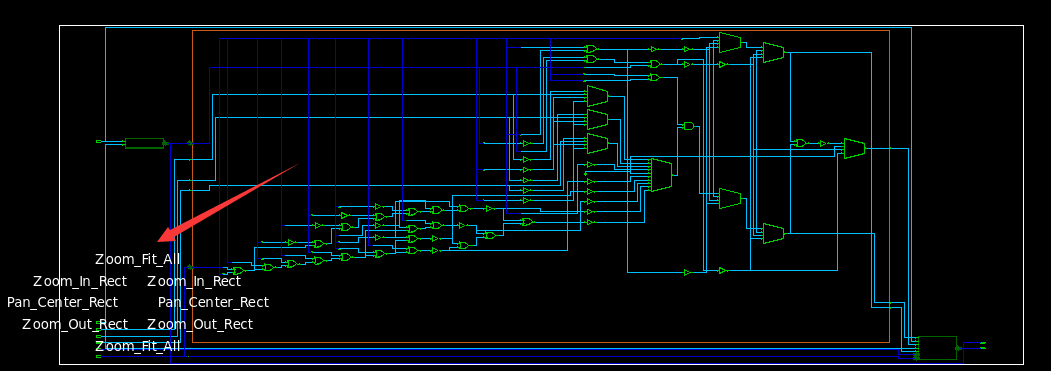

双击效果举例:

- 点击鼠标中键后悬停,可以浮现操作轮盘

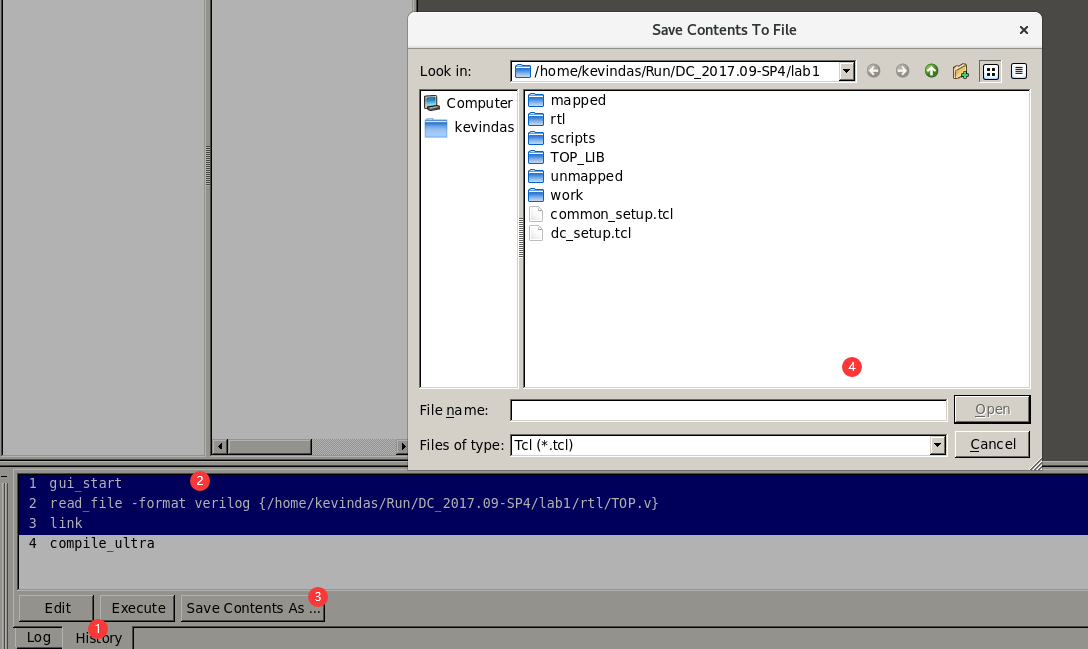

- 将DC的部分操作保存为脚本

三、其它

- DC命令被执行后返回1表示命令被成功执行。

- compile_ultra命令会自动将设计打平(flatten),以获得更好的时序和面积结果。

- DC意外退出后的恢复:command.log文件记录了DC的操作,copy并重新命名为xx.tcl,将xx.tcl最末尾的exit或quit删除,重新使用DC加载该脚本:

design_vision -topo -f xx.tcl

491

491

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?