出于学习目的,将DS90LV012A英文数据手册翻译为中文数据手册,分享给需要的小伙伴。

水平有限,烦请谅解。如翻译有误,请留言,笔者将尽快更正,谢谢~

本文仅展现原理部分,详细电性能参数、封装等信息参照中文数据手册,下载链接如下:

lmk04821中文数据手册资源-CSDN文库 https://download.csdn.net/download/lu2289504634/89530525

https://download.csdn.net/download/lu2289504634/89530525

1 特征

- 支持 JEDEC JESD204B

- 超低RMS抖动

- 88 fs RMS抖动(12 kHz 至 20 MHz)

- 91 fs RMS抖动(100 Hz 至 20 MHz)

- -162.5 dBc/Hz 本底噪声@245.76 MHz

- 来自 PLL2 的多达 14 个差分设备时钟

- 最多 7 个 SYSREF 时钟

- 最大时钟输出频率 3.1 GHz

- 来自 PLL2 的 LVPECL、LVDS、HSDS、LCPECL 可编程输出

- 来自 PLL1 最多 1 个缓冲 VCXO/晶体输出

- LVPECL、LVDS、2xLVCMOS 可编程

- 双环 PLLatinum™ PLL 架构

- PLL1

- 多达 3 个冗余输入时钟

- 自动和手动切换模式

- 无中断切换和 LOS

- 集成低噪声晶体振荡器电路

- 输入时钟丢失时的保持模式

- PLL2

- 归一化 [1 Hz] PLL 本底噪声为-227 dBc/Hz

- 鉴相频率高达 155 MHz

- OSCin 倍频器

- 两个集成的低噪声 VCO

- 50% 占空比输出分频,1 至 32(偶数和奇数)

- 精密数字延迟,动态可调

- 25 ps 步进模拟延迟

- 多模式:双 PLL、单 PLL 和时钟分配

- 工业温度范围:-40 至 85°C

- 支持 105°C PCB 温度(在散热焊盘处测量)

- 3.15 V 至 3.45 V 工作电压

- 封装:64 引脚 QFN(9.0 mm × 9.0 mm × 0.8mm)

2 应用

- 无线基础设施

- 数据转换器时钟

- 网络、SONET/SDH、DSLAM

- 医疗/视频/军事/航空航天

- 测试和测量

3 描述

LMK0482x 系列是业界支持 JEDEC/JESD204B的最高性能的时钟调节器。

PLL2 的 14 个时钟输出可配置为设备时钟和 SYSREF 时钟,以驱动7个JESD204B转换器或其他逻辑器件。可通过直流和交流耦合提供SYSREF时钟。不仅限于JESD204B应用,14 个输出中的每一个都可单独配置为用于传统时钟系统的高性能输出。

LMK0482x 系列的高性能,再加上在功耗或性能之间进行权衡的能力、双 VCO、动态数字延迟、保持模式和无损模拟延迟等特性,使其成为提供灵活的高性能时钟树的理想之选。

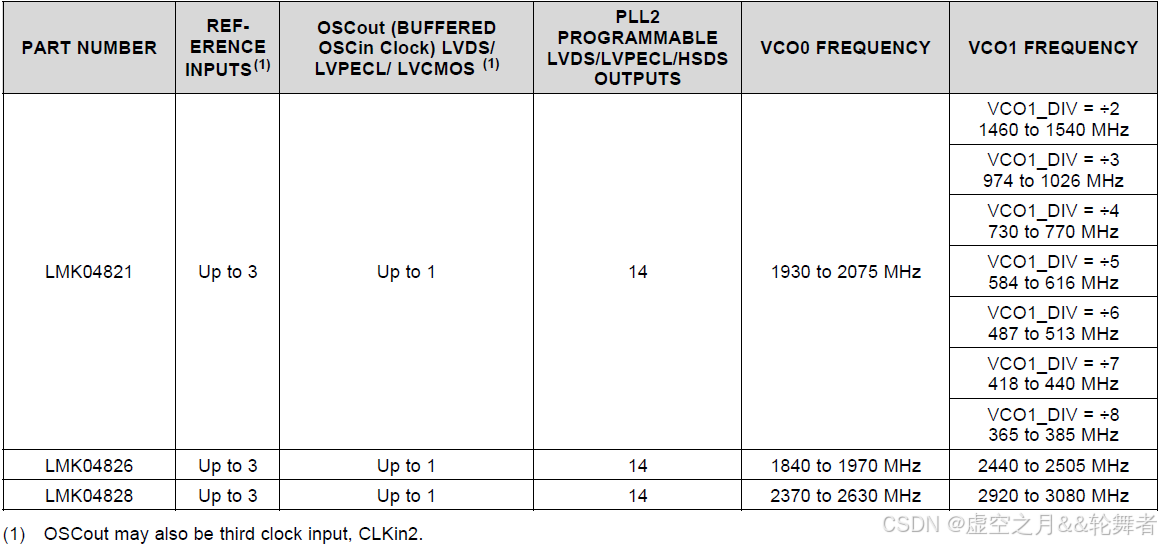

4芯片对比表

4.1 芯片配置信息

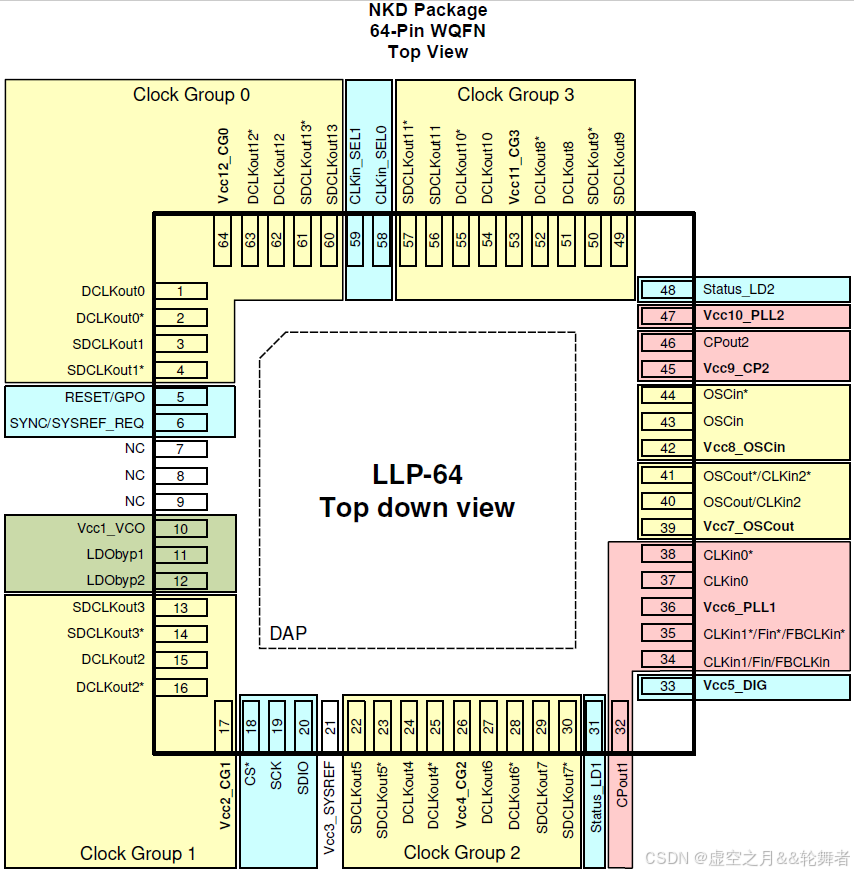

5 芯片引脚及功能

| 引脚 |

I/O |

描述 |

|

| 编号 |

名称 |

||

| 1 |

DCLKout0 |

O |

设备时钟输出0。差分时钟输出,隶属于时钟组0。为尽量减少噪声,应使时钟组中的所有输出保持相同频率或无杂散干扰的频率。如果未使用,则将输出格式缓冲器设置为断电,并让引脚处于浮空状态。 |

| 2 |

DCLKout0* |

||

| 3 |

SDCLKout1 |

O |

SYSREF/设备时钟输出1。差分时钟输出,隶属于时钟组0。为尽量减少噪声,应使时钟组中的所有输出保持相同频率或无杂散干扰的频率。如果未使用,则将输出格式缓冲器设置为断电,并让引脚处于浮空状态。 |

| 4 |

SDCLKout1* |

||

| 5 |

RESET/GPO |

I/O |

设备复位输入或 GPO。如果用作复位输入,引脚极性和标称160kΩ上拉或下拉由寄存器设置控制。如果用作输出,则可设置为推挽式或开漏式。 |

| 6 |

SYNC/SYSREF_REQ |

I |

同步输入。可用于复位分频器、触发SYSREF脉冲发生器,或从 SYSREF 分频器请求SYSREF连续模式。引脚极性由寄存器设置控制。标称160 kΩ下拉。 |

| 7 |

—— |

NC |

引脚必须保持浮空 |

| 8 |

—— |

NC |

|

| 9 |

—— |

NC |

|

| 10 |

Vcc1_VCO |

P |

VCO LDO电源,去耦电容要求随系统频率变化,详见10.1章节“引脚连接建议” |

| 11 |

LDObyp1 |

BP |

LDO旁路。必须在该引脚附近放置10μF的电容器,将其旁路到地。 |

| 12 |

LDObyp2 |

BP |

LDO旁路。必须在该引脚附近放置0.1μF的电容器,将其旁路到地。 |

| 13 |

SDCLKout3 |

O |

SYSREF/设备时钟输出3。差分时钟输出,隶属于时钟组1。为尽量减少噪声,应使时钟组中的所有输出保持相同频率或无杂散干扰的频率。如果未使用,则将输出格式缓冲器设置为断电,并让引脚处于浮空状态。 |

| 14 |

SDCLKout3* |

||

| 15 |

DCLKout2 |

O |

设备时钟输出2。差分时钟输出,隶属于时钟组1。为尽量减少噪声,应使时钟组中的所有输出保持相同频率或无杂散干扰的频率。如果未使用,则将输出格式缓冲器设置为断电,并让引脚处于浮空状态。 |

| 16 |

DCLKout2* |

||

| 17 |

Vcc2_CG1 |

P |

时钟输出2和3的电源。去耦电容要求可能随系统频率而变化。有关建议,请参阅引脚连接建议。 |

| 18 |

CS* |

I |

SPI 芯片选择。低电平有效输入。不使用时必须从外部拉高或主动驱动为高电平。 |

| 19 |

SCK |

I |

SPI时钟。高电平有效输入。标称160 kΩ 下拉。 |

| 20 |

SDIO |

I/O |

SPI 数据。该引脚可实现双向I/O。作为输出,该引脚可配置为漏极开路或推挽式。开漏输出需要外部上拉。寄存器设置可禁用该引脚的输出功能。其他 GPIO 引脚也可配置为传统 4 线SPI的SPI MISO(主-入-从-出)。 |

| 21 |

Vcc3_SYSREF |

P |

SYSREF 分频器和 SYNC 的电源。去耦电容要求可能随系统频率而变化。有关建议,请参阅引脚连接建议。 |

| 22 |

SDCLKout5 |

O |

SYSREF/设备时钟输出5。差分时钟输出,隶属于时钟组2。为尽量减少噪声,应使时钟组中的所有输出保持相同频率或无杂散干扰的频率。如果未使用,则将输出格式缓冲器设置为断电,并让引脚处于浮空状态。 |

| 23 |

SDCLKout5* |

||

| 24 |

DCLKout4 |

O |

设备时钟输出4。差分时钟输出,隶属于时钟组2。为尽量减少噪声,应使时钟组中的所有输出保持相同频率或无杂散干扰的频率。如果未使用,则将输出格式缓冲器设置为断电,并让引脚处于浮空状态。 |

| 25 |

DCLKout4* |

||

| 26 |

Vcc4_CG2 |

时钟输出 4、5、6 和 7 的电源。去耦电容要求可能随系统频率而变化。有关建议,请参阅引脚连接建议。 |

|

| 27 |

DCLKout6 |

O |

设备时钟输出6。差分时钟输出,隶属于时钟组2。为尽量减少噪声,应使时钟组中的所有输出保持相同频率或无杂散干扰的频率。如果未使用,则将输出格式缓冲器设置为断电,并让引脚处于浮空状态。 |

| 28 |

DCLKout6* |

||

| 29 |

SDCLKout7 |

O |

SYSREF/设备时钟输出7。差分时钟输出,隶属于时钟组2。为尽量减少噪声,应使时钟组中的所有输出保持相同频率或无杂散干扰的频率。如果未使用,则将输出格式缓冲器设置为断电,并让引脚处于浮空状态。 |

| 30 |

SDCLKout7* |

||

| 31 |

Status_LD1 |

I/O |

可编程状态引脚。默认情况下,该引脚被配置为高电平有效输出,表征PLL1锁定检测的状态。其他状态条件和输出极性可通过寄存器选择。该引脚可配置为开漏或推挽输出。 |

| 32 |

CPout1 |

O |

电荷泵 1 输出。该引脚连接至 PLL1 的外部环路滤波器元件以及 VCXO 控制电压引脚。 |

| 33 |

Vcc5_DIG |

P |

为 SPI 总线和 GPIO 引脚等数字电路供电。去耦电容要求可能随系统频率而变化。有关建议,请参阅引脚连接建议。 |

| 34 |

CLKin1 |

I |

(默认)PLL1的参考时钟输入端口1。可配置为直流或交流耦合。可接受单端或差分时钟。如果在单端配置中未使用,则使用 0.1-μF 电容连接至 GND。如果两个引脚都未使用,则保持浮空。有关单端信息,请参阅 "驱动 CLKin 和 OSCin 输入"。 |

| FBCLKin |

用于外部时钟的反馈输入(零延迟模式)。可配置为直流或交流耦合。可接受单端或差分时钟。如果在单端配置中未使用,则用 0.1-μF 电容连接至 GND。如果两个引脚都未使用,则保持浮空。有关单端信息,请参阅 "驱动 CLKin和OSCin输入"。 |

||

| Fin |

外部 VCO 输入(外部 VCO 模式)或时钟分配输入(分配模式)。可配置为直流或交流耦合。可接受单端或差分时钟。如果在单端配置中未使用,则使用 0.1-μF 电容连接至 GND。如果两个引脚都未使用,则保持浮空。有关单端信息,请参阅 "驱动 CLKin 和 OSCin 输入"。 |

||

| 35 |

CLKin1* |

I |

(默认)PLL1 的参考时钟输入端口1。可配置为直流或交流耦合。可接受单端或差分时钟。如果在单端配置中未使用,则使用0.1-μF电容连接至GND。如果两个引脚都未使用,则保持浮空。有关单端信息,请参阅 "驱动CLKin和OSCin输入"。 |

| FBCLKin* |

|||

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

4904

4904

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?