Nmos管做低端驱动

电路工作原理说明:

对于Nmos管,G极电位比S极电位高于导通域值电压便会导通

对于Pmos管则相反,G极电位比S极电位低于导通域值电压才会导通

所以Nmos管适合做低端驱动,S极接地,以使S极的电压固定,Pmos管适合做高端驱动,S极接电源VCC,也是使S极的电压固定

当MCU IO输出高电平时,Q1三极管B极电位高于E极电位,发射极正偏,Q1三极管导通,从而将Q2三极管的B极电位拉低,Q2三极管发射极也正偏,三极管导通,12*10/11≈10.9V,再减去三极管的导通压降0.7V,MOS管G极的电位便是10.2V,MOS管导通

由于并非图腾柱驱动电路,信号低电平时,缺少强拉断,导致MOS管关断较慢,对于频率较高的驱动信号,需要注意

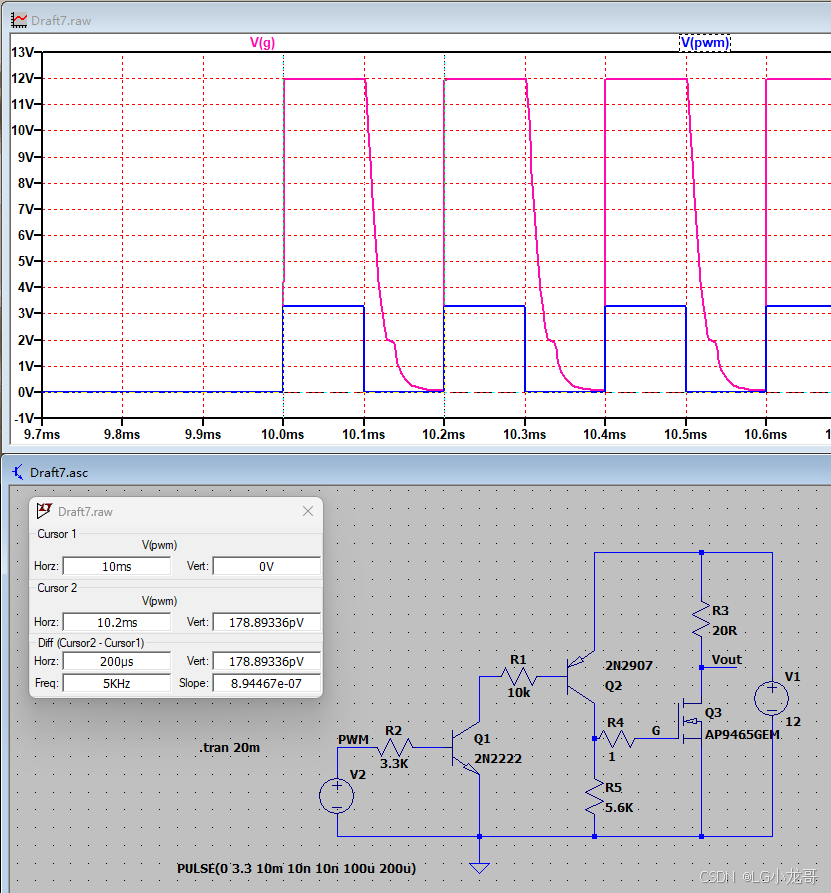

下图为应用仿真波形,对于输入信号为5Khz,50%真空比的方波信号,MOS管开通时,由Q2三极管导通后,12V电源通过R4施加至MOS管栅极,MOS管快速开通(对于更高的频率,或者快速开通的应用,MOS的栅极驱动电阻R4的阻值需要减小);当Q2关断时,由于MOS管栅极寄生电容存有电荷,需通过R4以及R5泻放后,MOS才逐渐关闭,关断较慢

蓝色为3.3V PWM输入信号, 红色为MOS栅极驱动信号

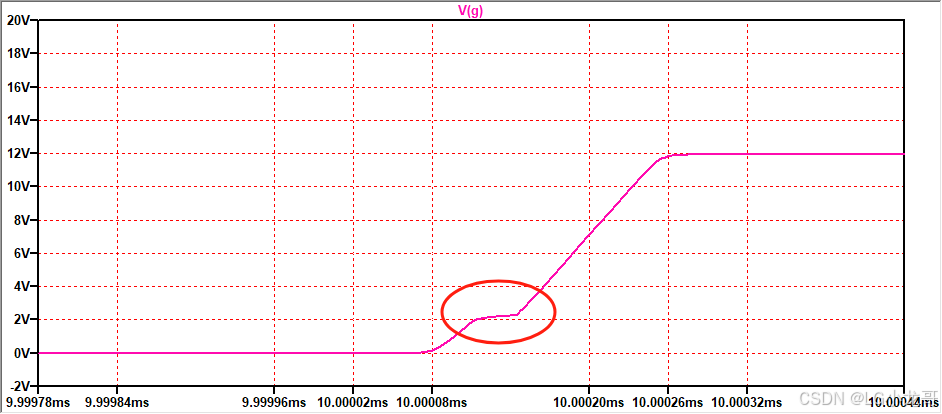

MOS开通 米勒平台

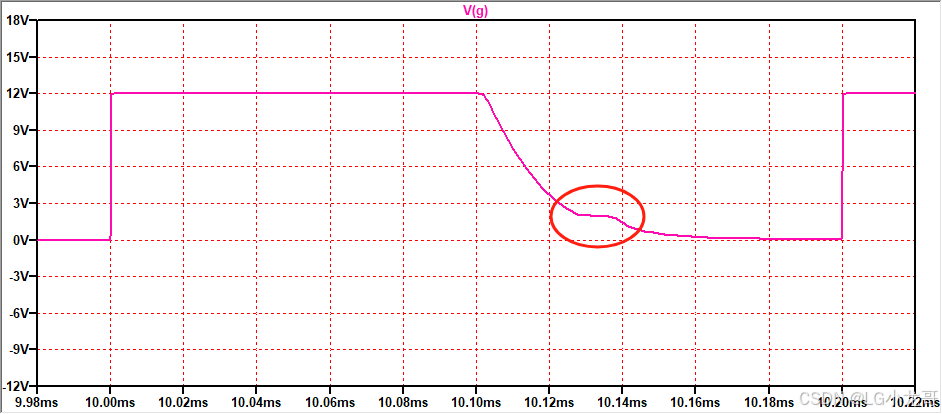

MOS关断 弥勒平台

本文详细介绍了Nmos管作为低端驱动的工作原理。当Nmos管的栅极电位高于源极,管子导通;反之,Pmos管在栅极电位低于源极时导通。由于这种特性,Nmos适合用于电路的地端驱动,保持源极电压固定,而Pmos适合高端驱动。通过MCU的IO口控制,可以实现对MOS管导通状态的精准控制。

本文详细介绍了Nmos管作为低端驱动的工作原理。当Nmos管的栅极电位高于源极,管子导通;反之,Pmos管在栅极电位低于源极时导通。由于这种特性,Nmos适合用于电路的地端驱动,保持源极电压固定,而Pmos适合高端驱动。通过MCU的IO口控制,可以实现对MOS管导通状态的精准控制。

1162

1162

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?