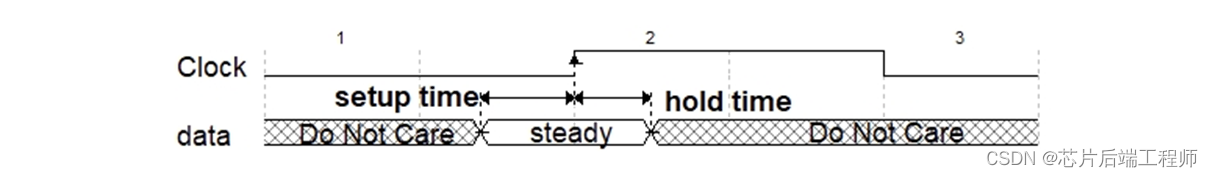

写在前面:先讲一下setup time和hold time的概念

建立时间:在时钟沿到来之前信号保持稳定的最小时间。

保持时间:指在时钟沿来临之后信号保持稳定的最小时间。

简而言之,触发器采样的前后一段时间内数据必须保持稳定,否则采样出的数据将会出现未知态,也就是我们常常说的“亚稳态”

在lib中,一般对于同步(synchronous)输入引脚,例如引脚D(或SI,SE)以及一些black box的同步输入端口,存在建立时间和保持时间的检查。

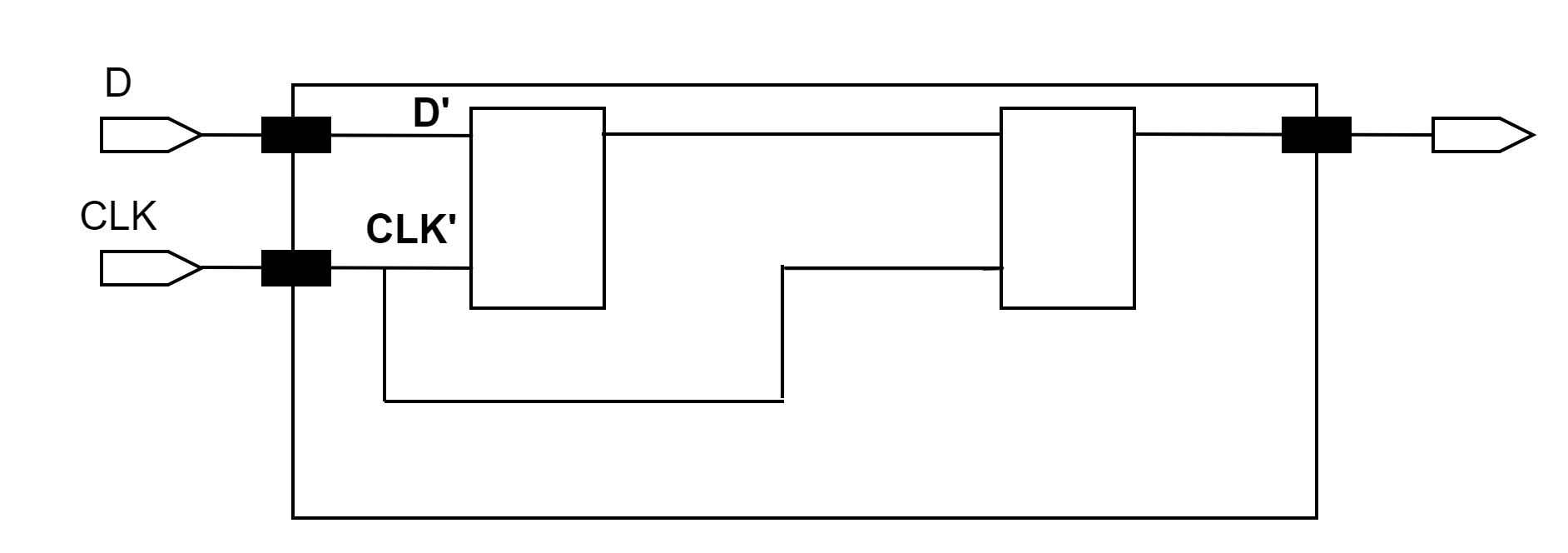

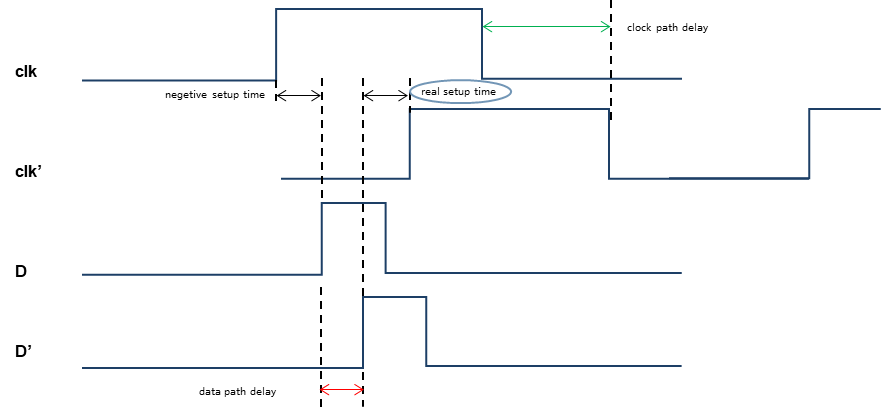

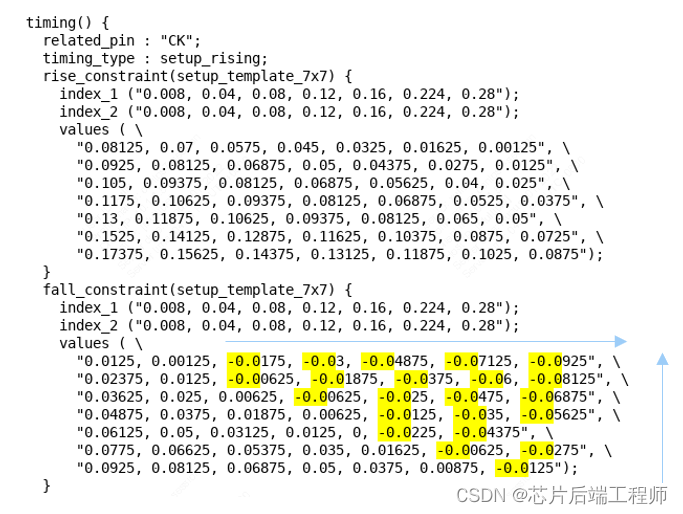

Lib 中 setup为负详细分析:

对于普通寄存器,从接口处的管脚到内部数据采集的latch的数据和时钟端之间还存在一段delay。当data从pin到锁存数据的锁存器的delay时间小于clock从pin到达锁存器CK端的delay时,那么D就可以在CLK上升沿之后再稳定,此时从register层面观测到的setup为负值,而实际上在锁存数据的锁存器端,由于之前data延迟小于clock延迟,D’仍在CLK’之前到来之前稳定,也就是此时实际setup仍为正值,只不过在register层面看为负值。

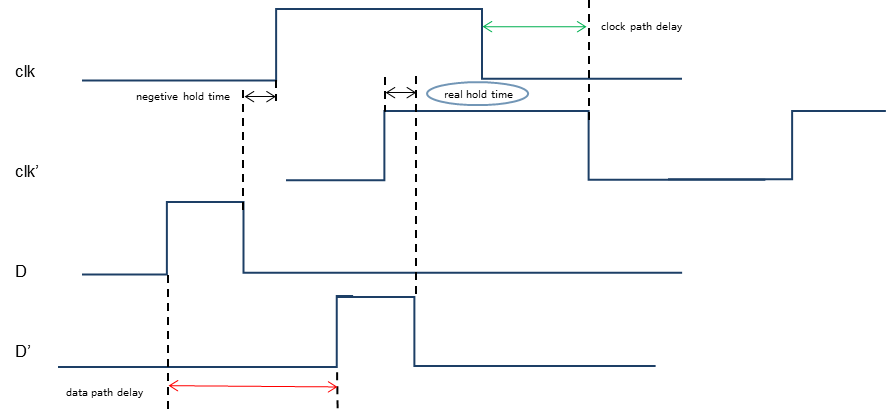

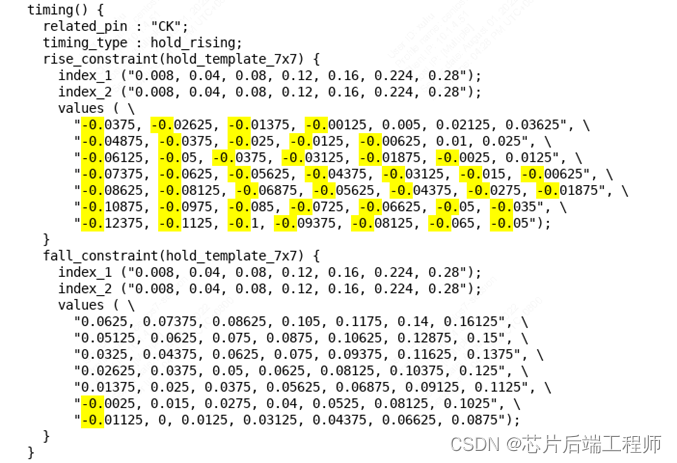

Lib 中 hold 为负详细分析:

同样因为寄存器端口到内部器件有一段delay,如果data 那段delay明显要大,hold就可能是负值了

对于建立时间来说,constrained pin transition越小,related pin transition越大,越趋向于负值。因为当clock上的transition相对较大时, clock 那段delay相对应的会较大,setup就更趋向负值了。对于保持时间来说正好相反。

结语

在较复杂的时序单元内,clock path与data path的长度不同,延时不同,可能导致setup time或者hold time为负。但是也必须保证“最小采样窗” (Tsetup + Thold)大于零成立,即保证数据有一段稳定的时间可以采样。

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?