4 DDR5 SDRAM命令描述和操作-8

4.8 写操作

写入操作将数据存储到DRAM中。它由写入命令启动,在此期间提供要写入阵列的数据的起列地址和bank/组地

址。数据在写入命令后的CAS写入延迟(CWL)周期内通过DQ输入提供给DRAM,同时在DQS输入上提供正确的

波形。CAS写入延迟是从写入命令的最后一个周期到第一个有效上升DQS(不包括写入前导码)的定义和测

量。

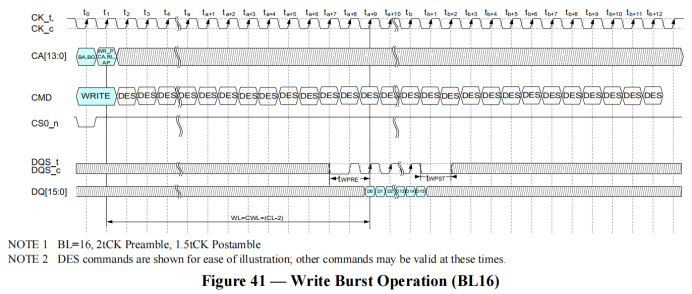

4.8.1 写数据掩码

在x8和x16的DDR5 SDRAM中,为每个字节数据组支持一个写入数据屏蔽(DM_n)引脚。通过模式寄存器启用

DM_n引脚/功能。对于x4配置的SDRAM,必须禁用DM模式寄存器设置。DM_n引脚在写入操作中具有与DQ引脚相

同的时序和终端功能,如图41所示。DM_n引脚在读取周期中不使用,该引脚应像DQ引脚一样驱动高电平或终

端到RTT_PARK。当MR禁用DM功能时,DRAM禁用DM输入和输出接收器,并且不期望也不驱动任何有效逻辑电平。

每个数据屏蔽突发位位置对应于相应字节组中DQ数据突发的相同位位置。

写入命令中的WR_partial = Low必须与DM_n数据一起使用。WR_partial = Low用于帮助DRAM在屏蔽写入期间

启动内部读取以进行“读取修改写入”。如果在写入期间WR_partial = High,则DM_n上的掩码数据必须为高

电平。如果禁用了DM(MR5 OP[5] = 0),则WR_Partial必须为“H”。DM_n可以是高电平或低电平。

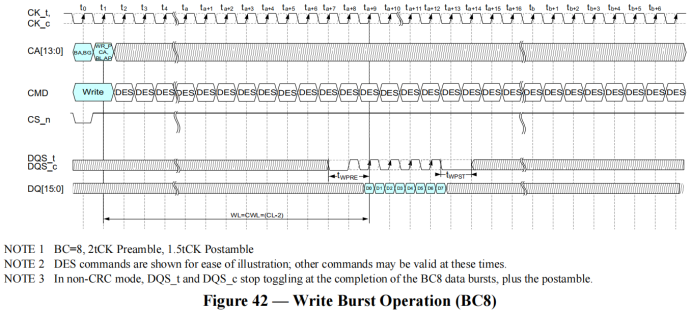

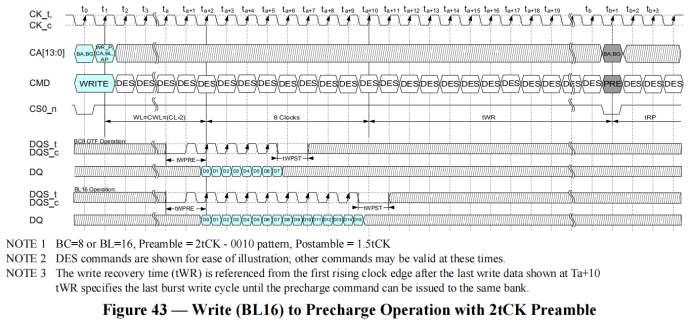

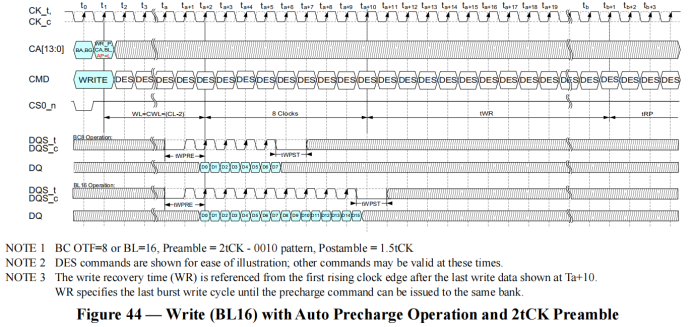

4.8.2 写突发操作

下面的写入时序图旨在帮助理解每个写入参数的含义;这些图表只是示例。每个参数的细节是单独定义的。

在这些写入时序图中,为了清晰起见,CK和DQS被显示为对齐。同时,DQS和DQ被显示为中心对齐。CK和DQS

之间以及DQS和DQ之间可能存在适当的偏移量。

注意事项1:BC=8,前导时间为2tCK,后导时间为1.5tCK。

注意事项2:DEs命令只是为了方便说明而显示;其他命令在这些时间点也可能有效。

注意事项3:在非CRC模式下,DQS_t和DQS_c在完成BC8数据突发以及后导时间后停止切换。

注意事项1:BC=8或BL=16,前导时间为2tCK,使用0010模式,后导时间为1.5tCK。

注意事项2:DEs命令只是为了方便说明而显示;其他命令在这些时间点也可能有效。

注意事项3:写入恢复时间(tWR)是从最后一个写入数据后的第一个上升时钟沿开始计时,Ta+10时刻后的时

钟沿。

tWR指定了最后一个突发写入周期,直到可以向同一银行发出预充电命令。

注意事项1:BC OTF=8或BL=16,前导时间为2tCK,使用0010模式,后导时间为1.5tCK。

注意事项2:DEs命令只是为了方便说明而显示;其他命令在这些时间点也可能有效。

注意事项3:写入恢复时间(WR)是从最后一个写入数据后的第一个上升时钟沿开始计时,Ta+10时刻后的时

钟沿。

WR指定了最后一个突发写入周期,直到可以向同一银行发出预充电命令。

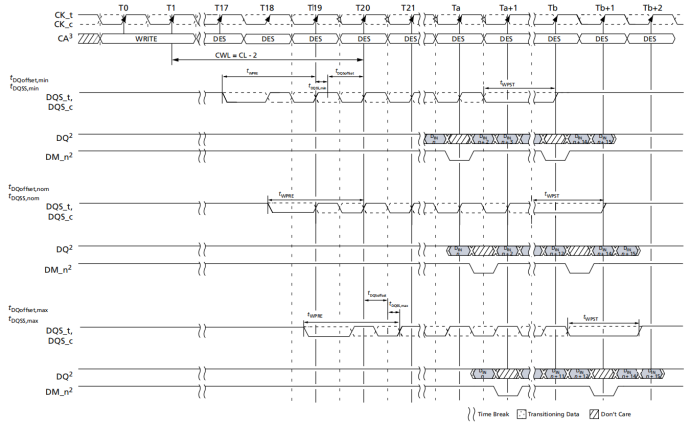

4.8.3 写时序参数

图45仅作为示例,用于列举特定写入突发的时钟边沿。对于有效的突发,必须满足每个边沿的所有时序参数。

注意事项1:BL=16,前导时间为2CK,使用0010模式,后导时间为1.5CK。

注意事项2:DEs命令只是为了方便说明而显示;其他命令在这些时间点也可能有效。

注意事项3:tDQSS必须在每个上升时钟沿上满足。

注意事项4:图中假设DRAM内部WL训练已完成。

注意事项5:DQ/DM_n脉冲时序和DQS到DQ的偏移由相应速度档位的Rx Strobe抖动敏感性规格定义。

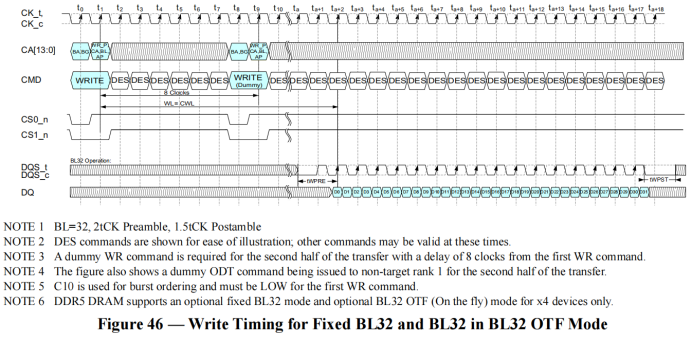

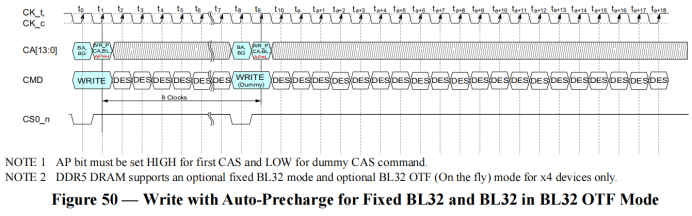

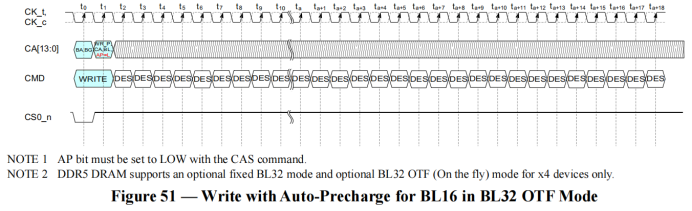

4.8.4 可选BL32模式的写突发操作

以下写入时序图涵盖了固定BL32、BL32 OTF模式下的BL32和仅适用于x4设备的BL16在BL32 OTF模式下的写入

时序。

在这些写入时序图中,为了清晰起见,CK和DQS被显示为对齐。同时,DQS和DQ被显示为中心对齐。CK和DQS

之间的偏移以及DQS和DQ之间的偏移可能是适当的。

第二个传输的后半段需要一个虚拟CAS命令来完成。如果系统需要非目标ODT,则必须向非目标rank发出虚拟

ODT命令来完成BL32的后半段传输。

注意事项1:BL=32,前导时间为2tCK,后导时间为1.5tCK。

注意事项2:DEs命令只是为了方便说明而显示;其他命令在这些时间点也可能有效。

注意事项3:在传输的后半段,需要延迟8个时钟周期发出一个虚拟WR命令。

注意事项4:图中还显示了向非目标rank 1发出一个虚拟ODT命令来完成传输的后半段。

注意事项5:C10用于突发指令排序,在第一个WR命令时必须为低电平。

注意事项6:DDR5 DRAM仅支持可选的固定BL32模式和可选的BL32 OTF(即时)模式,仅适用于x4设备。

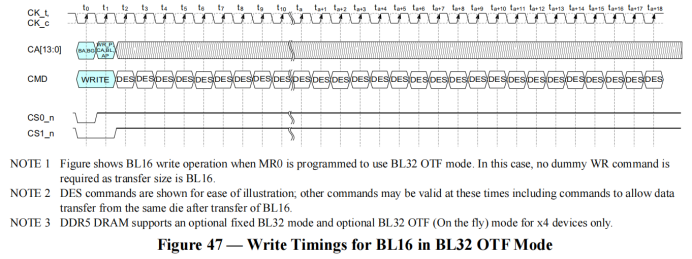

注意事项1:图中显示了当将MR0编程为使用BL32 OTF模式时的BL16写入操作。在这种情况下,由于传输大小

为BL16,不需要虚拟WR命令。

注意事项2:DEs命令只是为了方便说明而显示;其他命令在这些时间点也可能有效,包括允许在BL16传输之

后从同一芯片内进行数据传输的命令。

注意事项3:DDR5 DRAM仅支持可选的固定BL32模式和可选的BL32 OTF(即时)模式,仅适用于x4设备。

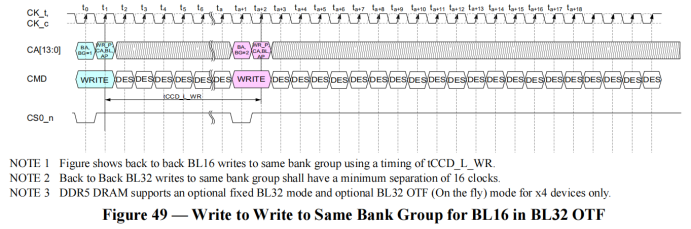

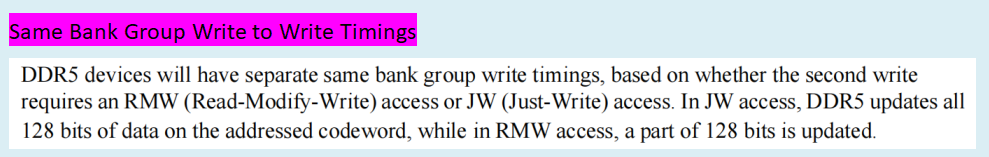

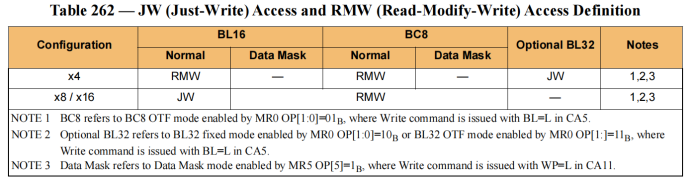

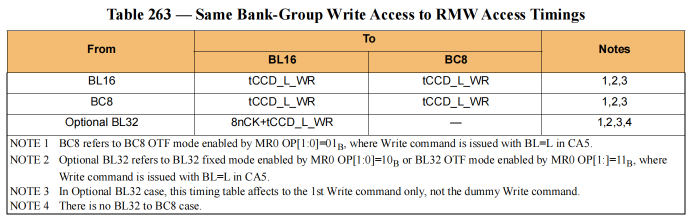

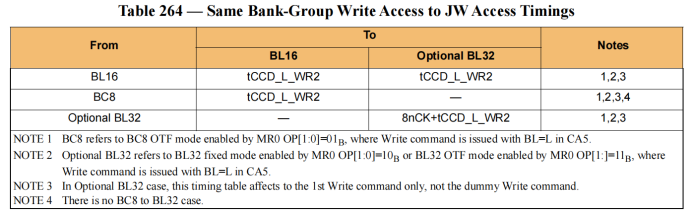

4.8.5 同一BG的写后写时序

DDR5设备将根据第二次写入是否需要RMW(读取-修改-写入)访问或JW(仅写入)访问,具有单独的相同存储

体组写入时序。在JW访问中,DDR5会更新所寻址编码字的全部128位数据,而在RMW访问中,只会更新128位

数据的一部分。

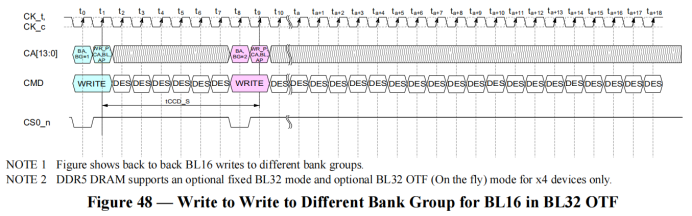

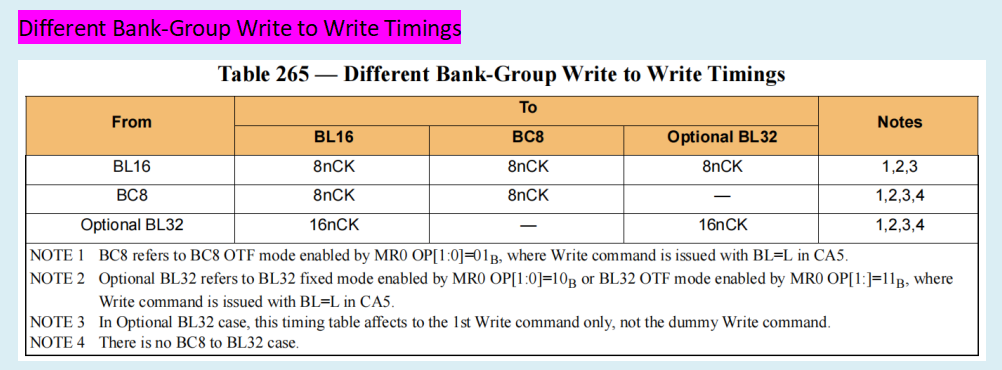

4.8.6 不同BG的写后写时序

4.8.7 写时序违反

4.8.7.1 诱因

通常情况下,如果写入时序参数被违反,就需要进行完整的复位/初始化过程,以确保DRAM正常工作。然而,

在本节中指定的某些违规情况下,希望DRAM能够保证不会“卡住”,并且错误仅限于特定的操作。

针对以下情况,假设关于写入命令本身(包括ODT等)没有时序违规,并且满足未在以下部分提到的所有时序

要求。

4.8.7.2 数据到脉冲眼图高和宽违反

如果违反所需的数据到时序或电压参数(例如:tRx_RDQ_tMargin,tRx_DQS2DQ_Skew,VRx_DQS,VRx_DQ

等),针对写入突发数据眼的任何数据/时序边缘或数据/时序电压限制,可能会将错误的数据写入到与此写

入命令寻址的内存位置。

在示例中,图TBD中,与写入突发相关的相关触发边缘与时钟边缘相关联:Tn,Tn+0.5,Tn+1,...,Tn+8.5

从该位置后续的读取可能导致不可预测的读取数据,但DRAM在其他方面将正常工作。

4.8.7.3 脉冲和脉冲到时钟时序违反

如果与写入突发相关的任何触发边缘的触发时序要求(tWPRE,tWPST)或触发与时钟的时序要求(tDQSS,

tDQSoffset)被违反,可能会将错误的数据写入到与该有问题的写入命令寻址的内存位置。从该位置后续的

读取可能导致不可预测的读取数据,然而DRAM在其他方面将正常工作,只需满足以下约束条件:

1. 写入CRC和数据突发OTF均被禁用;未违反tWPRE,tWPST,tDQSS,tDQSoffset以外的时序规格。

2. 有问题的写入触发(和前导)不早于或晚于Write-Latency位置之后的六个DQS转换边缘。

3. 在任何开启的存储区后面跟随有问题的写入命令时,允许进行读取命令。

4. 可以在tCCD_L延迟后发出一个或多个后续的WR或后续的WRA(与有问题的WR相同的存储区),但可能会写

入错误的数据;后续的WR和WRA可以是有问题的或非有问题的写入。从这些写入中读取可能会提供错误的

数据。

5. 可以在tCCD_S延迟后发出一个或多个后续的WR或后续的WRA(到不同的存储区组),但可能会写入错误的

数据;后续的WR和WRA可以是有问题的或非有问题的写入。从这些写入中读取可能会提供错误的数据。

6. 一旦在有问题的写入命令之后向DDR5发出一个或多个预充电命令(PREpb,PREsb或PREab),并且所有存

储区变为预充电状态(空闲状态),后续的非有问题的WR或WRA到任何开启的存储区都应能够写入正确的

数据。

7. DQS触发器(包括前导)必须与每个写入命令的数据突发长度配置对齐。如果由于对齐错误或缺失触发边

缘而导致DRAM无法捕获或错误地解序列化传入的数据流,可能会发生错误。这些错误将无限传播,直到

DRAM进入空闲状态,即所有存储区都处于预充电状态且满足tRP。

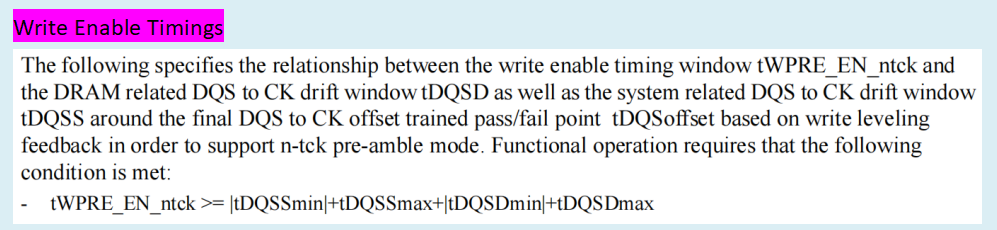

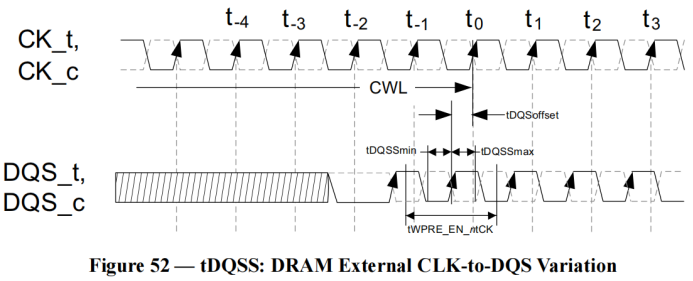

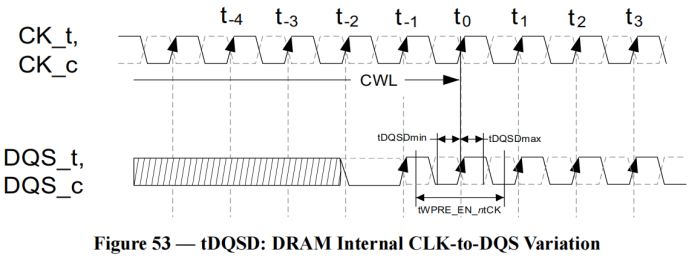

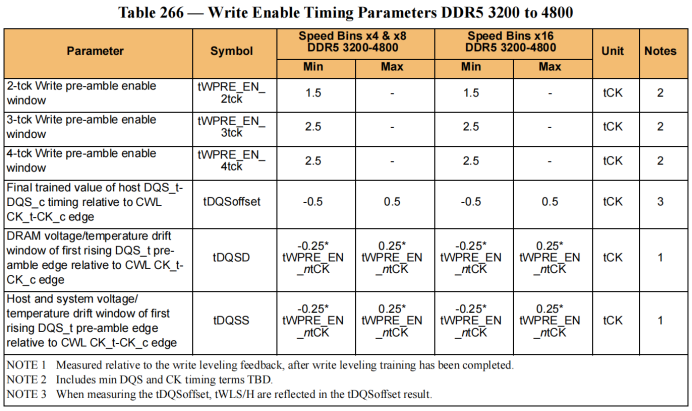

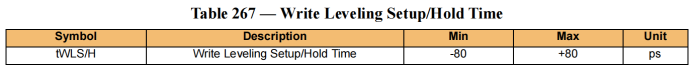

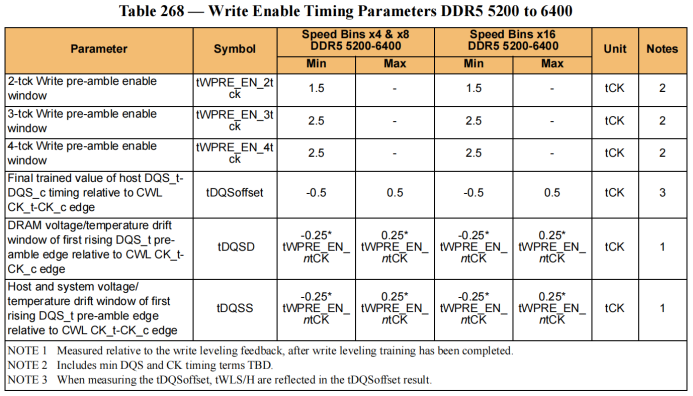

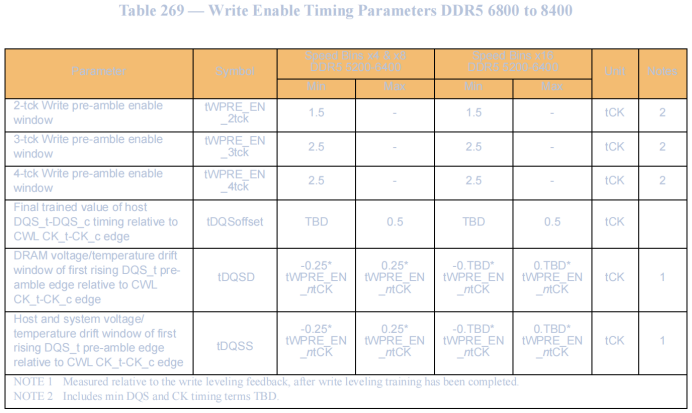

4.8.8 写使能时序

下面说明了写使能时序窗口tWPRE_EN_ntck与DRAM相关的DQS到CK漂移窗口tDQSD以及系统相关的DQS到CK漂移

窗口tDQSS之间的关系,以及基于写入平衡反馈的最终DQS到CK偏移训练的通过/失败点tDQSoffset,以支持

n-tck前导模式。功能操作要求满足以下条件:

357

357

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?