3 功能描述-5Mode Registers

3.5 模式寄存器

在DDR5中,利用率和编程方法将从DDR3和DDR4中的传统 addressing scheme 改变,并将转移到LPDDR使用的方法中,其中模式寄存器地址(MRA)和放置在操作码(OP)中的有效负载都以数据包的形式进行命令总线编码。请参考表241了解模式寄存器读取(MRR)和模式寄存器写入(MRW)命令协议。

对于DDR5,SDRAM将支持最多8个MRA,每个MRA带有一个字节宽的有效负载。这样可以支持最多256个字节宽的寄存器。

utilization:利用,使用

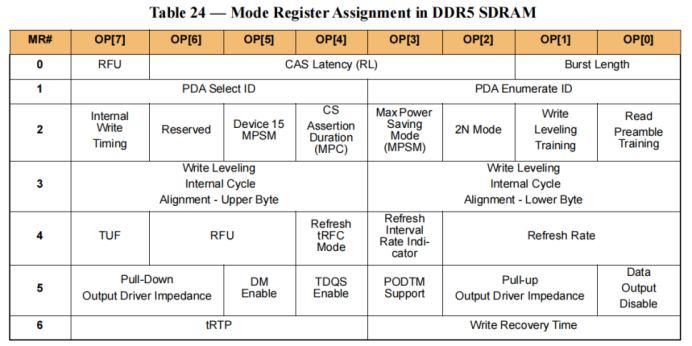

通过模式寄存器,可以对SDRAM的特性、功能、设置进行编程。

这些寄存器通过MRW命令进行配置;

模式寄存器一般在初始化期间进行设定,但也可以在后续正常工作时间修改。

DDR5将改变DDR3和DDR4中传统的寻址方案,转而采用LPDDR使用的寻址方案,其中模式寄存器地址(MRA)和操作码(OP)中的有效载荷都将封装在命令总线编码方法中。请参阅表241,了解DDR5中模式寄存器读取(MRR)和模式寄存器写入(MRW)命令协议。

在DDR5中,SDRAM将支持最多8个MRA,每个MRA的有效载荷宽度为1字节,这将允许最多256个1字节宽的寄存器。这种利用和编程方法的变化将提供更多的灵活性和效率,以管理和访问DDR5内存系统中的数据。

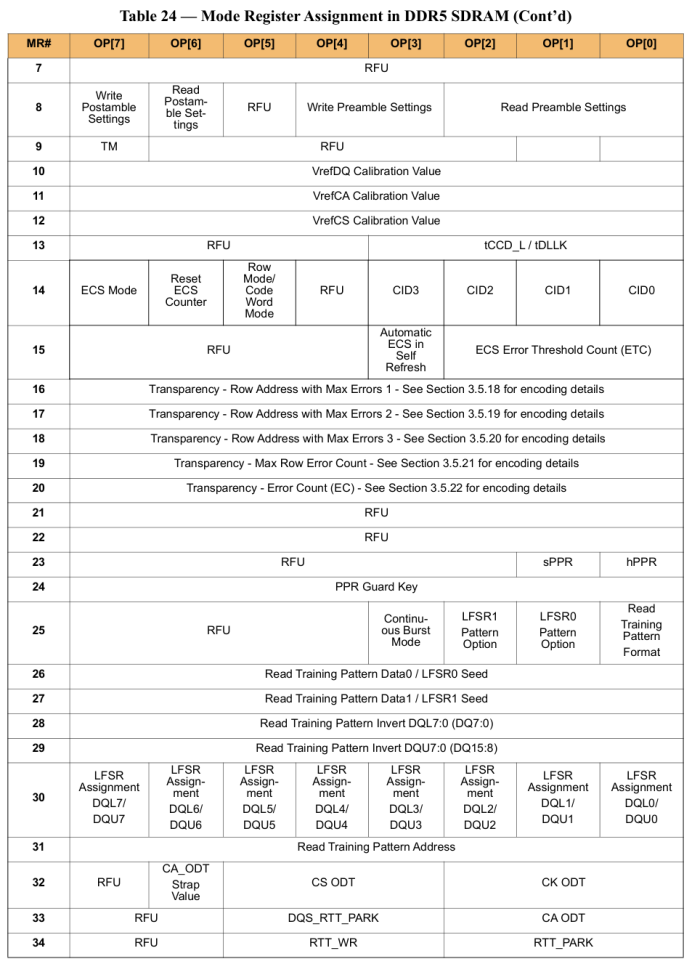

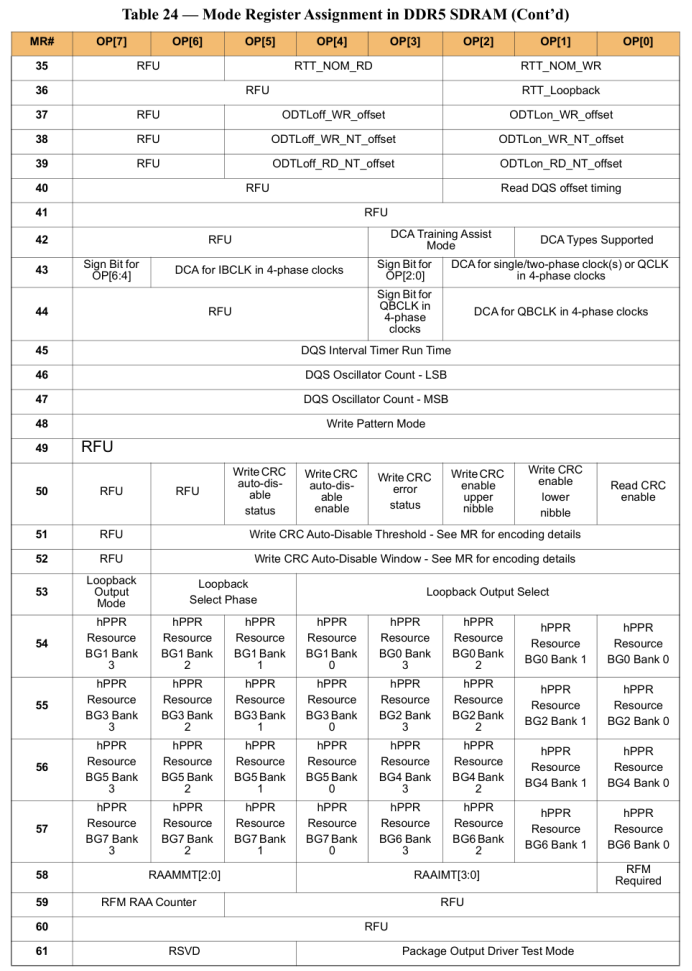

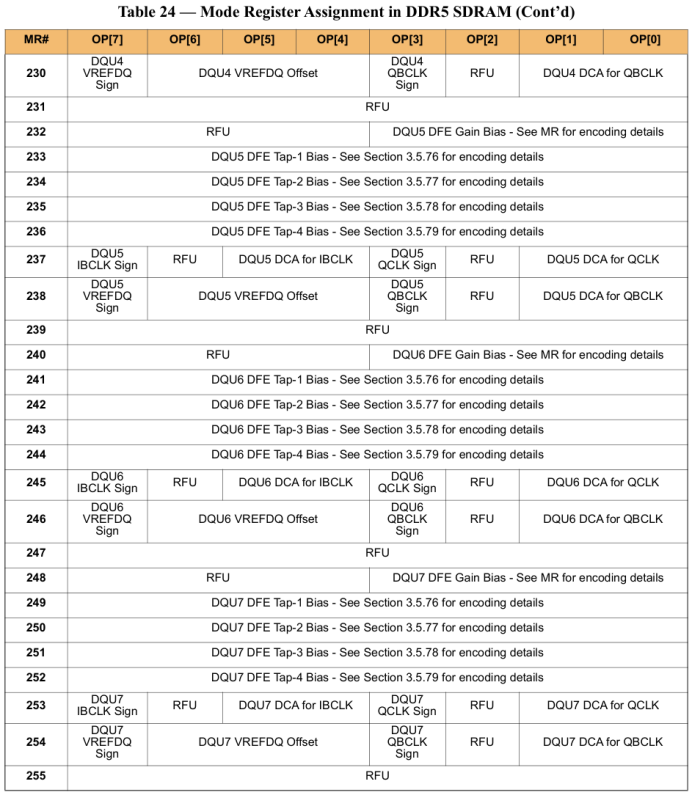

3.5.1 DDR5 SDRAM中模式寄存器分配和定义

表格24展示了DDR5 SDRAM的模式寄存器。在一个寄存器字节(MR#)中,每一位都被标注为“R”,如果它可以读取但不能写入;标注为“W”,如果它可以写入但读取该位将始终产生零;标注为“R/W”,如果它既可以读取又可以写入。此外,将只读DRAM位与仅主机可写的位组合在一起被标注为“SR/W”位。该位允许DRAM在读取该位时返回定义的状态(SR = 状态读取),与主机可能写入的位无关。

denote:表示,指示

R:可读,不可写

W:可写,读返回0

R/W:可读,可写

SR/W:状态读,即这个bit可以被host写,读的时候,将写入的状态读出来。

R,W,SR/W表示的都是某个bit的属性

定义的寄存器字节(MR#)是至少有一个位被定义的任何MR#。

当整个MR#被标记为RFU(保留未来使用)时,它被视为未定义,并且来自DRAM的所有位于读取或写入时都是不关心的。这些未定义的模式寄存器(完全为空的字节,而不是MR的单个位)可能不受DRAM的支持。当定义的寄存器字节(MR#)包含“RFU”位时,主机必须将这些特定位写入零,并且DRAM不保证这些特定RFU位的任何操作。当主机对包含RFU位的已定义寄存器(MR#)发出MRR时,这些特定位始终产生零。

在DDR5 SDRAM中,MR#(模式寄存器)是用于存储配置设置的寄存器,其中每个寄存器字节(MR#)包含被指定为“R”、“W”或“R/W”的单独位,具体取决于它们是否只能读取、写入或同时可读写。在某些情况下,某个位可能被指定为“SR/W”,这意味着DRAM可以读取该位,并由主机进行写入,但是DRAM将在读取操作期间返回预定义的状态,与主机写入该位的值无关。此功能可在DDR5内存系统中提供更多的灵活性和控制,以管理和访问数据。

如果整个MR#都标记为RFU(保留未来使用),则它被视为未定义的,并且来自DRAM的所有位都将被忽略以进行读取或写入。这些未定义的模式寄存器可能不受DRAM支持。

如果定义的寄存器字节(MR#)包含RFU位,则主机必须为这些特定位写入ZERO。DRAM不保证这些RFU位的任何操作。当主机向包含RFU位的定义寄存器(MR#)发送模式寄存器读取(MRR)命令时,这些特定位始终产生ZERO。

RFU:未定义

(1). 整个MR所有bit都未定义,意味着,DRAM不必关心这个MR是否可读/可写,这样的MR可能不被DRAM支持;

(2). MR中包含部分未定义的bit,host必须在这些bit写0,且DRAM不能保证这些RFU bit的任何操作;

(3). 当host发出一个MRR命令,给定义好的MR,这个MR如果包含RFU bit,这些bit位将产生0。

MR定义不同配置和容量时,有以下规则:

(1). DRAM是x4/x8配置,这个MR仅用于x16配置,则这个MR被认为是RFU,这些bit位不关心读/写,可能不被DRAM支持;

(2). 当某些MR bits字段定义的配置/容量和DRAM不同,host可能也会向这些字段写值,但DRAM的操作不会被影响。

(3). MRR命令用于读一个MR,MRW命令用于写一个MR。

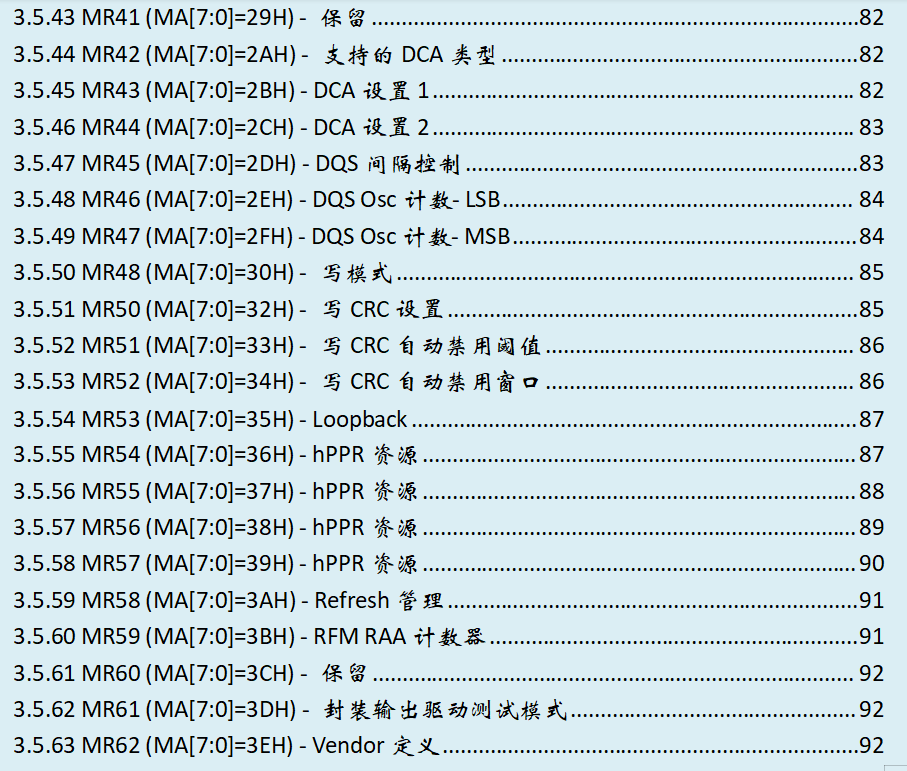

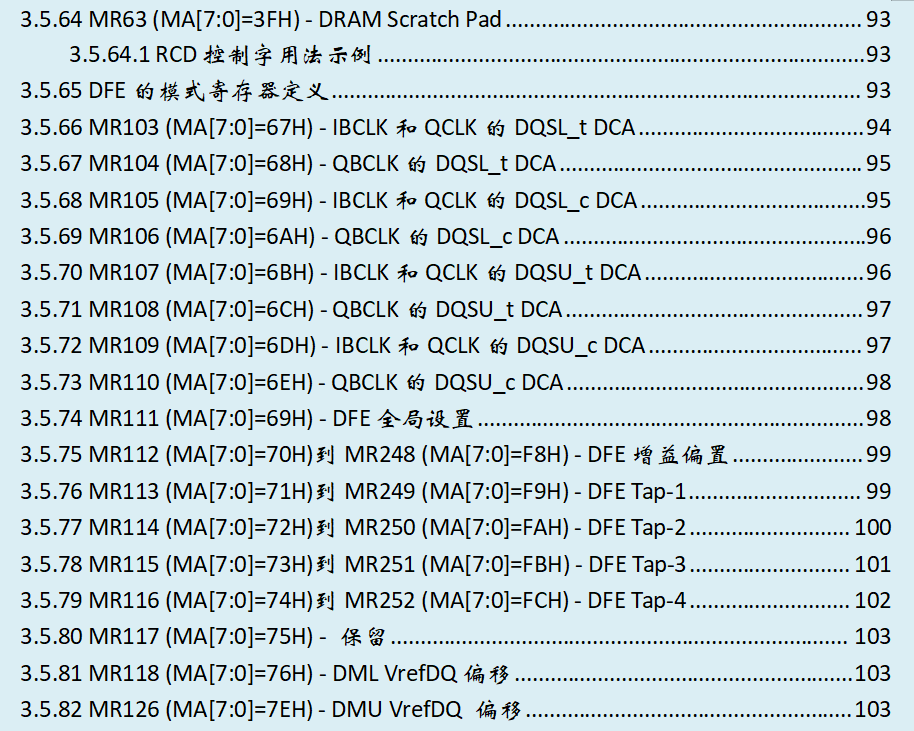

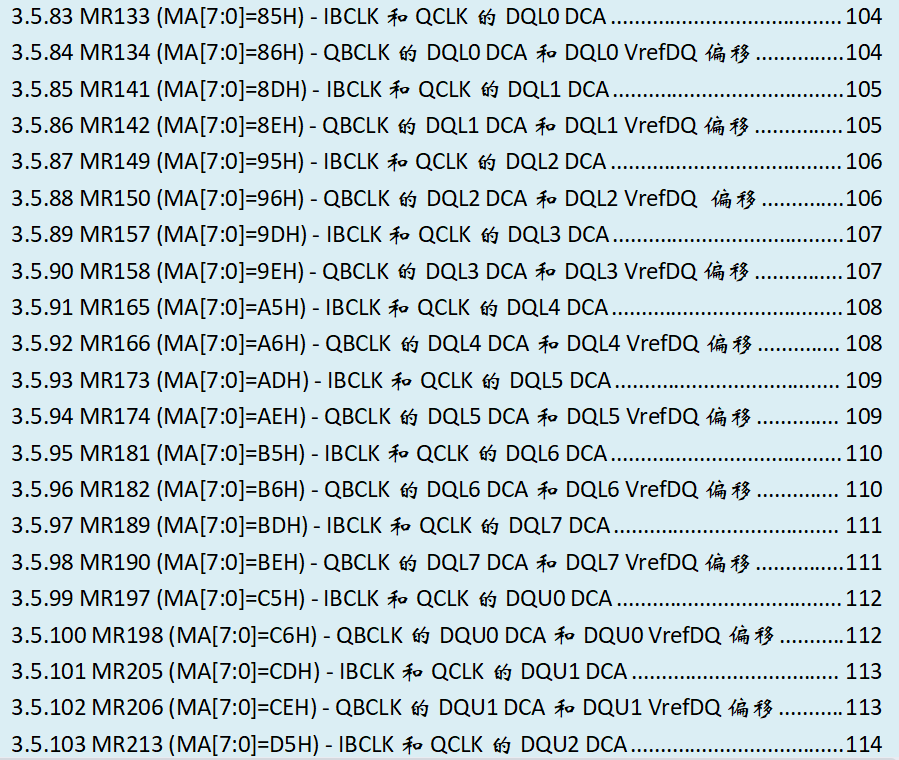

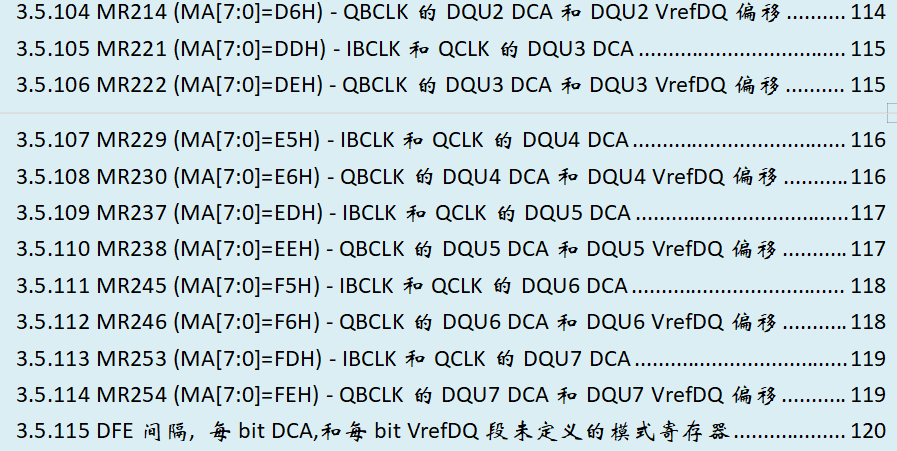

模式寄存器目录

本文详细介绍了DDR5SDRAM中模式寄存器的改变,包括地址分配、编程方法和命令协议。模式寄存器用于配置SDRAM特性,支持8个MRA,每个带1字节有效负载。寻址方案更新,MRR和MRW命令引入,以提高灵活性和效率。

本文详细介绍了DDR5SDRAM中模式寄存器的改变,包括地址分配、编程方法和命令协议。模式寄存器用于配置SDRAM特性,支持8个MRA,每个带1字节有效负载。寻址方案更新,MRR和MRW命令引入,以提高灵活性和效率。

1180

1180

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?