5 片上终端-2(ODT Modes, Timing Diagrams and State Table)

5.2 ODT模式,时序图和状态表

DDR5 SDRAM的ODT模式有5种状态,终结电阻禁用,RTT_WR,RTT_NOM_RD,RTT_NOM_WR和RTT_PARK。ODT模式受控于下面列表中MR对RTT设置。

进入自刷新模式后,DRAM自动禁用ODT,设置终端状态为高阻态,忽略这些设置。

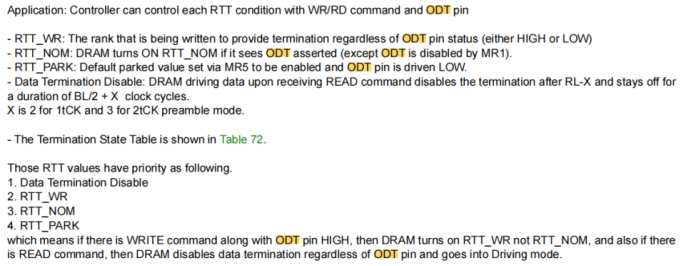

控制器用WR/RD命令和ODT Offset Control MR控制RTT。

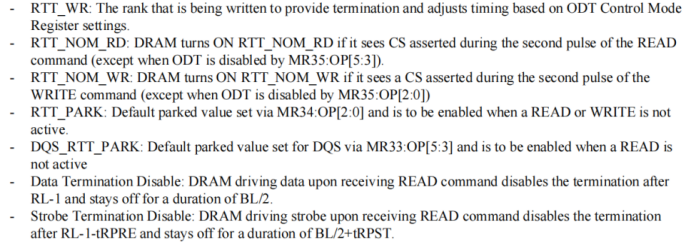

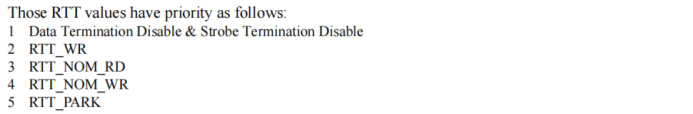

RTT_WR:每个正在被写入的rank基于ODT Control MR 设置配置此值并调整时序;

RTT_NOM_RD: DRAM READ命令的第二脉冲的CS置高时,终结电阻转为此值;(MR35:OP[5:3] disable ODT时除外)

RTT_NOM_WR: DRAM READ命令的第二脉冲的CS置高时,终结电阻转为此值;(MR35:OP[2:0] disable ODT时除外)

RTT_PARK:READ或者WRITE命令未激活时,默认的阻值,由MR34:OP[2:0]确定;

DQS_RTT_PARK:READ命令未激活时,DQS默认的阻值,由MR33:OP[5:3]确定;

Data Termination Disable:终结电阻禁用,DRAM收到READ命令后,在输出读返回数据时,在时间RL-1后保持BL/2 个时钟周期内将终结电阻禁用。数据驱动

Strobe Termination Disable:终端电阻禁用,DRAM收到READ命令后,在输出读返回数据时,在时间RL-1-tRPRE后保持BL/2 + tRPST 个时钟周期内将终结电阻禁用。选通驱动

这就意味着,如果有一个WRITE命令,DRAM的激活rank打开RTT_WR,而不是RTT_NOM_RD或者RTT_NOM_WR;如果是一个READ命令,DRAM禁用终端电阻并且进入驱动模式;

如果一个READ或者WRITE命令的第二脉冲,有CS使能,非目标rank的ODT被使能,并且有合适的RTT_NOM_RD或者RTT_NOM_WR值;

这为channel上的其它(非目标)rank提供了不同终端电阻选择的可能。

这里与DDR4比有调整,如下为DDR4的:

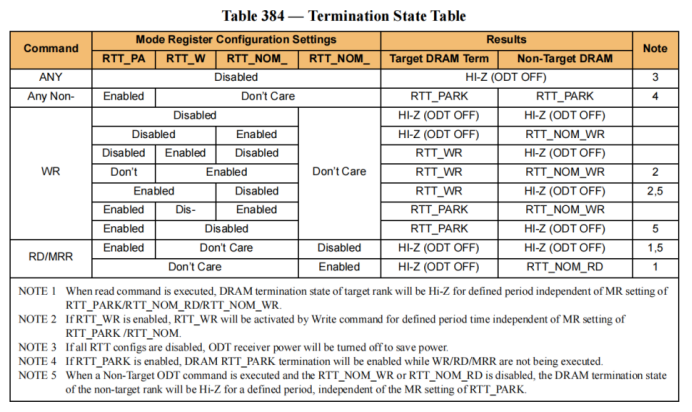

注意1:执行读取命令时,目标存储器排的终端状态将在定义的时间段内保持高阻态,独立于RTT_PARK/RTT_NOM_RD/RTT_NOM_WR的模式寄存器设置。

注意2:如果启用了RTT_WR,在定义的时间段内,写入命令将激活RTT_WR,独立于RTT_PARK/RTT_NOM的模式寄存器设置。

注意3:如果所有的RTT配置都被禁用,ODT接收器的电源将关闭以节省电能。

注意4:如果启用了RTT_PARK,在执行WR/RD/MRR命令时,DRAM的RTT_PARK终端将被启用。

注意5:当执行非目标ODT命令且禁用了RTT_NOM_WR或RTT_NOM_RD时,非目标存储器排的终端状态将在定义的时间段内保持高阻态,独立于RTT_PARK的模式寄存器设置。

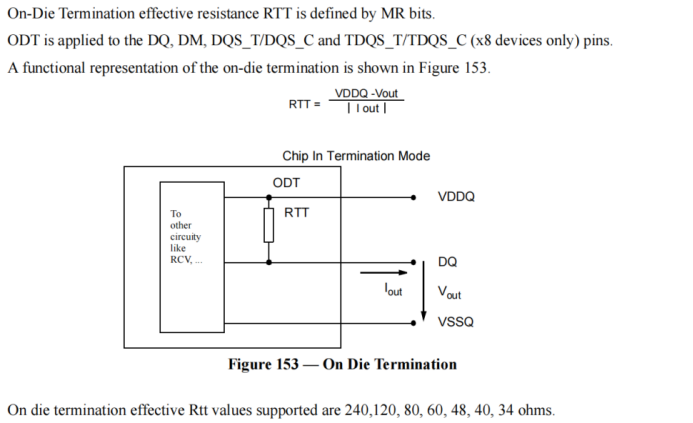

芯片内终端电阻的有效电阻RTT由模式寄存器位定义。

ODT应用于DQ、DM、DQS_T/DQS_C和TDQS_T/TDQS_C(仅适用于x8设备)引脚。

图153显示了芯片内终端电阻的功能表示。

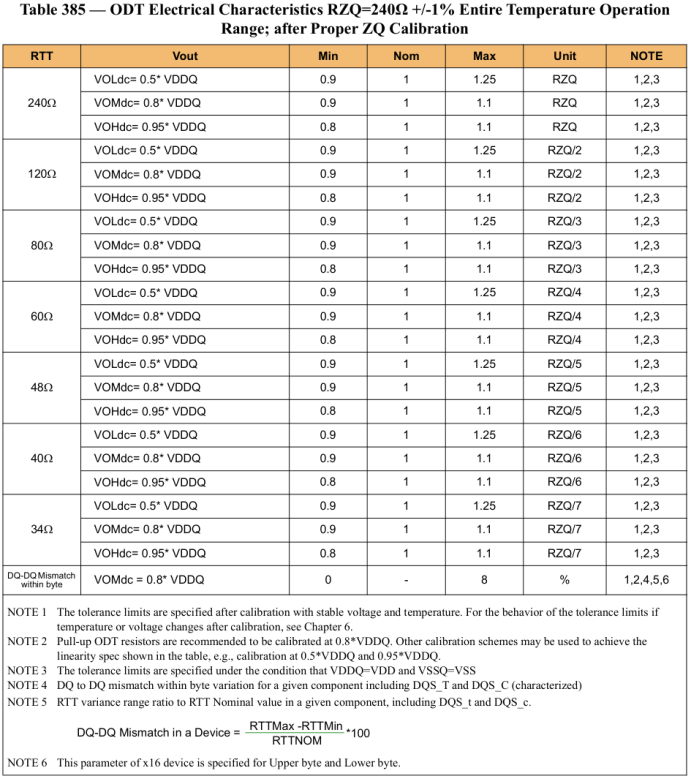

ODT典型表示及应用范围,有效的RTT取值。

注意1:在稳定的电压和温度下进行校准后,规定了容差限制。如果在校准后温度或电压发生变化,关于容差限制的行为请参阅第6章。

注意2:建议将上拉ODT电阻在0.8*VDDQ下进行校准。为了实现表中所示的线性规范,可以使用其他校准方案,例如在0.5*VDDQ和0.95*VDDQ下进行校准。

注意3:容差限制是在VDDQ=VDD和VSSQ=VSS的条件下规定的。

注意4:DQ到DQ的字节误差在给定的元件中包括了DQS_T和DQS_C(已经进行了特征化)。

注意5:给定元件中RTT变异范围与RTT标称值的比例,包括了DQS_t和DQS_c。

注意6:对于x16设备,该参数针对上字节和下字节进行规定。

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?