5 片上终端-3(Dynamic ODT)

5.3 动态 ODT

为了增强在某些应用下的数据总线信号完整性,需要DDR5 SDRAM在不使用MRS命令的情况下,能够改变终结电阻的强度。这种需求就需要支持“动态ODT”特性,如下所示。

5.3.1 ODT功能描述

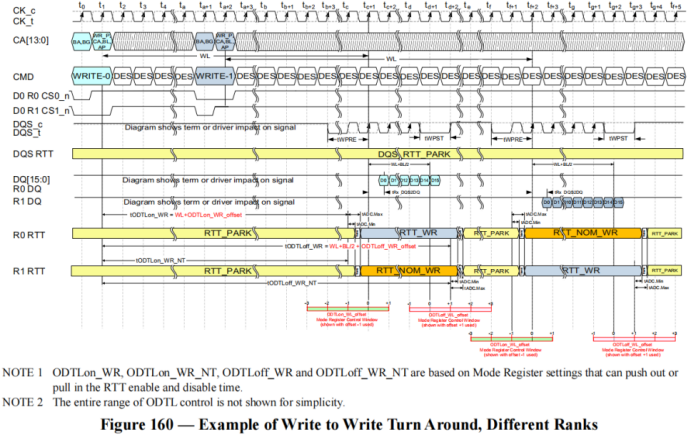

1. RTT有5种阻值可供选择;

2. 在无命令的操作中,终端电阻受控如下:

名义上讲,终端阻值可以在所有类型阻值(RTT_NOM_RD, RTT_NOM_WR, RTT_WR, RTT_PARK & DQS_RTT_PARK)之间选择;

RTT_NOM_WR&RTT_NOM_RD打开关闭,由NT写&读命令控制;

DQS_RTT_PARK取决于MR33被写入的值,并且保持不变。

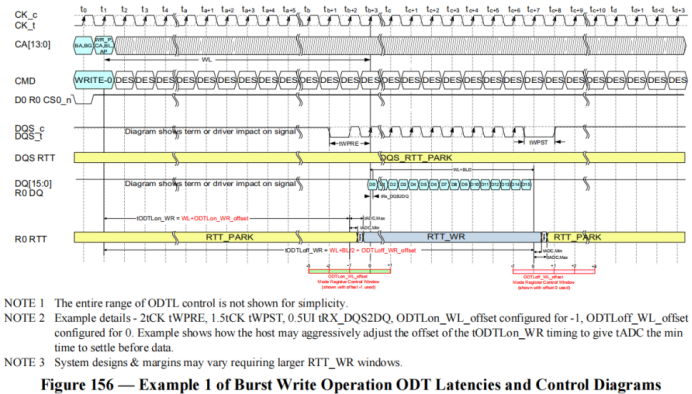

3. 当一个写命令被锁存时,终端电阻控制规则如下:

在写请求后的ODTLon_WR时间,终结电阻阻值变为RTT_WR;

在写请求后的ODTLoff_WR,RTT_WR阻值将被关闭;

4. RTT_NOM_WR,用于非写命令目标(rank),打开与关闭由延迟参数ODTLon_WR_NT and ODTLoff_WR_NT控制;

5. 当一个读命令被锁存时,终端电阻控制规则如下:

在读请求后的ODTLoff_RD时间,数据终结电阻被禁用;在读请求后的ODTLon_RD时间,终结电阻被启用;

在读请求后的ODTLoff_RD_DQS时间,选通终结电阻被禁用;在读请求后的ODTLon_RD_DQS时间,终结电阻被启用;

6. RTT_NOM_RD,用于非读命令目标(rank),打开与关闭由延迟参数ODTLon_RD_NT and ODTLoff_RD_NT控制;

duration:持续时间

violate:违反

一个读或写命令的持续时间是BL/2周期,终端电阻打开,关闭延迟设定不应该导致ODT脉冲的产生,即不能违背突发周期的最小持续时间;

应该设定ODTLoff_X - ODTLon_X >= BL/2(X=WR, WR_NT, RD_NT);

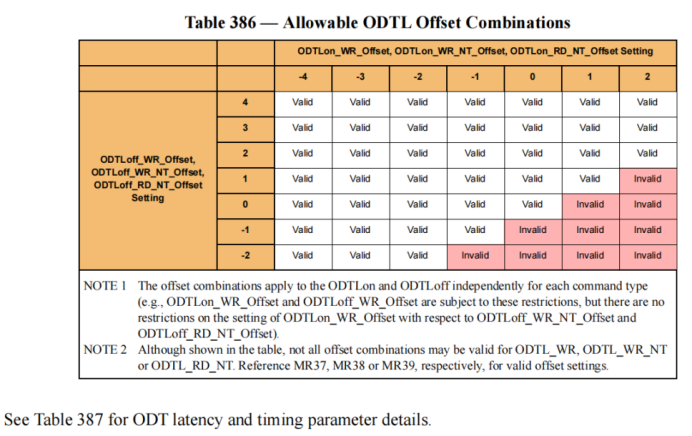

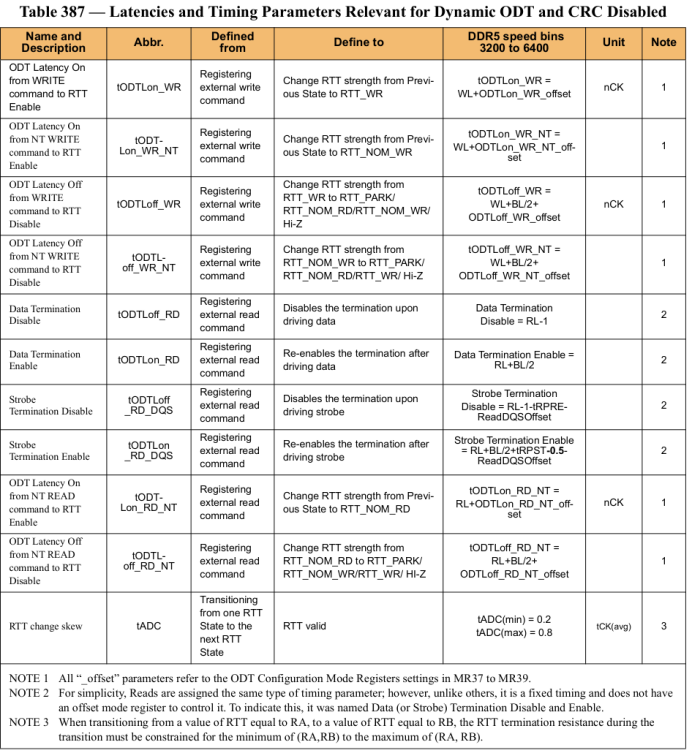

ODTLoff_X 和 ODTLon_X具体设定由MR进行设定,上面规定了WR ODT,WR NT ODT,RD NT ODT,ODT的组合见下表:

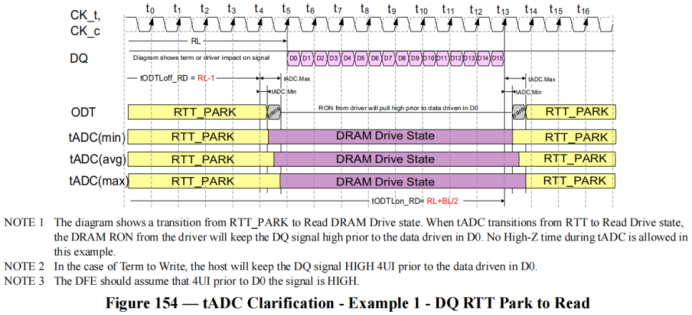

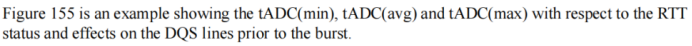

5.3.2 ODT tADC澄清

tADC是DRAM从一个RTT状态到下一个RTT状态需要花费的时间,如读的条件下,是从RTT状态到DRAM驱动状态的时间。在tADC范围内,只要RTT没有被无效,不允许高阻态状态的存在;

在DRAM驱动状态,第一次DQ转变前,DRAM RON应该保持DQ信号拉高;DFE应该假定4UI先于D0信号拉高。

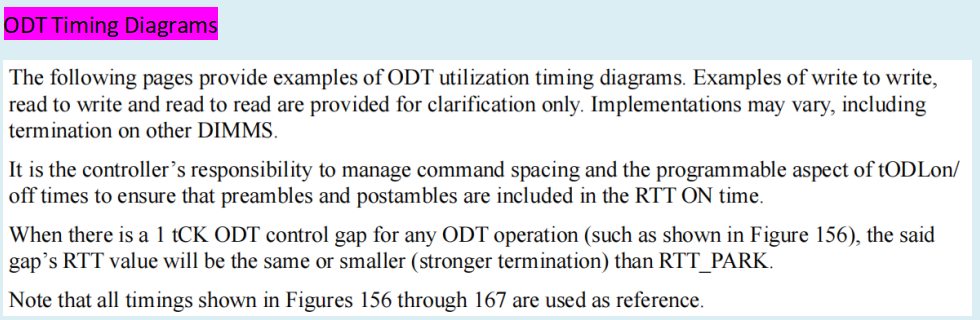

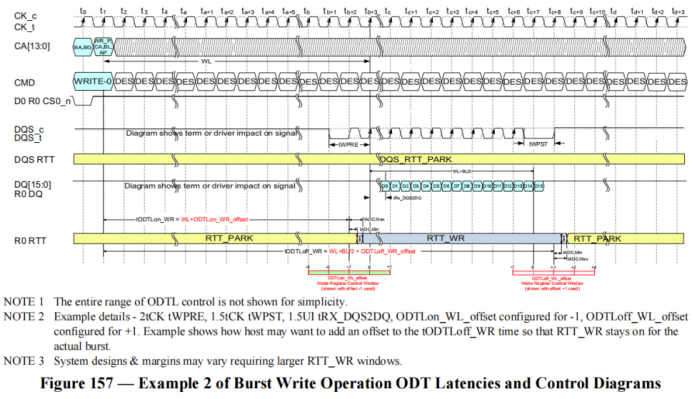

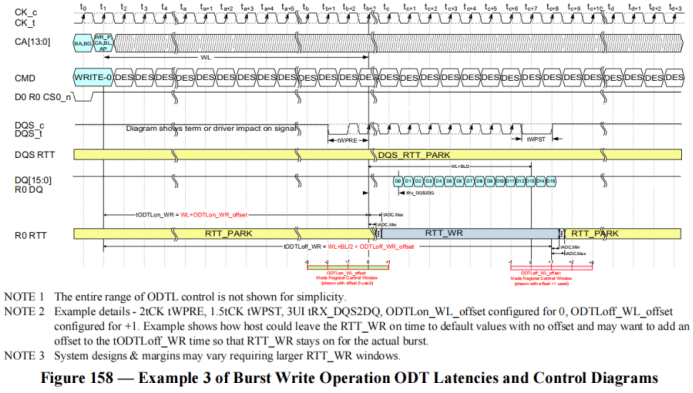

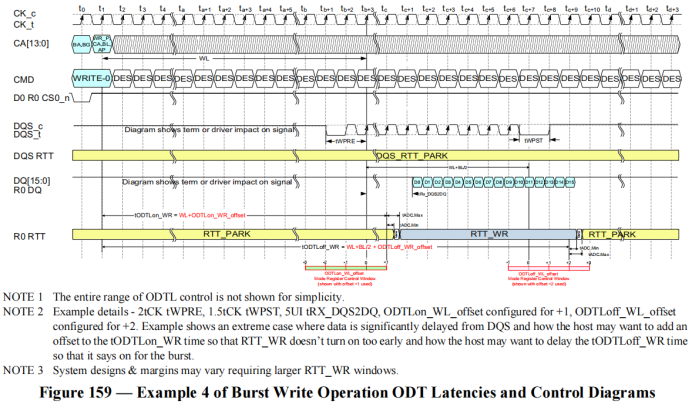

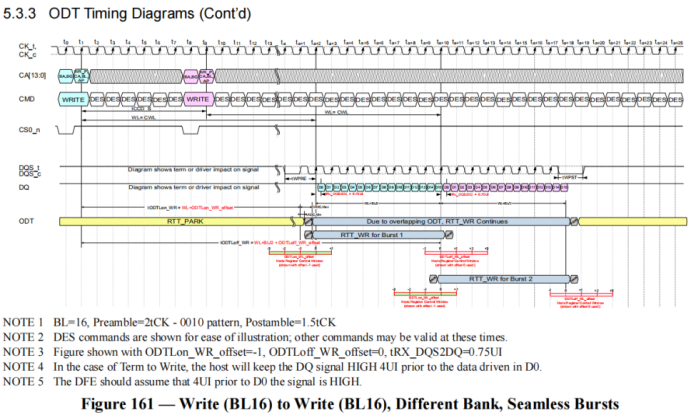

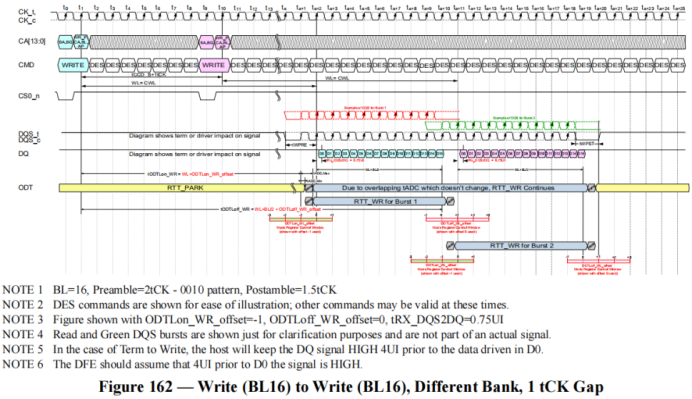

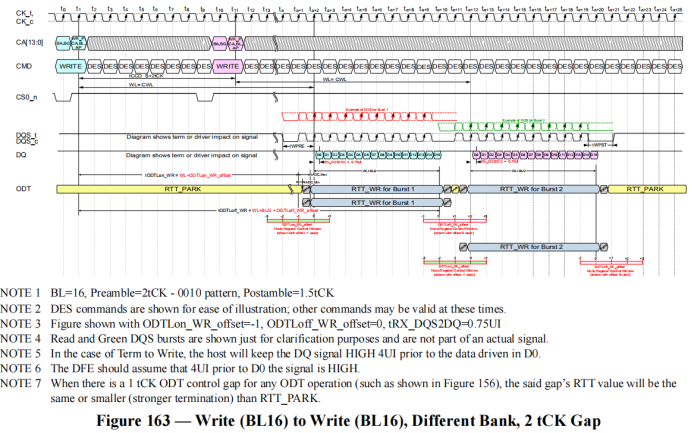

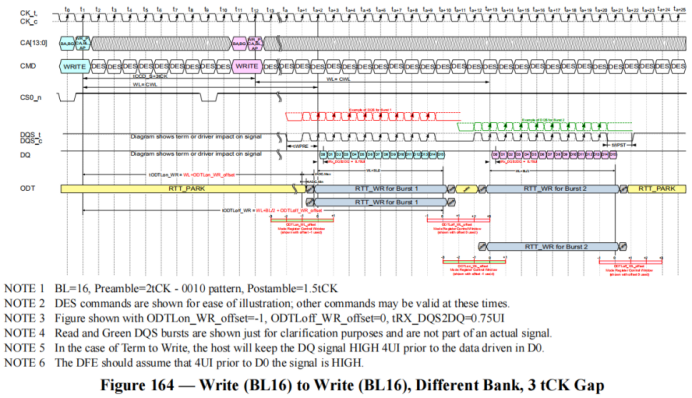

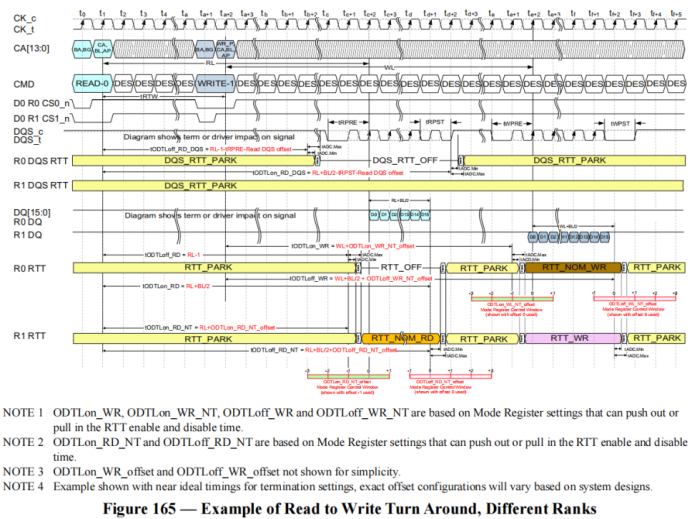

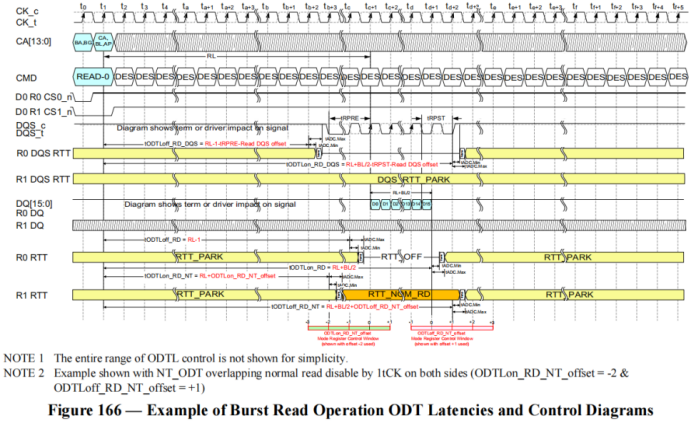

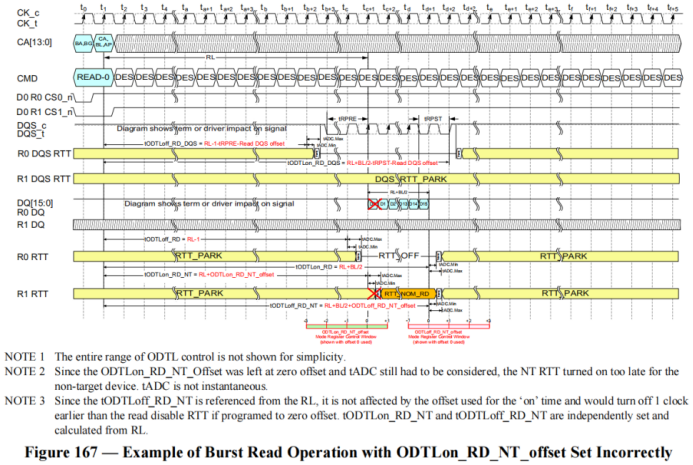

5.3.3 ODT时序图

下面几页举例ODT使用的时序图解;写到写、读到写、读到读的图解仅用于说明,完全体可能更复杂,包括其它DIMMS的终端电阻。

控制器应当管理命令空间和调整tODTLon/off时间,保证前导和后导包含在RTT ON时间内。

如图156所示,当ODT操作有一个1 tCK控制间隙,该间隙RTT的值应该小于等于RTT_PARK。

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?