| 锁定范围 | 高于PLL最大锁定范围 比VCO的调谐范围更宽 | type2 PLL为欠阻尼电路会过冲,超过目标频率 |

| 最大工作频率 | 轨到轨摆幅输入的单端逻辑电路 | 高频数字电路产生的开关噪声会通过衬底噪声耦合影响VCO的噪声性能 可提供紧凑的面积和低功耗 |

| 差分摆幅输入的CML电路 | 最大工作频率更高 噪声耦合小,首选 |

- 由于分频器的功耗和速度性能主要取决于前端预分频器,

- 预分频器的工作基于数字锁存器和逻辑电路,因此主要的设计工作在于高速锁存器的低功耗设计。

1. 标准逻辑分频器

当用CMOS逻辑电路设计锁存器时,可以考虑静态逻辑电路或动态逻辑电路。

| 静态锁存器 | 动态锁存器 真单相时钟(TSPC) | |

| 优点 | 更快的速度 更低的功率 | |

| 低功率、紧凑面积和无偏置电流 | ||

| 很受欢迎:不需要互补时钟和非重叠时钟生成电路 | ||

| 缺点 | 最小工作频率 (动态锁存器中的动态充电节点不能长时间保持电压,导致低频时钟故障) | |

| 对工艺、电压和温度(PVT)变化高度敏感 | ||

| 更依赖于物理布局,需要仔细的布局后仿真 VCO和分频器之间的距离太远,则由于寄生电容增加,预分频器输入端的上升沿和下降沿会变慢或压摆,这会导致正反馈锁存器无法正确翻转先前状态的情况。 VCO和预分频器距离太近,VCO可能会受到基板噪声耦合的影响 | ||

动态锁存器先进的CMOS技术可用

2. 电流型逻辑分频器(CML分频器)

CML锁存器采用差分输入,可实现高速工作、降低开关噪声,并具有良好的抗电源电压变化能力。

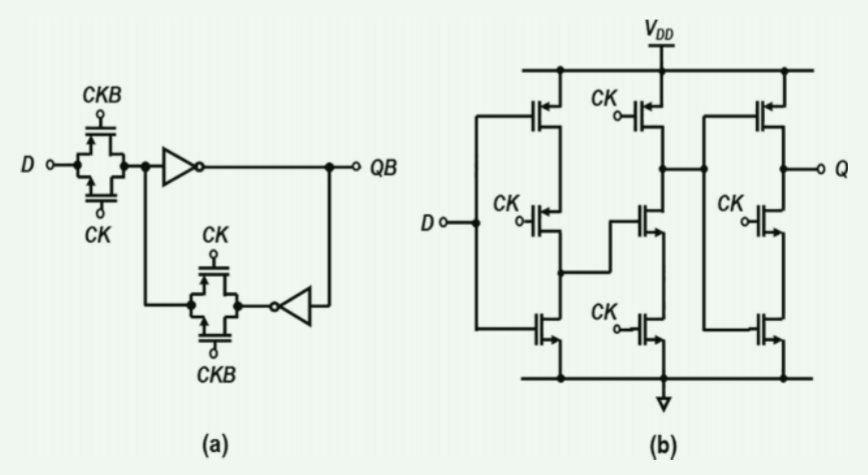

如图是一个使用主从CML锁存器的传统2分频电路,该锁存器在时钟上升沿产生输出。

主从CML锁存器通过使第二锁存器的反相输出连接到第一锁存器的数据输入来形成TFF。

CML锁存器也可以在没有尾偏置电流的情况下工作,但是性能对电源电压高度敏感,除非像伪差分逻辑那样假设大的电压摆幅。

电流偏置和晶体管尺寸会影响CML锁存器的速度和输入灵敏度,因此CML锁存器的设计过程需要考虑以下几个设计因素:

- 输入敏感度:

【保证CML分频器功能鲁棒性】

- 最大频率:

- 功耗:

- 电压幅度:

【确定速度、功率、DC净空和CML鲁棒性的重要设计参数】

- DC净空

- 小信号增益和噪声

单个CML锁存器可以分析为一个两级电路,

其功能类似于由一个前置放大器和一个正反馈锁存器组成的比较器。如果第一级放大器的增益不够高,则第二级处的交叉耦合锁存器不能正确地翻转状态。

普通差分放大器的输入灵敏度取决于偏置电流和晶体管尺寸。

2.1 输入敏感度

在常规差分放大器中,足够电流导引的最小差分输入电压:

:输入晶体管过驱动电压

:尾电流

:NMOS的电子迁移率

:氧化物电容

设计一个具有小负载电阻和大尾电流的CML锁存器以实现高速工作可能会遇到输入灵敏度差的问题,特别是当所有晶体管都设计为具有小W/L比以最小化寄生电容时。

简单地增加偏置电流以获得较大的电压摆幅并不能解决输入灵敏度问题,因为它还会增加

。

如果使用差分输入晶体管的高W/L比来提高输入灵敏度,则高W/L比会增加分频器自身输出节点处的寄生电容以及前一级的负载电容,从而显著降低给定偏置电流下分频器的最大速度。

另一个注意事项是,输入波形的幅度和斜率对于输入灵敏度都很重要。

这是因为具有缓慢上升沿或下降沿的输入波形导致输入对晶体管的长时间同时导通重叠。

例如,当输入信号像三角波形一样摆动时,即使是大的输入波形也可能导致电流导引不足。

压摆波形的产生是因为负载电容较大,VCO和分频器相距较远时通常会出现这种情况。

因此,保持输入波形的快速上升和下降时间对于CML分频器的鲁棒功能来说是重要的,但代价是增加功率。

2.2 最大工作频率

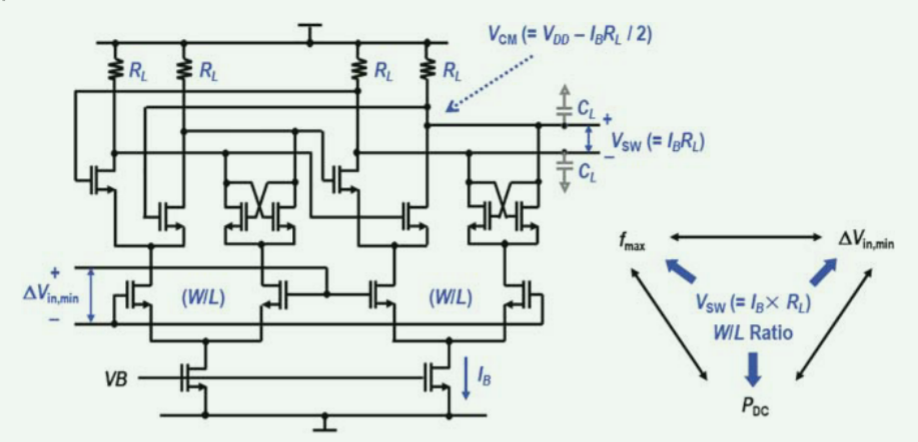

最大速度主要由输出节点处的RC时间常数确定。

- 电阻由负载电阻RL设置,

- 而负载电容CL输出节点处的所有寄生电容之和

- 包括下一级中的输入晶体管的栅极氧化物电容。

如果不改变晶体管尺寸和电压摆幅,提高速度的唯一方法是降低电阻并增加偏置电流。

增加偏置电流而不改变晶体管尺寸会降低输入灵敏度。

因此,在最大工作频率和输入灵敏度之间存在基本的折衷。

- 在CML分频器的设计中,输入灵敏度的最坏情况可能发生在快速拐角工艺和高温下。这是因为快速转角工艺具有较低的RL值,而高温会降低晶体管的移动性,从而为小信号增益提供最差条件。

- 另一方面,最大速度的最坏情况条件发生在慢角工艺和高温度下,因为慢角工艺在输出节点处给出大的RC时间常数,而热温度使晶体管变慢。

- 为了正确设计CML分频器,必须运行两种最坏情况条件,即高温下的快转角和慢转角工艺。

2.3 电压摆幅

电压摆幅是确定速度、功率、DC净空和CML鲁棒性的重要设计参数。

- 它应充分大于ΔVin,min【

】,以确保稳定运行。

- CML锁存器的小信号增益必须充分高于1,以进行适当的差分逻辑操作。

- 由于CML分频器是一个开关电路而不是放大电路,因此与VCO或电荷泵相比,具有足够VSW的CML分频器在PLL输出端的噪声贡献可以忽略不计。

- 在CML分压器中,电压摆幅也设置输出共模电压VCM。因此,如果电压摆幅太大,则随后的锁存器的输入共模电压太低而不能使尾晶体管在具有足够DC净空的饱和区域中操作。

当级联CML分频器用于分频器链时,对锁存器的任何修改都可能影响上一级或下一级锁存器的性能。

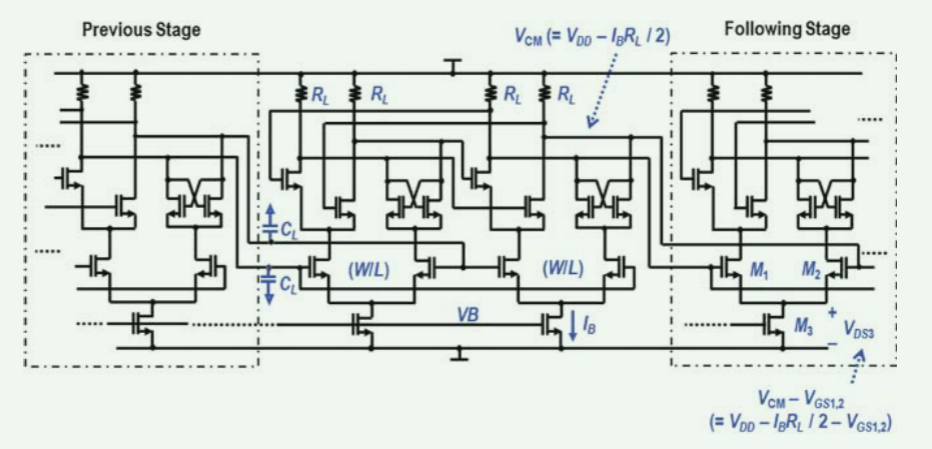

如图所示,说明在由三个级联的2分频电路组成的8分频电路设计中,

第二级分频器的变化影响第一级和第三级分频器。

| 第一级2分频电路设计为具有相对小的输出摆幅,以满足低功耗的最大速度 | |

| 第二级2分频电路的工作频率是第一级2分频电路一半,考虑稍大的输出摆幅 | |

| 增加输入级晶体管的尺寸 | 增加偏置电流 |

| 增加了第一级分压器的输出负载电容, 输出负载电容的主要部分由CoxWL给出。 | 降低输出共模电压 |

| 随着输出负载电容的增加,第一级分频器电路需要重新设计 | 下一级分压器的直流裕量较小,需要降低输出负载电阻的值。否则,下一级的电流镜可能由于有限的漏源电压而进入线性区。 增加偏置电流而不增加晶体管尺寸将降低输入灵敏度 |

例子:电压摆幅随工艺和温度的变化

- 电压摆幅-->速度、鲁棒

- 考虑电压摆幅随工艺和温度的变化

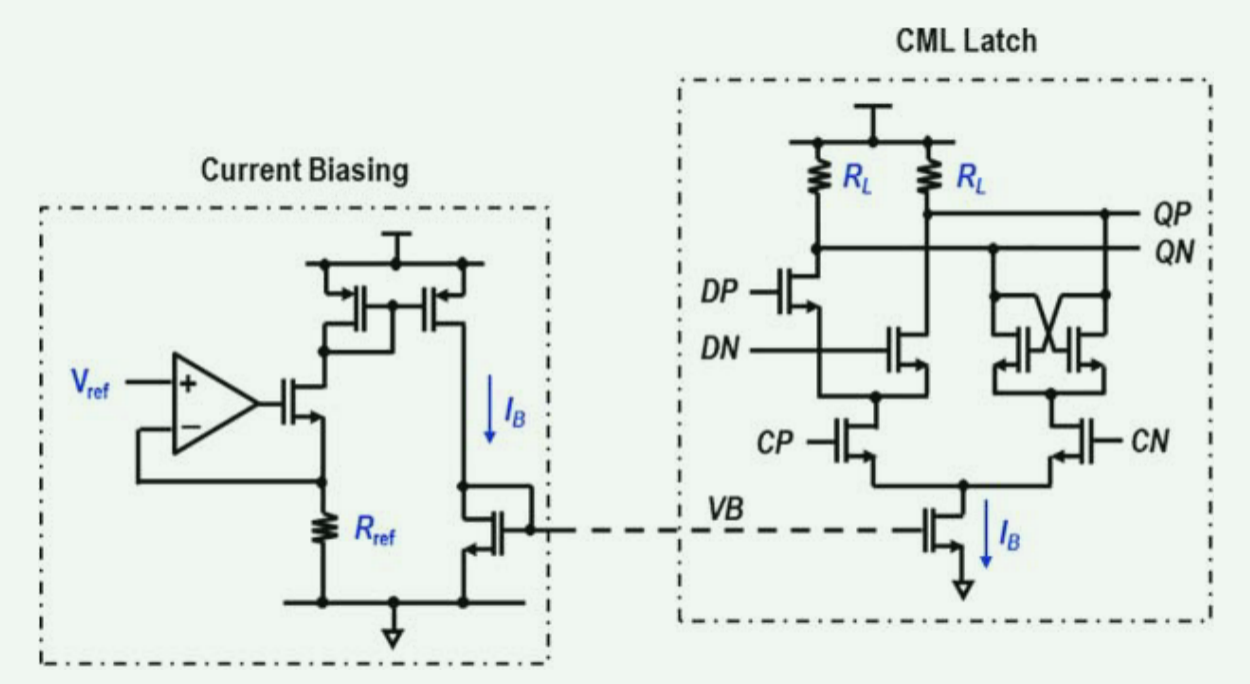

带隙基准电压Vref和片内电阻Rref用于产生CML分压器的偏置电流IB。电压摆幅Vsw:

- 如果电流生成电路和CML分压器都使用相同类型的电阻,则无论工艺和温度变化如何,都可以实现恒定的电压摆幅。

- 这种方法对于控制紧凑的DC裕量并避免在慢转角过程或高温下的速度降级是有用的。

- 当低电压摆幅被设计用于低功率和高速操作时,固定电压摆幅可能在慢转角或高温下对下一级造成不足的电流导引或输入灵敏度问题。

- 在这种情况下,可以考虑使用外部电阻或可编程基准电压的固定电流来代替带隙基准电压。

- 为了进一步增加电压摆幅以补偿高温下的灵敏度下降,还可以考虑以降低最大频率为代价的与绝对温度成比例(PTAT)电压。

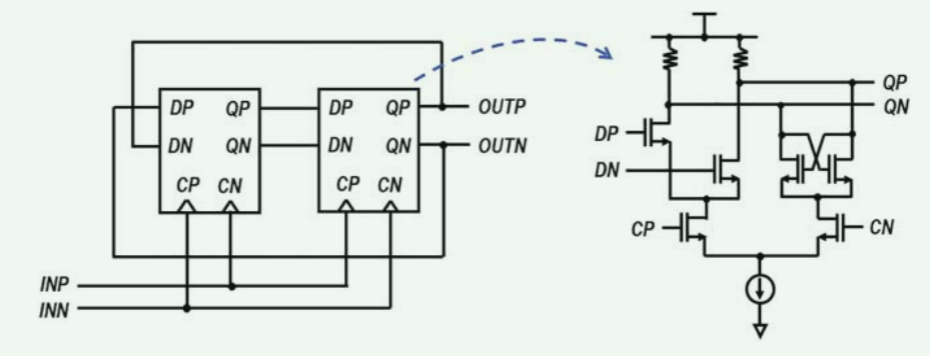

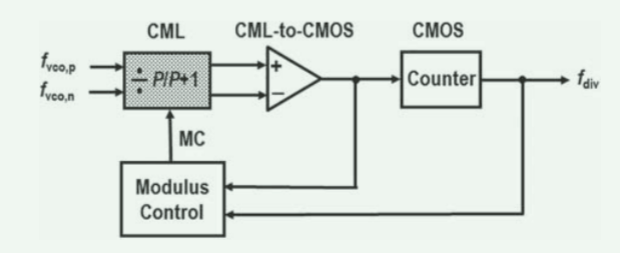

如图所示,由CML预分频器、CML至CMOS转换器、计数器和模数控制器组成。

- CML电路设计用于高速和低开关噪声,

- 低速计数器设计用于低功耗和紧凑的面积的标准CMOS逻辑。

- CML至CMOS转换器从差分输入产生单端轨到轨输出。

- 对于分频器的整体性能而言,模数控制器的时序有时比前端预分频器的速度更为关键。

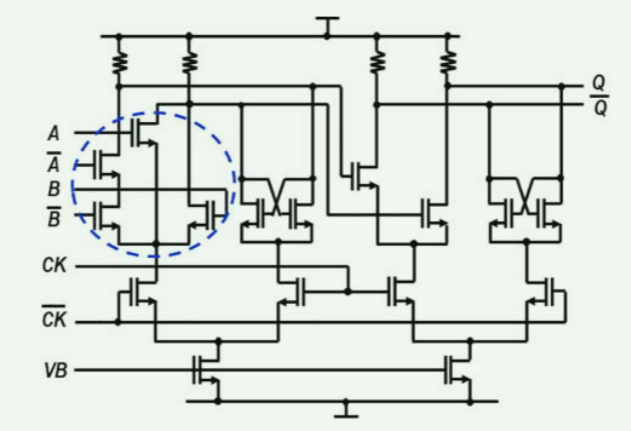

CML分频器嵌入逻辑门

CML分频器的电流导引操作使其易于使用嵌入式逻辑门来实现低功耗预分频器设计。

当一个合理的电压摆幅被假定时,如何保证所有的晶体管都处于饱和区??

- 事实上,在整个电压切换周期期间,所有晶体管都难以工作在饱和区。

- 除电流镜外,其它晶体管在电压摆幅达到最大或最小时,都可以工作在线性区。

- CMOS晶体管在线性区和饱和区之间的转换中是快速的,并且不会因为转换而减慢速度。

- 相比之下,双极晶体管从饱和区恢复线性区的速度较慢,

- 因此应在输出端添加一个射极跟随器,以提供适当的直流电平移位,这称为射极耦合逻辑(ECL)。

- 相反,在CMOS CML设计中由于显著的增益损失而不需要源极跟随器。

3. 模式控制的关键路径

3.1 设计挑战(32/33分频器)

预分频器是高速低功耗分频器设计中最关键的组成部分。

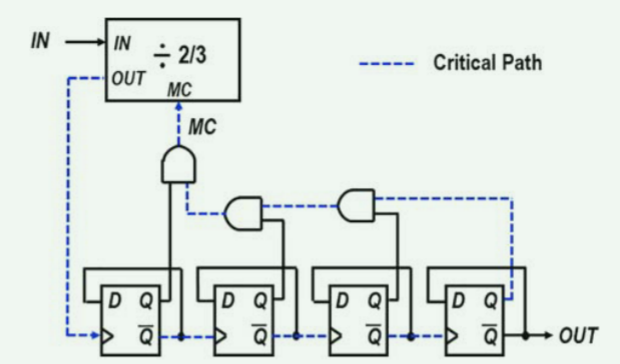

用于模控制的反馈路径不应被忽略,因为MC信号的定时裕度可能是高速分频器设计的瓶颈。

一个32/33 DMD的最大速度由MC信号路径限制,而不是预分频器限制。

32/33 DMD的MC信号由四个级联的TFF和几个逻辑门产生,以控制2/3预分频器。

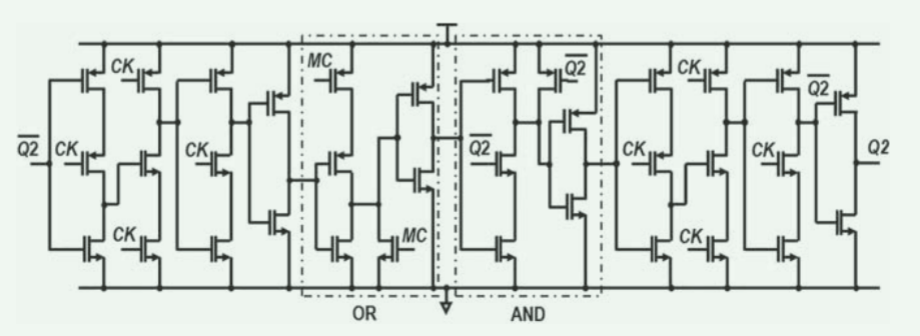

如图所示,MC信号的关键路径由四个TFF和三个与门的总延迟来设置。

- 如果2/3预分频器的输入频率为2 GHz

- 则2/3预分频器的MC信号路径的时间裕度应小于1 ns

- 因为2/3预分频器输出端的最小时钟周期为1 ns

- 在这种情况下,最小化MC信号延迟比设计2 GHz 2/3预分频器更具挑战性,

- 使得MC信号路径的延迟成为低功耗DMD设计的瓶颈。

3.2 缓解时序问题

在基于预分频器的分频器中,通过连接TFF和逻辑门,可以显著缓解MC时序问题。

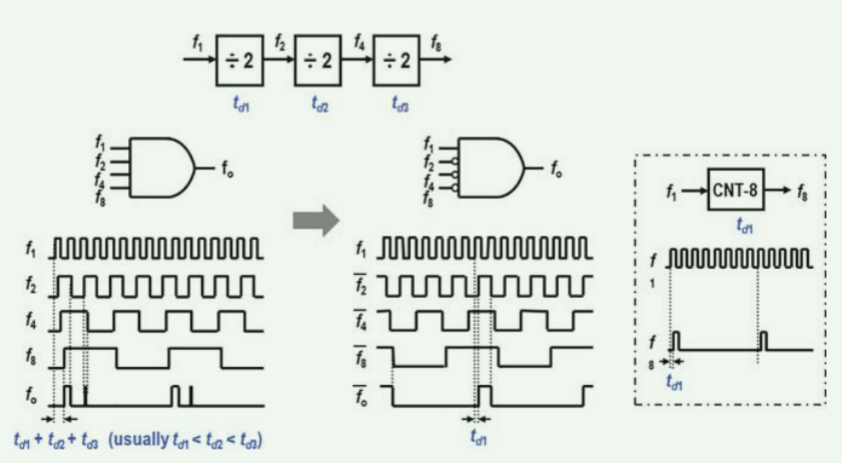

8分频电路由三个级联的TFF组成。

异步8分频计数器的总延迟由(td1 + td2 + td3)给出,其中td1、td2和td3分别是第一、第二和第三TFF的延迟时间。

与门的输出表现出来自级联TFF的累积时间延迟。

此外,由于第一个TFF的输出f2和第二个TFF的输出f4之间的重叠,可能会出现如图所示的毛刺波形。

如图所示,如果使用TFF的互补输出,

与门的输出只有第一个TFF的一个门延迟时间。

与门的输出不具有毛刺波形,因为f2完全嵌入在f4和f8的脉冲宽度内。

结果表明,后续TFF的栅极延迟并不重要,因为MC时序的关键路径由第一TFF的栅极延迟确定。

因此,即使使用异步计数器,我们也可以实现与同步计数器相同的延迟,从而充分利用基于预分频器的拓扑。

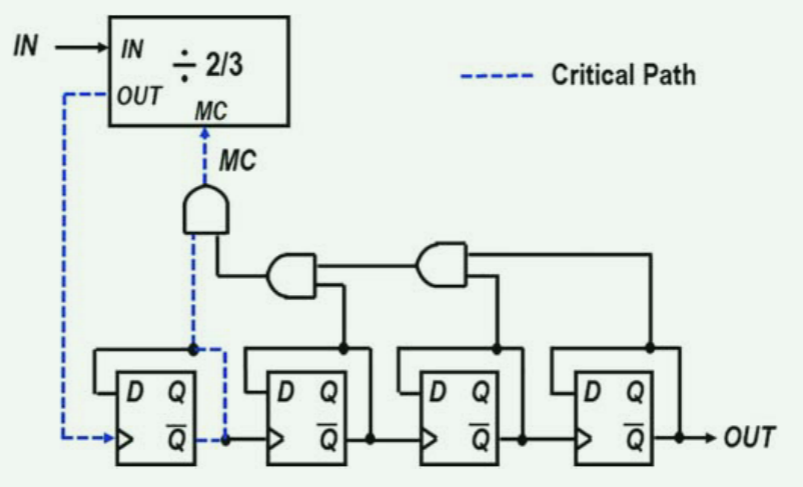

3.3 32/33分频器优化

TFF的互补输出Q用于模控制,

因此MC时序的关键路径由第一个TFF和一个与门的门延迟时间给出。

这样,64/65或128/129 DMD的MC信号路径的关键路径可以与32/33 DMD的几乎相同。

因此,对于低频TFF不需要保持相同的功率。

例如,128/129 DMD的总功耗与32/33 DMD的总功耗相当,因为额外的两个TFF可以仅消耗第一高频TFF的十分之一的功率。

957

957

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?