Vivado IP核之定点复数乘法器Complex Multiplier使用说明

配置步骤

IP核仿真测试

目录

前言

在数字信号处理、通信系统以及其他嵌入式应用中,复数运算是不可或缺的基础。Vivado设计套件作为Xilinx公司的一款强大工具,提供了丰富的IP核,其中复数乘法器(Complex Multiplier)是实现高效复数运算的重要组件。本文将说明Vivado IP核中的定点复数乘法器(Complex Multiplier)的使用方法,介绍该IP核的配置选项,并编写verilog代码测试了该IP核的累加功能。

提示:以下是本篇文章正文内容,各位在转载时附上本文链接。

一、Complex Multiplier IP配置步骤

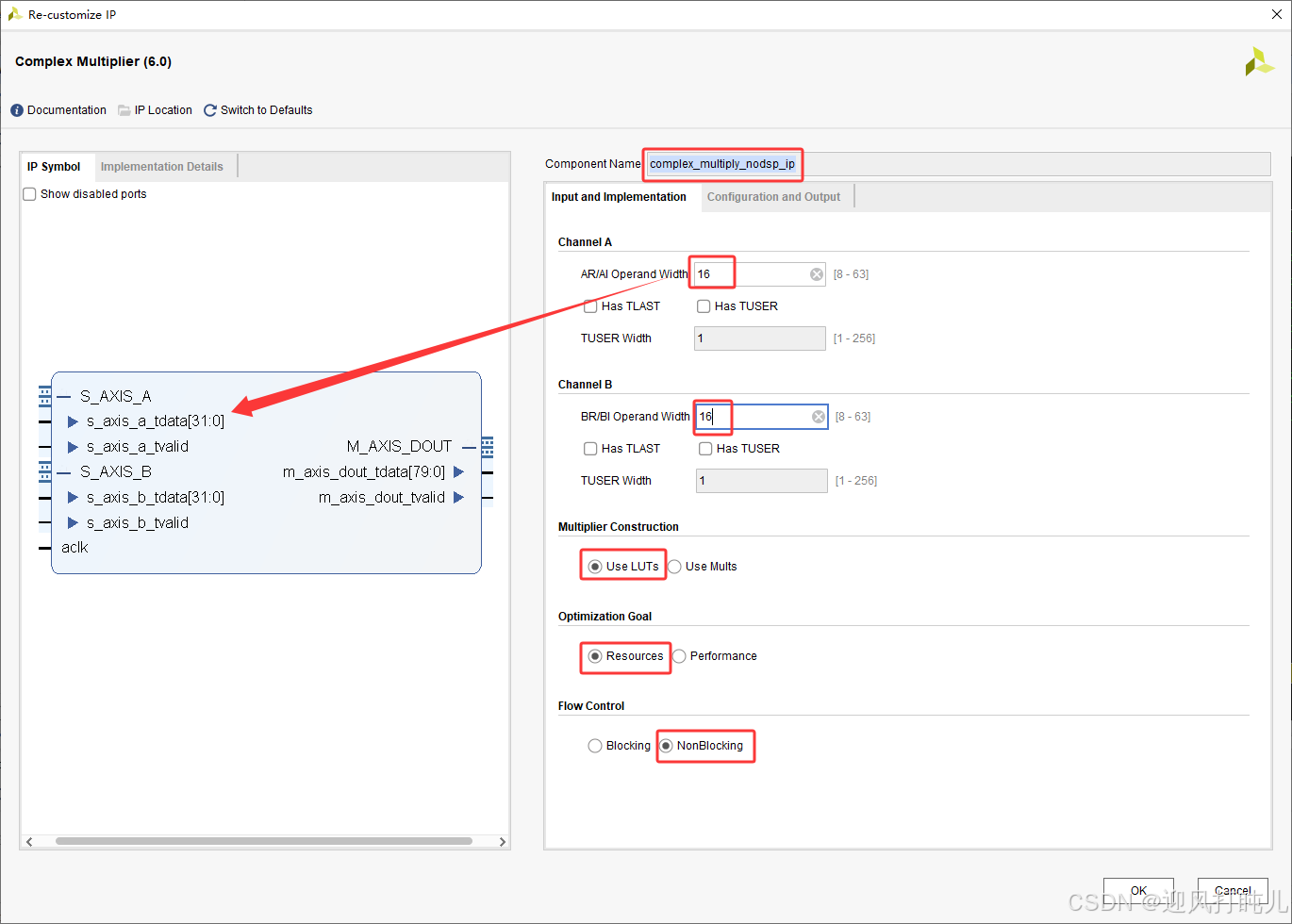

首先配置Input and Implementation界面:

配置变量A实部和虚部的位宽为16位,变量B实部和虚部的位宽为16位,变量s_axis_a_tdata有32位,其中高16位为虚部,低16位为实部;

use luts仅消耗逻辑资源,use mults消耗DSP资源;

选择资源优先还是性能优先(性能指IP时钟频率可以跑的更快);

流控制和AXI4总线协议有关,正常情况下默认选非阻塞模式就行,即两个输入数据同一时钟有效才会得到正确的输出结果。

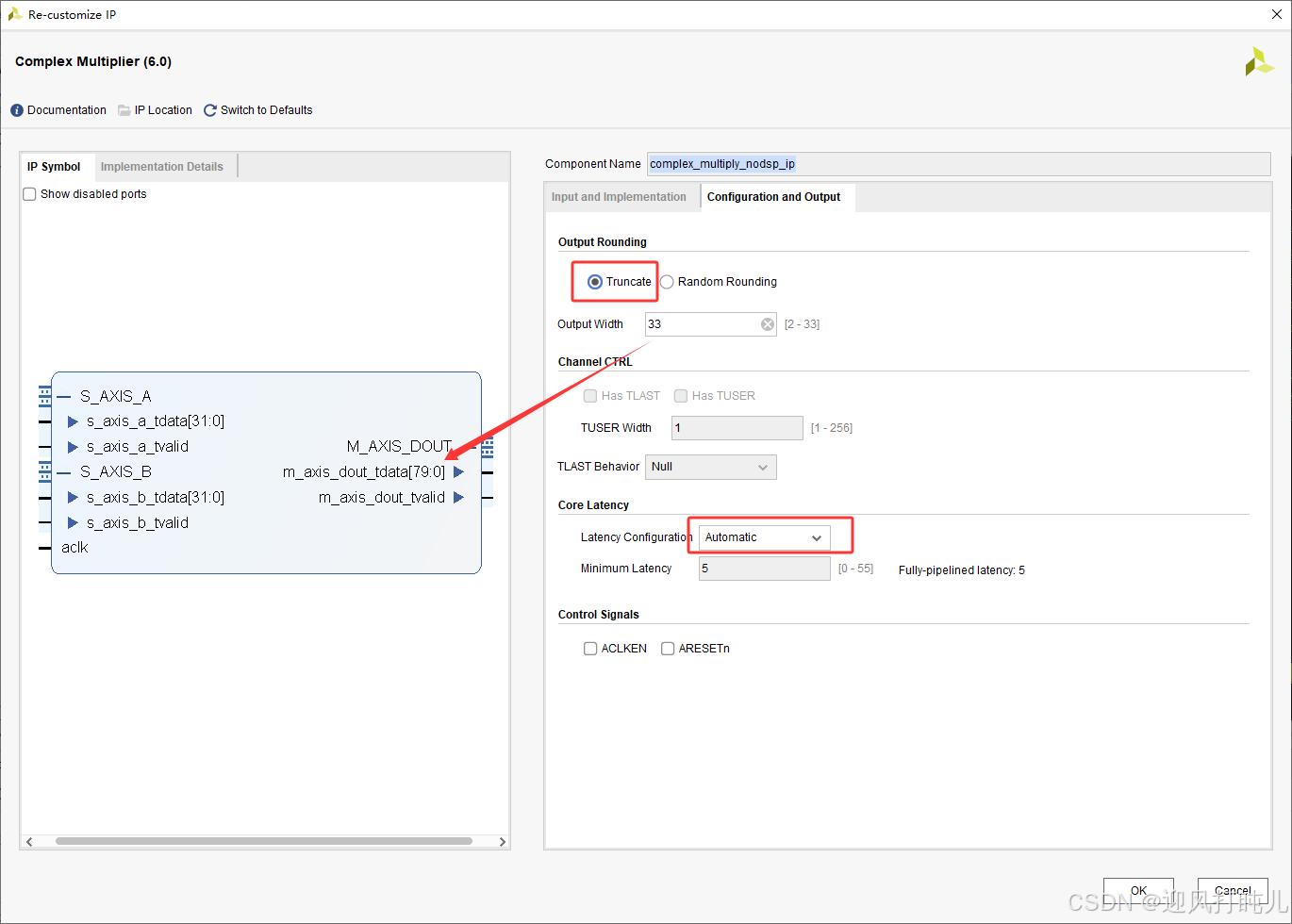

然后配置Configuration and Output界面:

选择截断不会引入新的变量端口;

输出实部和虚部位宽为33位,实际却用了80位,因为该IP核是AXI4协议,要字节对齐。那么输出的高40位为虚部,低40位为实部,另外要注意40位当中低33位为有效数据。

这样设置后资源消耗了1001个LUT,974个FF。

二、仿真

建立一个仿真模块,命名为tb_complex_multiply_nodsp_ip,用来仿真刚才生成的IP核。

代码如下:

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2025/03/13 15:38:00

// Design Name:

// Module Name: tb_complex_multiply_nodsp_ip

// Project Name:

// Target Devices:

// Tool Versions: 2018.3

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module tb_complex_multiply_nodsp_ip();

reg clk=1;

reg din_valid=0;

reg [15 : 0] real_a=0;

reg [15 : 0] imag_a=0;

reg [15 : 0] real_b=0;

reg [15 : 0] imag_b=0;

wire dout_valid;

wire [79 : 0] m_axis_dout_tdata;

wire [32 : 0] dout_real;

wire [32 : 0] dout_imag;

assign dout_imag=m_axis_dout_tdata[72:40];

assign dout_real=m_axis_dout_tdata[32:0];

initial

begin

forever #(1) clk=~clk;

end

initial

begin

#4 din_valid<=1;real_a=1;imag_a=2;real_b=16'hFFFF;imag_b=16'hFFFE; //1+2j -1-2j

#2 din_valid<=1;real_a=1;imag_a=2;real_b=16'h3FFF;imag_b=16'hC001; //1+2j 16383-16383j

#2 din_valid<=0;real_a=0;imag_a=0;real_b=0;imag_b=0;

#(20)

$finish;

end

complex_multiply_nodsp_ip u_complex_multiply_nodsp_ip (

.aclk(clk), // input wire aclk

.s_axis_a_tvalid(din_valid), // input wire s_axis_a_tvalid

.s_axis_a_tdata({imag_a,real_a}), // input wire [31 : 0] s_axis_a_tdata

.s_axis_b_tvalid(din_valid), // input wire s_axis_b_tvalid

.s_axis_b_tdata({imag_b,real_b}), // input wire [31 : 0] s_axis_b_tdata

.m_axis_dout_tvalid(dout_valid), // output wire m_axis_dout_tvalid

.m_axis_dout_tdata(m_axis_dout_tdata) // output wire [79 : 0] m_axis_dout_tdata

);

endmodule

三、仿真分析

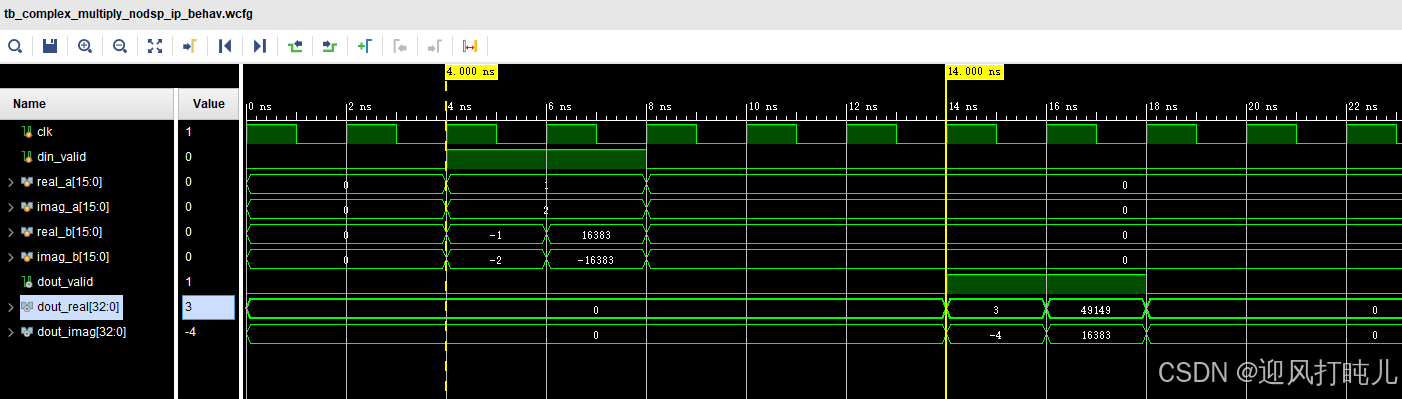

以下图片是testbench的仿真结果:

可见仿真结果输出相对于输入延迟了5个CLK,且结果与MATLAB对的上,成功验证了该IP核的使用。

总结

以上就是今天要讲的内容,本文介绍了 Complex Multiplier 该IP核的使用方法,介绍的配置选项,并编写verilog代码测试了该IP核的复数乘法功能。

1222

1222

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?