本实验利用Aurora的drp接口对CPLL参数进行修改,实现线速率的动态修改。(详情参考UG476)

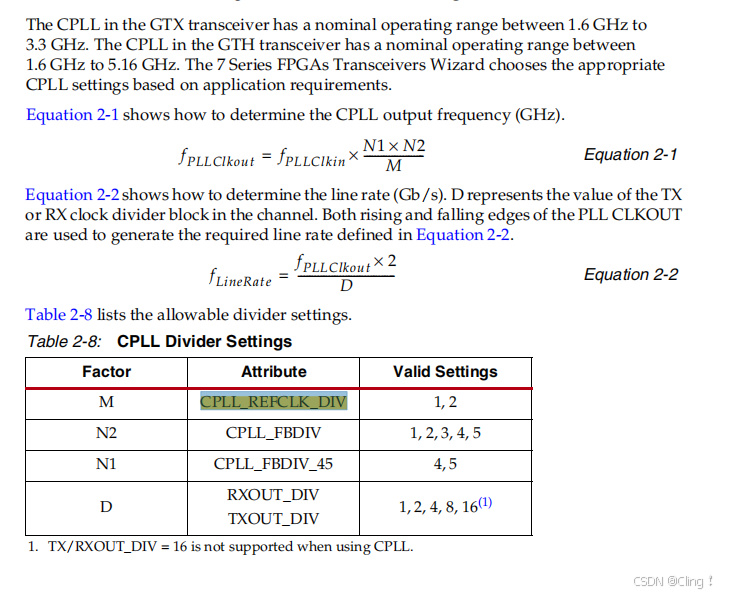

线速率修改公式如下图所示,图中Fpllclkin为IP 的GT参考时钟(实验中为125Mhz):

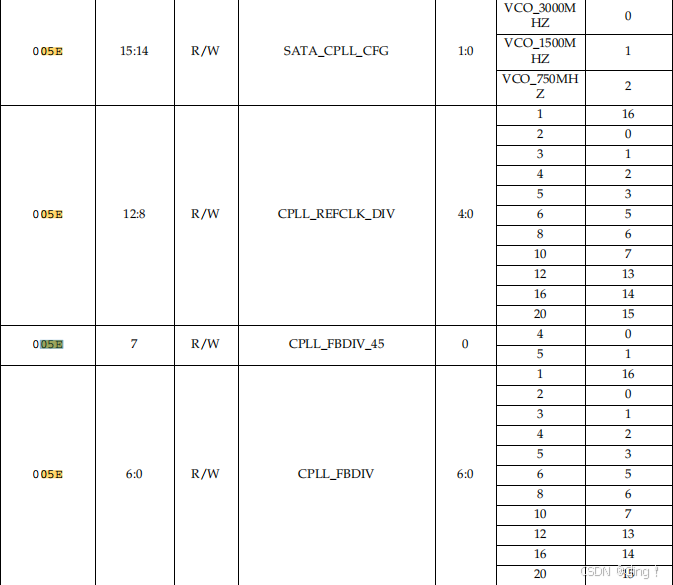

寄存器地址映射如下图:

仿真测试如下:

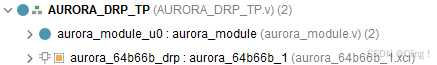

用一个确定速率的IP(aurora_64b66b_drp)去测试需要动态修改速率的模块。这里aurora_64b66b_drp的线速率设为1.25Gbps,被测试的IP初始线速率为6.25Gbps。

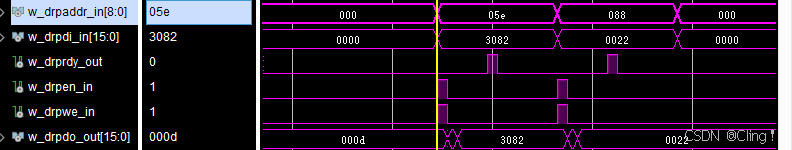

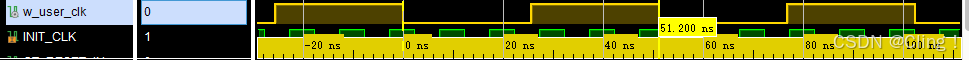

DRP接口时序如图所示:

上图为6.25Gbps----> 1.25Gbps, 注意在操作DRP接口后对被测IP进行整体复位。

w_user_clk为IP输出的用户时钟,可以看到修改线速率之前的周期为10.240ns,修改之后为51.200ns。并且channel_up、lane_up拉高证明双方LINK成功。

461

461

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?