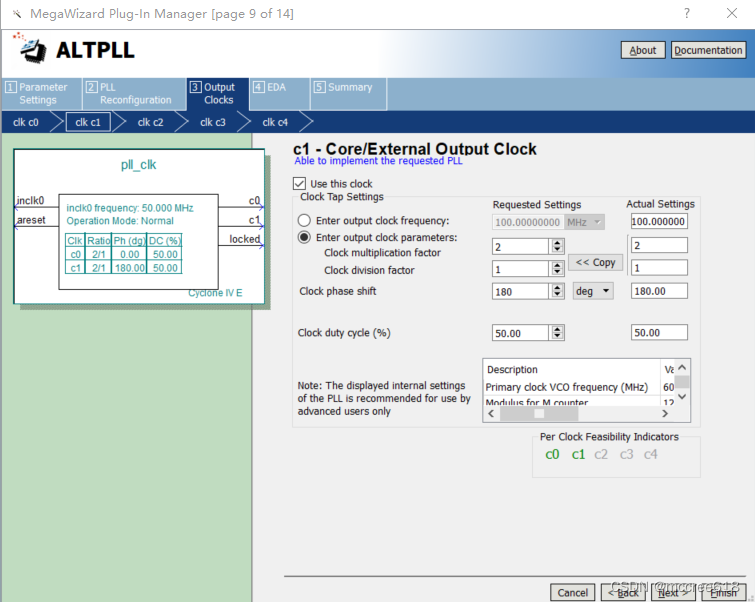

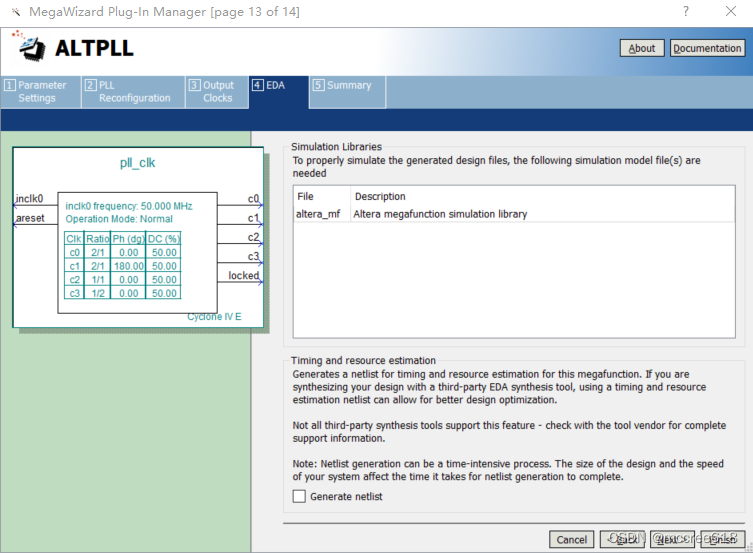

一、创建PLL IP核

Tools — MegaWizard Plug-In Manager — 于如下页面进行相关设置

ps: 若进行仿真,需添加altera_mf模块

二、顶层模块编写

module pll_ip(

input sys_clk,

input sys_rst,

output clk_100m,

output clk_100m_180d,

output clk_50m,

output clk_25m

);

wire locked_sig;

wire rst_n;

assign rst_n = sys_rst & locked_sig; // reset signal for other modules

// pll_clk with high reset

pll_clk pll_clk_inst (

.areset (~ sys_rst ),

.inclk0 ( sys_clk ),

.c0 ( clk_100m ),

.c1 ( clk_100m_180d ),

.c2 ( clk_50m ),

.c3 ( clk_25m ),

.locked ( locked_sig )

);

A. 仿真

三、基于modelsim进行仿真

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

5092

5092

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?