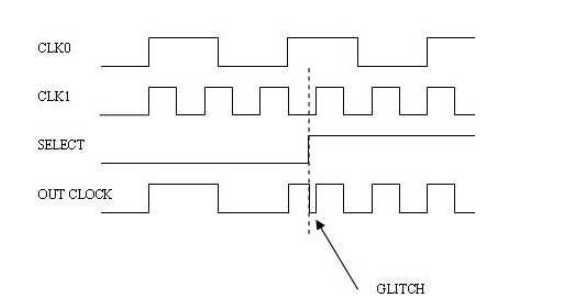

1. 产生毛刺的原因

时钟在另一个时钟为高电平的时候进行切换才会导致毛刺的现象,因此我们需要采用下降沿采样的方式来阻止这种情况

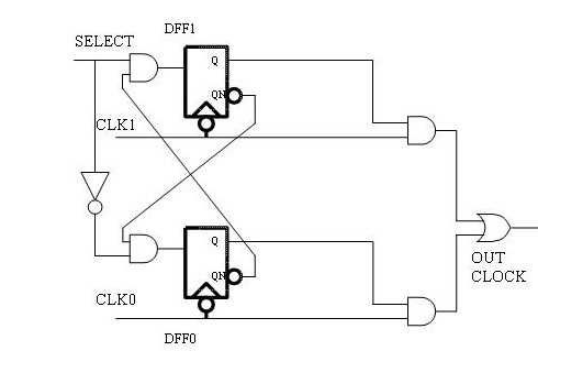

2. 针对两个同步时钟源的切换

通过下降沿触发器进行采样,然后与时钟信号相与,目前没有好的理解方式,只能强记。

reg out1;

reg out0;

always @(negedge clk1 or negedge rst_n)begin

if(rst_n == 1'b0)begin

out1 <= 0;

end

else begin

out1 <= ~out0 & select;

end

end

always @(negedge clk0 or negedge rst_n)begin

if(rst_n == 1'b0)begin

out0 <= 0;

end

else begin

out0 <= ~select & ~out1;

end

end

assign outclk = (out1 & clk1) | (out0 & clk0);

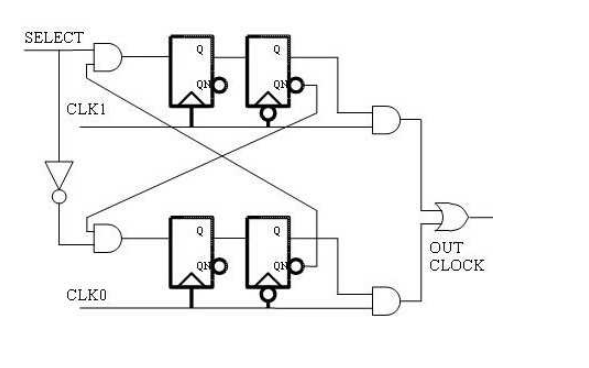

3. 针对两个异步时钟源的切换

先用上升沿采样,然后用下降沿采样

reg out_r1;

reg out1;

reg out_r0;

reg out0;

always @(posedge clk1 or negedge rst_n)begin

if(rst_n == 1'b0)begin

out_r1 <= 0;

end

else begin

out_r1 <= ~out0 & select;

end

end

always @(negedge clk1 or negedge rst_n)begin

if(rst_n == 1'b0)begin

out1 <= 0;

end

else begin

out1 <= out_r1;

end

end

always @(posedge clk0 or negedge rst_n)begin

if(rst_n == 1'b0)begin

out_r0 <= 0;

end

else begin

out_r0 <= ~select & ~out1;

end

end

always @(negedge clk0 or negedge rst_n)begin

if(rst_n == 1'b0)begin

out0 <= 0;

end

else begin

out0 <= out_r0;

end

end

assign outclk = (out1 & clk1) | (out0 & clk0);

参考链接:

https://blog.csdn.net/Reborn_Lee/article/details/101107058

https://zhuanlan.zhihu.com/p/51859467

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?