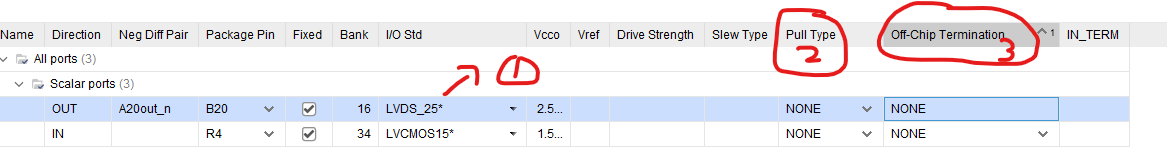

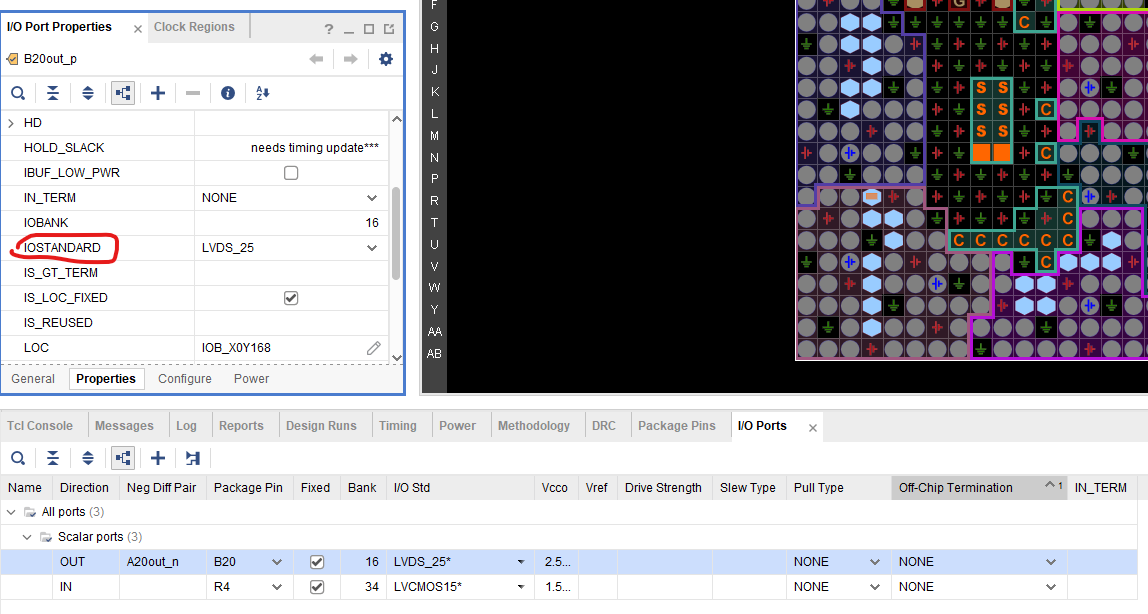

1.有时候在布线这里没有lvds 电平可以选择,这时可以在这个地方约束如下:

2.

2.

PullType设置(当 IO端口设为LVDS的 时候, PullType只能设为 None。)

PullType共有四种选择: PULLUP、PULLDOWN、 NONE、KEEPER。数字电路有三种状态:高电平、低电平和高阻。当 输入为无效 信号的时候 ,可以通过上拉( PULLUP)电阻 和下拉 (PULLDOWN)电阻的方式使其处于稳定状态。

当选择 (KEEPER)时, 使电平保持为上一个有效值。KEEPER 表示启用内部总线保持电路(Bus-Keeper)。当引脚未被主动驱动(处于高阻态或悬空状态)时,该电路会自动将引脚电平保持在最近一次驱动的逻辑电平(0 或 1),防止信号因悬空而波动或引入噪声。

NONE 表示不启用任何内部保持电路、上拉(PULLUP)或下拉(PULLDOWN)电阻。引脚在未被驱动时会处于高阻态(悬空),电平可能受外部电路或噪声影响。

3.

off-chip terminatio设置

这个是设置片外端接电阻和片内端接电阻。采用片上内置的端接电阻可以节省和缩小PCB面积

1771

1771

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?