目录

一、同步电路

定义:电路中所有受时钟控制的单元,全部由一个统一的时钟控制。

优点:在同步设计中,EDA工具可以保证电路系统的时序收敛,避免电路设计中的竞争冒险。

缺点:时钟树综合需要加入大量延迟单元,使电路面积和功耗大大增加。

二、异步电路

定义:电路数据传输可以在任一时刻发生,没有一个统一的时钟控制。

优点:模块化特点突出,对信号延迟不敏感,没有时钟偏斜问题,低功耗的特性

缺点:设计复杂,缺少相应EDA工具支持

同步电路和异步电路的区别在于电路触发是否与驱动时钟同步,从行为上讲,就是所有电路是否在同一时钟沿下同步地处理数据。(《XilinxFPGA设计权威指南》P86~P91 )

即所说的同一个时钟域或不同时钟域,主要是针对时钟源点来区分的。比如有好几个时钟,都是从一个PLL出来的,那这些时钟的相位和倍数都是可控的,我们认为它们之间是同步时钟。

目前大多大规模ASIC和SOC中,都采用全局异步,局部同步的方法。

三、方案概述

四、亚稳态

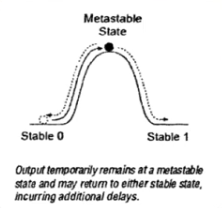

定义:触发器无法在规定时间内达到一个可确认的状态。

无法预测输出的电平,也无法预测何时输出才能稳定。

亚稳态无法从根本上消除,但可以采取一定的措施使其造成的影响降低。

五、快慢转换

2524

2524

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?