提到门延时,就必须重提分布延迟。

分布延迟指模块内信号从(逻辑门的输入到输出)或者(线网的延迟)。这里虽然简短一句话,却涵盖非常大的信息量。

一 门延迟种类

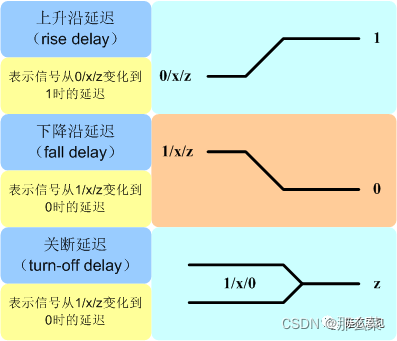

今天我们着重看门延迟。常见门延迟主要有三种:

注意!:如果信号从0/1/z变化到x,那么此时的门传输延迟为上述三种延迟最小的.另外,在进行仿真时,有些逻辑门的输出不可能会出现高阻态z,所以对于这些逻辑门实际上就不存在关断延迟了,类似的逻辑门有:and、nand、or、nor、xor、xnor、buf和not等。

二 门延时格式

其中delay用于指定延迟,如果不指定,则所有延迟的默认值为0.如果指定,主要有两种形式:

- 基本延迟表达式

- 最小值:典型值:最大值"形式

并且这两种形式结合不同的延迟类型经常会混合使用。

2.1 基本延迟表达式

基本延迟一般不指定"最小值:典型值:最大值",可以简单粗暴的认为在简单延迟中,最小值、典型值和最大值可以认为是相同的,常见的简单延迟使用格式如下表示例.

| 延迟类型 | 无延迟 | 1个延迟值(d) | 2个延迟值(d1,d2) | 3个延迟值(d1,d2,d3) |

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

932

932

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?