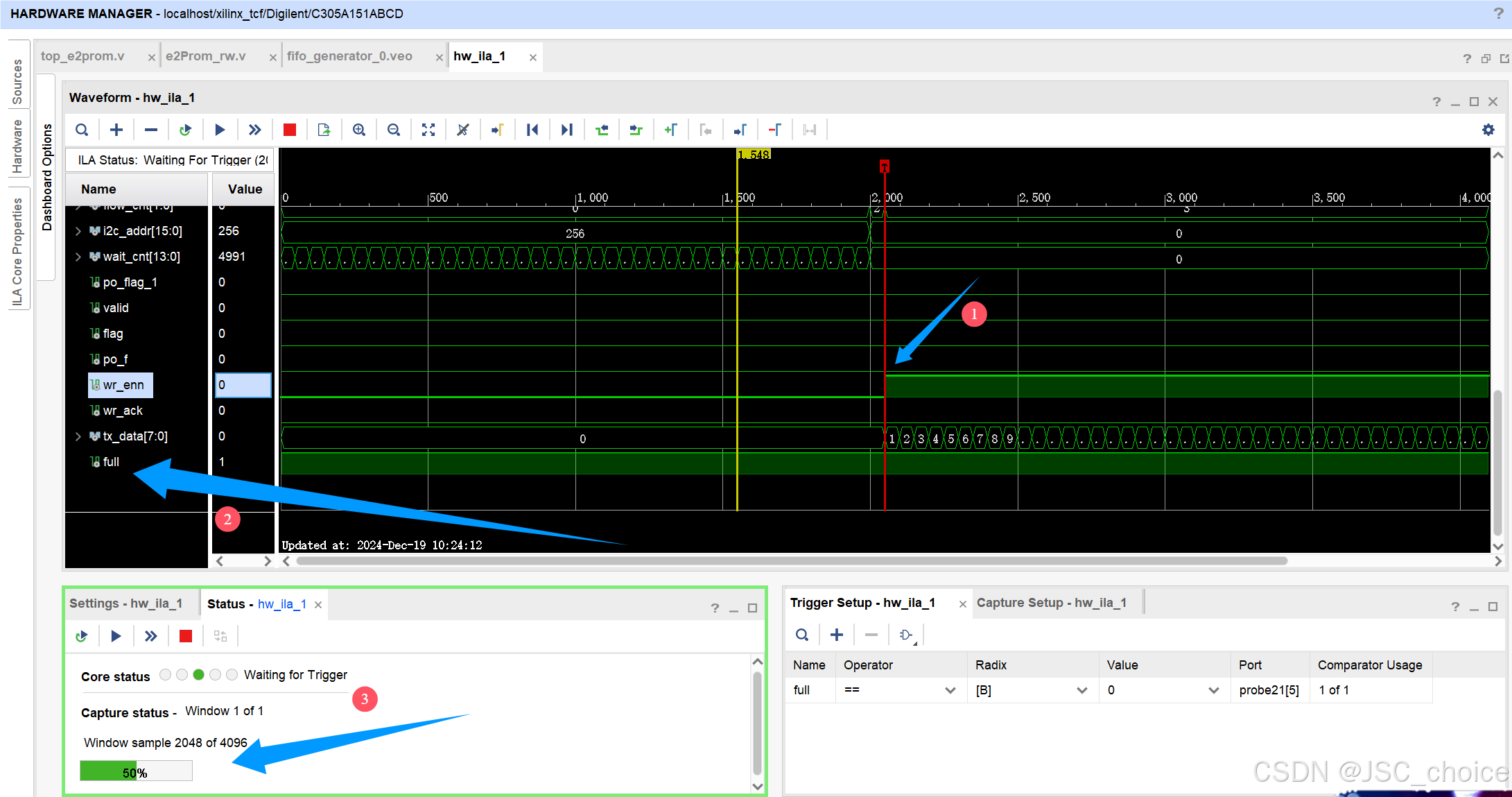

今天使用异步FIFO IP核处理跨时钟域数据,但是遇到full信号一直为高的情况。此时写使能还没有拉高,还没写入数据,full怎么就拉高了。可能是没有使用复位带来的问题。

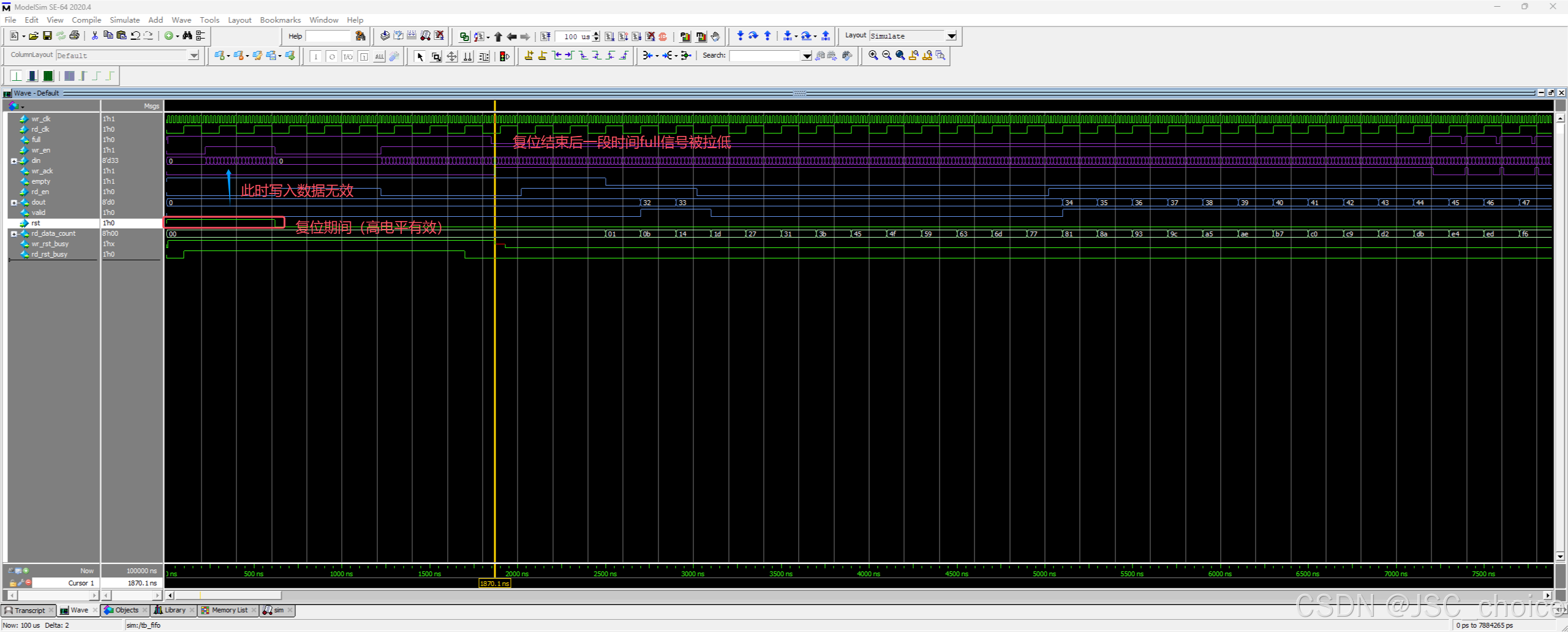

加上复位后进行仿真。

full信号在复位(高电平有效)结束后一段时间后被拉低

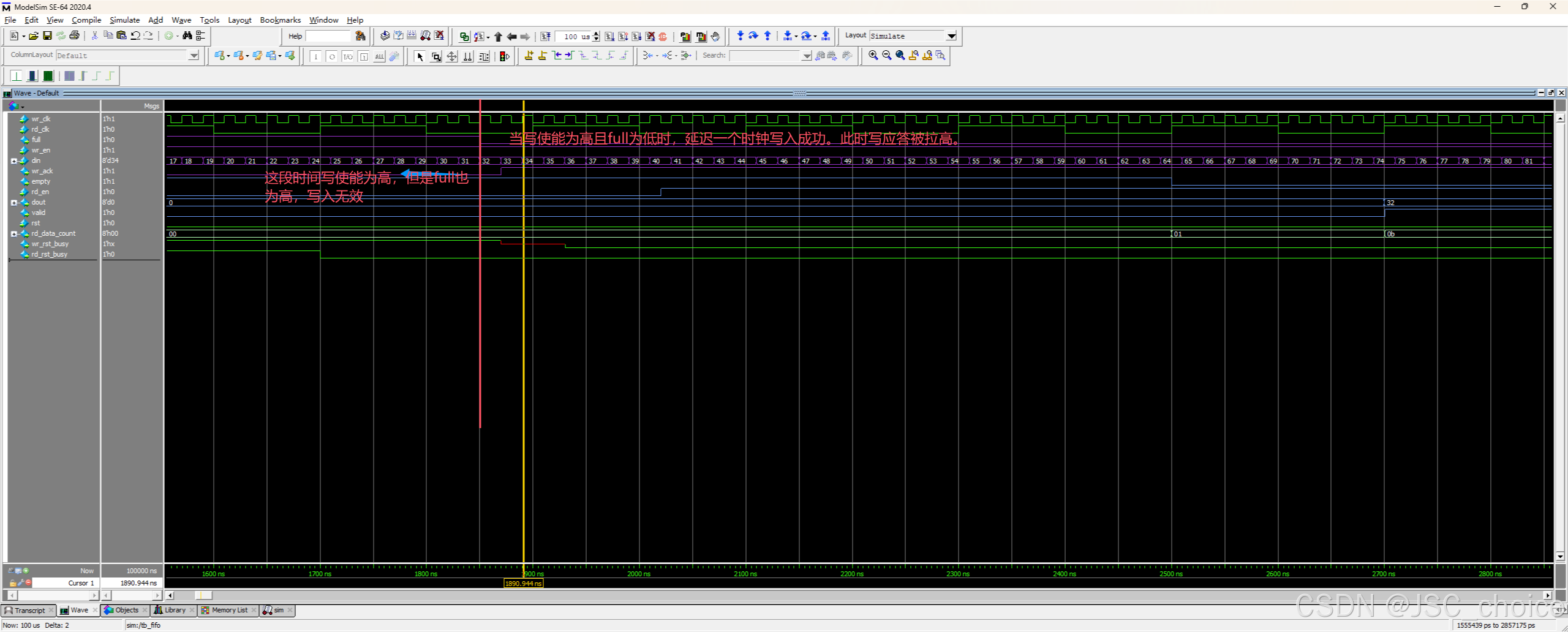

当写使能为高且full为高时,延迟一个时钟写入成功。此时写应答信号被拉高。

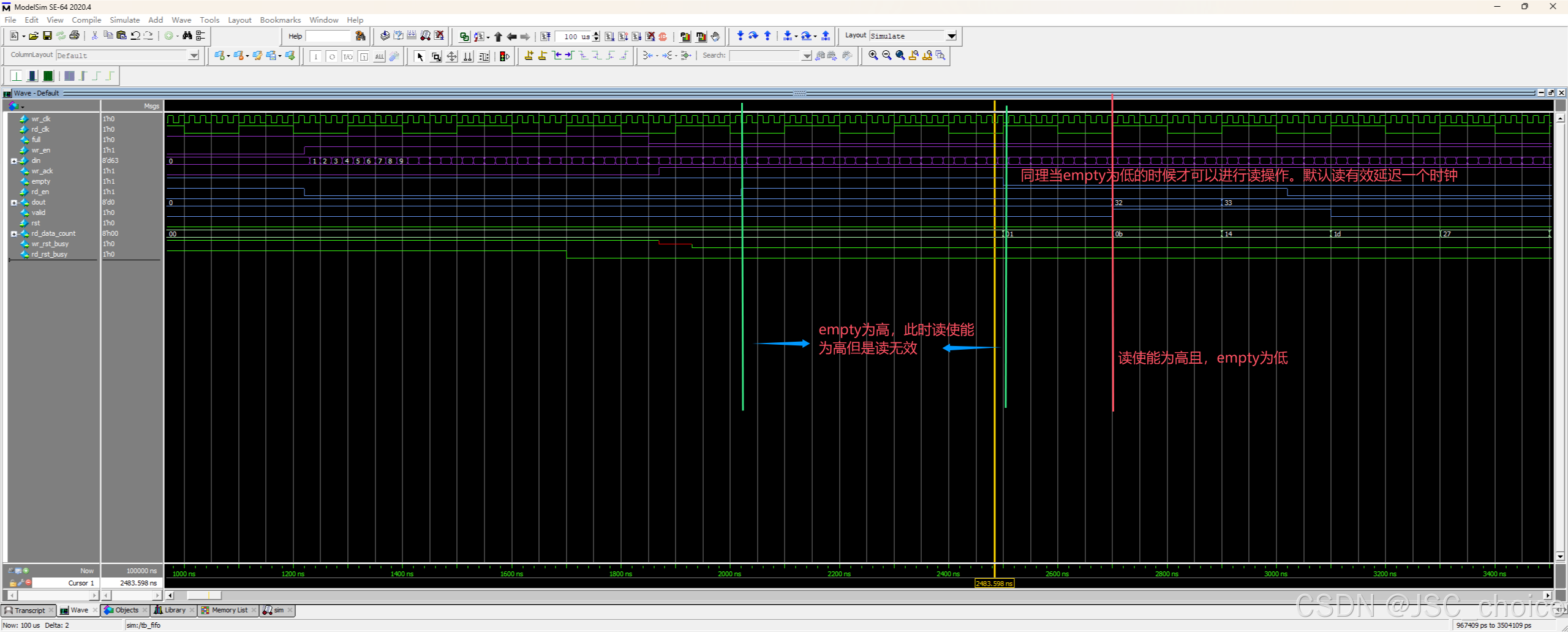

同理当empty为低的时候才可以进行读操作。默认读有效延迟一个时钟

总结:

感觉还是把复位打开比较好。当拉高写使能时要确保full为低(保证有空间写入)。同理empty为低的时候才可以进行读操作。

1158

1158

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?