include和define都是预处理命令,用于常量阐述的定义。

//---------------------------------------

`include file1.v

//--------------

`define X = 1 ;

`define Y

`ifdef Y

Z = 1 ;

`else

Z = 0 ;

`endif有时候我们会定义一些公共的宏参数,将其放在 一个文件 中,比如这个文件命名为 **.v , 那么就可以在其他设计中通过添加 `include **.v 来包含文件中定义的一些宏参数。

Verilog中`include作用与C中的include用法基本一致,区别就在于Verilog中使用时,作为系统任务需要在关键字前加 ` 。

在设计时,将`define 、`ifdef、`else 、 `endif几个关键字联合起来使用,能够使得程序多样化, 比如在VGA驱动设计时,对一些分辨率的参数定义,以及串口设计时对于一些波特率参数的定义等。

一般情况下,Verilog HDL源程序中所有的行都参加编译。但是有时候希望对其中的一部份内容只有在条件满足的时候才进行编译,也就是对一部分内容指定编译的条件,这就是“条件编译”。有时,希望当满足条件时对一组语句进行编译,当条件不满足时则对另外一组语句进行编译。

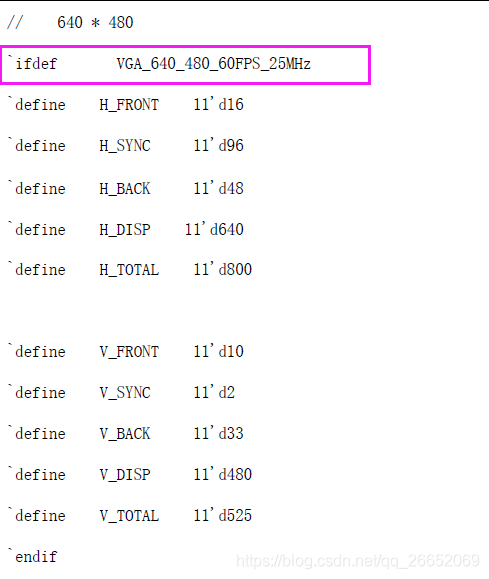

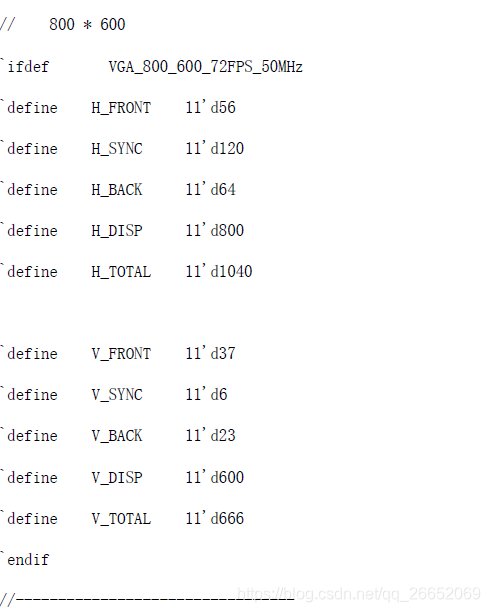

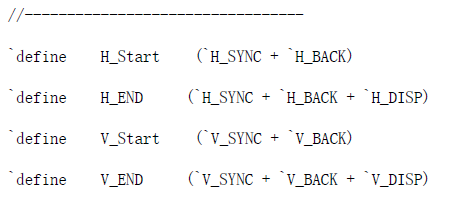

上述都是在lcd_para.h中定义的参数,一共定义了两种分辨率,分别通过VGA_640_480_60FPS_25MHz或`define VGA_800_600_72FPS_50MHz来决定用哪种分辨率。

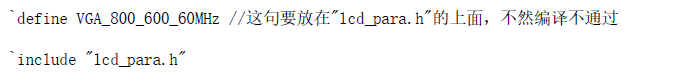

当设计文件想调用lcd.para.h时,在设计文件中需要作如下操作:

需要注意的是,`include "lcd_para.h"路径有一点讲究,上述设计文件作为引用lcd_para.h的文件,它必须和lcd_para.h在同一文件夹下,因为这样写是以设计文件的当前路径去索引lcd_para.h的位置。 如果二者不在同一文件夹下,那么必须要写出更详细,更准确的路径。lcd_para.h添不添加到工程无所谓的,只要路径对了即可。

条件编译命令的几种形式:

即`ifdef、`else 、 `endif的联合使用。

(1)

`ifdef宏名(标识符)

程序段1

`else

程序段2

`endif它的作用是当宏名已经被定义过(此处需要采用`define命令定义),则对程序段1进行编译,程序段2将被忽略;否则编译程序段2,程序段1将被忽落。

其中`else部分可以没有,即:

(2)

`ifdef宏名(标识符)

程序段1

`endif这里的“宏名”是一个Verilog HDL 的标识符,“程序段”可以是Verilog HDL语句组,也可以是命令行。这些命令可以出现在源程序的任何地方。

【注意】:被忽略掉不进行编译的程序段部分也要符合Verilog HDL程序的语言规则。

通常在Verilog HDL程序中用到`ifdef、`else、`endif编译命令的情况有以下几种:

(1)选择一个模板的不同代表部分。

(2)选择不同的时序或结构信息。

(3)对不同的EDA工具,选择不同的激励。

最常用的情况是:Verilog HDL代码中的一部分可能适用于某个编译环境,但不适用于另一个环境,如果设计者不想为两个环境创建两个不同版本的Verilog 设计,还有一种方法就是所谓的条件编译,即设计者在代码中指定其中某一部分只有在设置了特定的标志后,这一段代码才能被编译,即设计者在代码中指定其中某一部分只有在设置了特定的标识后,这一段代码才能编译。

设计者也可能希望在程序的运行中,只有当设置了某个标志后,才能执行Verilog 设计的某些部分,这就是所谓的条件执行。

条件编译可以用编译指令`ifdef、`else、`elsif和`endif实现。

`ifdef和`ifndef指令可以出现在设计的任何地方。设计者可以有条件地编译 语句、模块、语句块、声明和其他编译指令。`else指令是可选的。一个`else指令最多可以匹配一个`ifdef或者`ifndef。一个`ifdef或者`ifndef可以匹配任意数量的`elsif命令。`ifdef或`ifndef总是用相应的`endif来结束。

Verilog文件中,条件编译标志可以用`define语句设置。如果没有设置条件编译标志,那么Verilog编译器会简单地跳过该部分。`ifdef语句中不允许使用布尔表带式,例如使用TEST && ADD_B2来表示编译条件是不允许的。

590

590

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?