目录

2.1 DDR5 SDRAM X4, X8的行

- DDR5 SDRAM x4/x8底部组件有13个电气行的焊球,包含信号、电源和地三种焊球。

- 除了电气行外,还有额外的非电气行,非电气行的焊球不用于电气连接,而是为了提供机械支撑。

2.2 DDR5 SDRAM球距

- DDR5 SDRAM 组件焊球的中心间距大小0.8mm*0.8mm,另外被缩减了3列未布线。

2.3 DDR5 SDRAM X4, X8的列

- DDR5 SDRAM x4/x8组件有6个电气列,分为2组,每组3列。在电气列之间有3个没有焊球的列。

- 留空未布线的列用于提供电气隔离、热管理或机械稳定性。

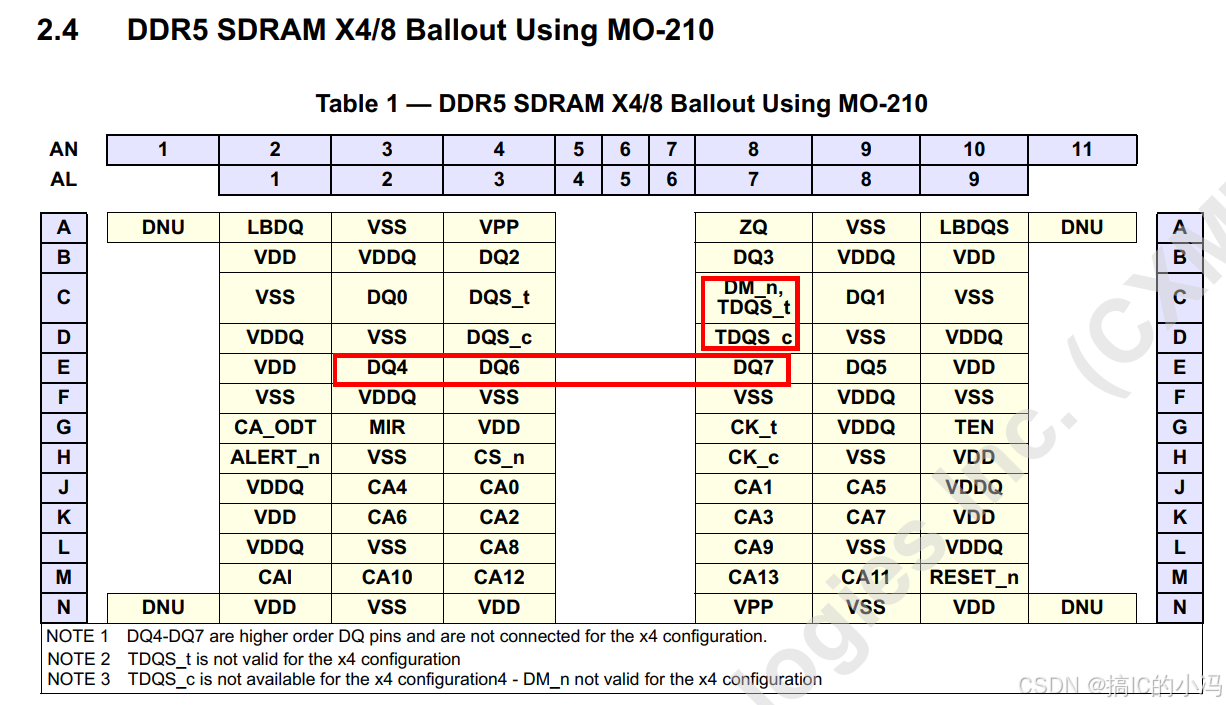

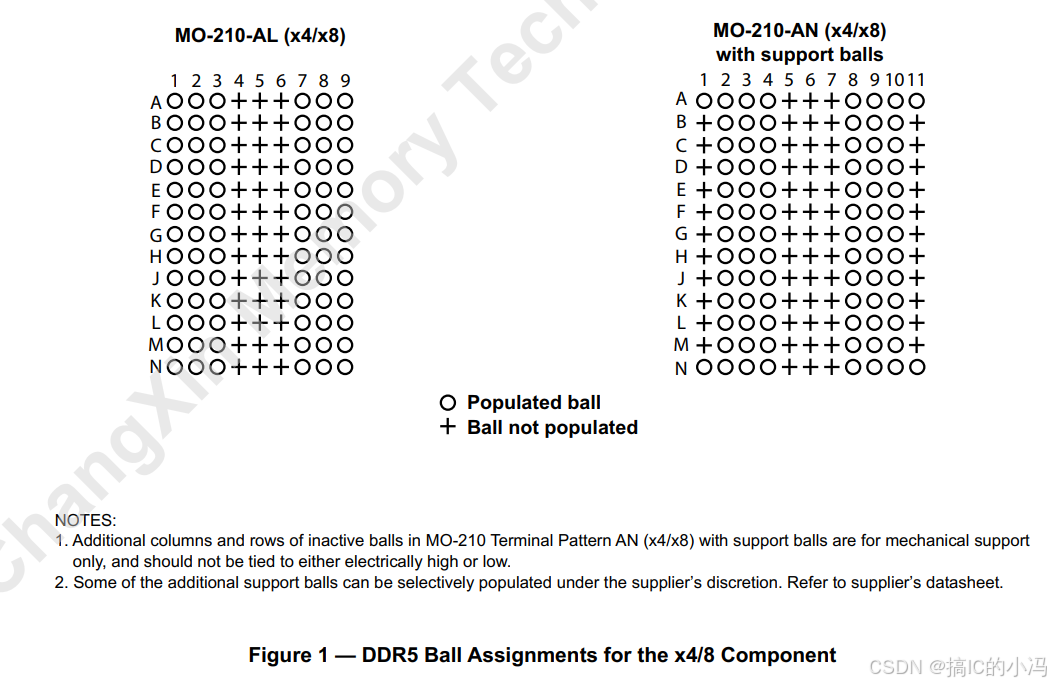

2.4 采用MO-210方式封装的DDR5 SDRAM X4/8引脚排布

- 红框中部分不支持x4配置

- 13行 2*3列

- AN和AL是两种不同的封装类型

MO-210是啥?

- 是JEDEC规定的一种封装形式。

- 完整英文电子版 JEDEC MO-210Q(PBGA-B#) :2021 Plastic Bottom Grid Array, 0.80 MM Pitch,

Rectangular Family Package( 塑料底部网格阵列,0.80 MM 间距,矩形系列封装)。

外形及尺寸标注的图纸。

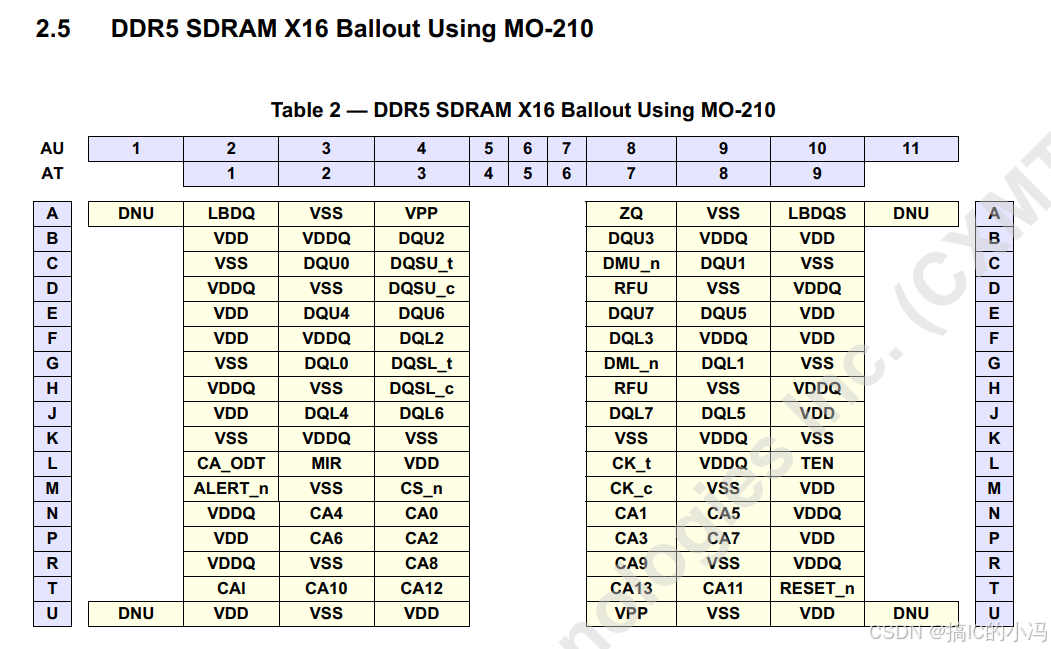

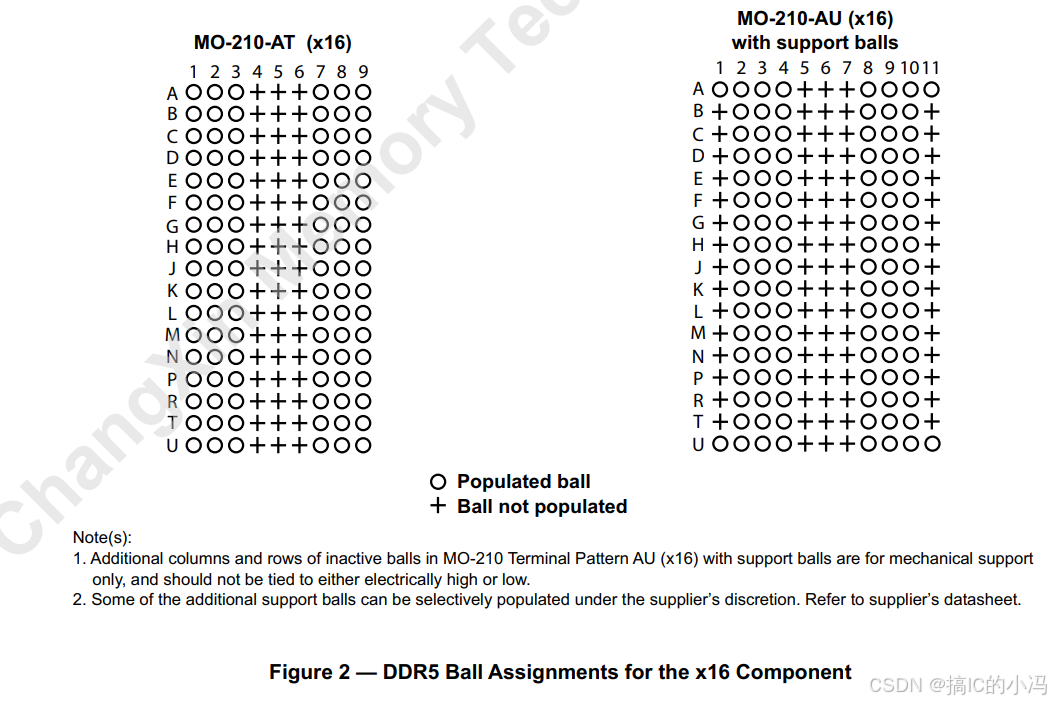

2.5 采用MO-210方式封装的DDR5 SDRAM X16引脚排布

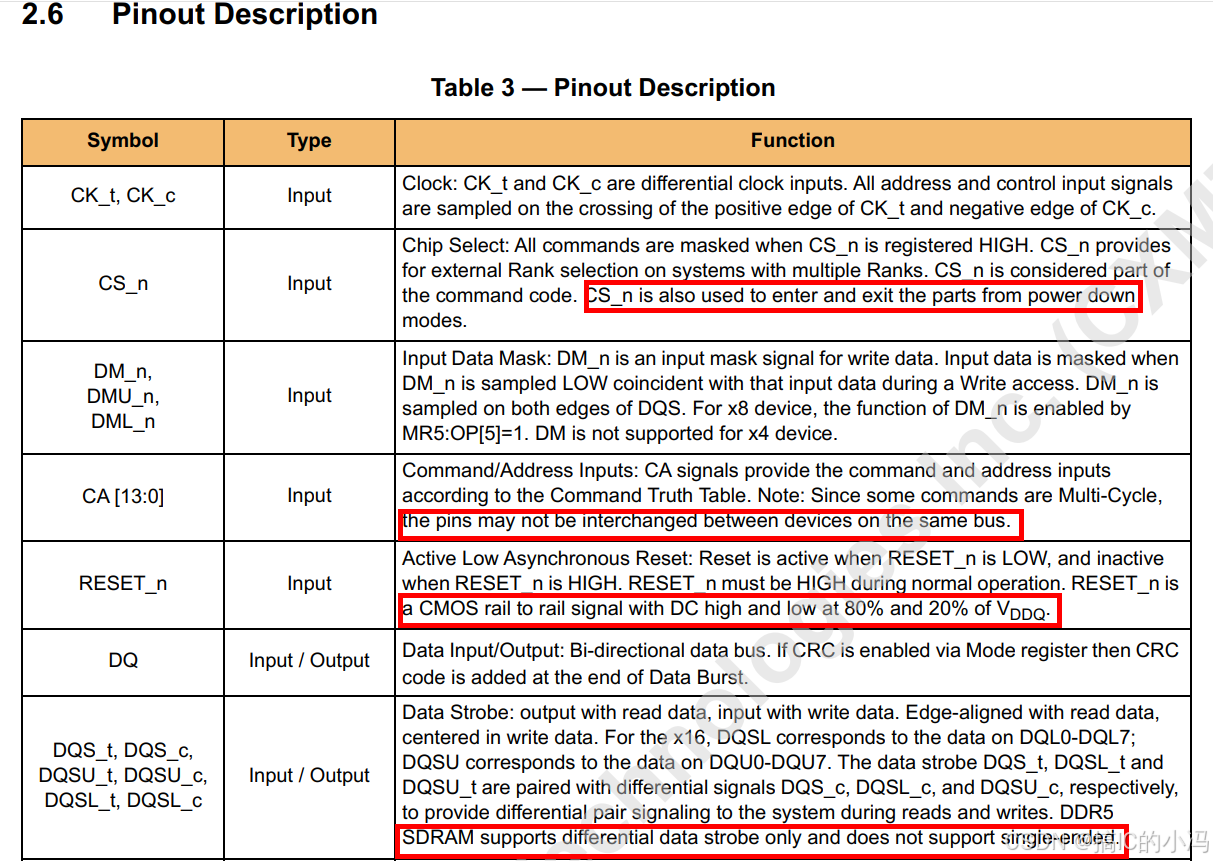

★2.6 引脚描述

分为配置引脚、控制引脚、电源引脚、时钟引脚、地址引脚和数据引脚

-

差分时钟: CK_t和CK_c是差分时钟输入。所有地址和控制输入信号在CK_t的正沿和CK_c的负沿交叉处进行采样。

-

芯片选择(Chip Select):当CS_n被设置为高电平时,所有命令都会被屏蔽。在具有多个rank的系统中,

CS_n用于外部rank选择。CS_n被视为命令代码的一部分。CS_n还用于低功耗模式进入和退出。 -

输入数据掩码(Input Data Mask):DM_n是用于写入数据的输入屏蔽信号。在写入访问期间,

当DM_n与相应的输入数据在低电平上同时采样时,输入数据会被屏蔽。DM_n在DQS的两个边沿上进行采样。

对于x8设备,通过MR5:OP[5]=1启用DM_n的功能。x4设备不支持DM。 -

★命令/地址引脚(CA):CA信号根据命令真值表提供命令和地址输入。注意:由于某些命令是多周期的,

因此在同一总线上的设备之间可能不能交换引脚。 -

低有效电平异步复位(Active Low Asynchronous Reset):

- 当RESET_n为低电平时,复位是激活状态;

- 当RESET_n为高电平时,复位是非激活状态。在正常操作期间,RESET_n必须为高电平。

RESET_n是一个CMOS电平信号,其高电平和低电平分别为VDDQ的80%和20%。

-

数据输入/输出(DQ): 双向数据总线。如果通过模式寄存器启用了CRC,则CRC码将添加到数据突发的末尾。DRAM 根据其 DQ 数据总线宽度,划分为 x4、x8 以及 x16 三类

-

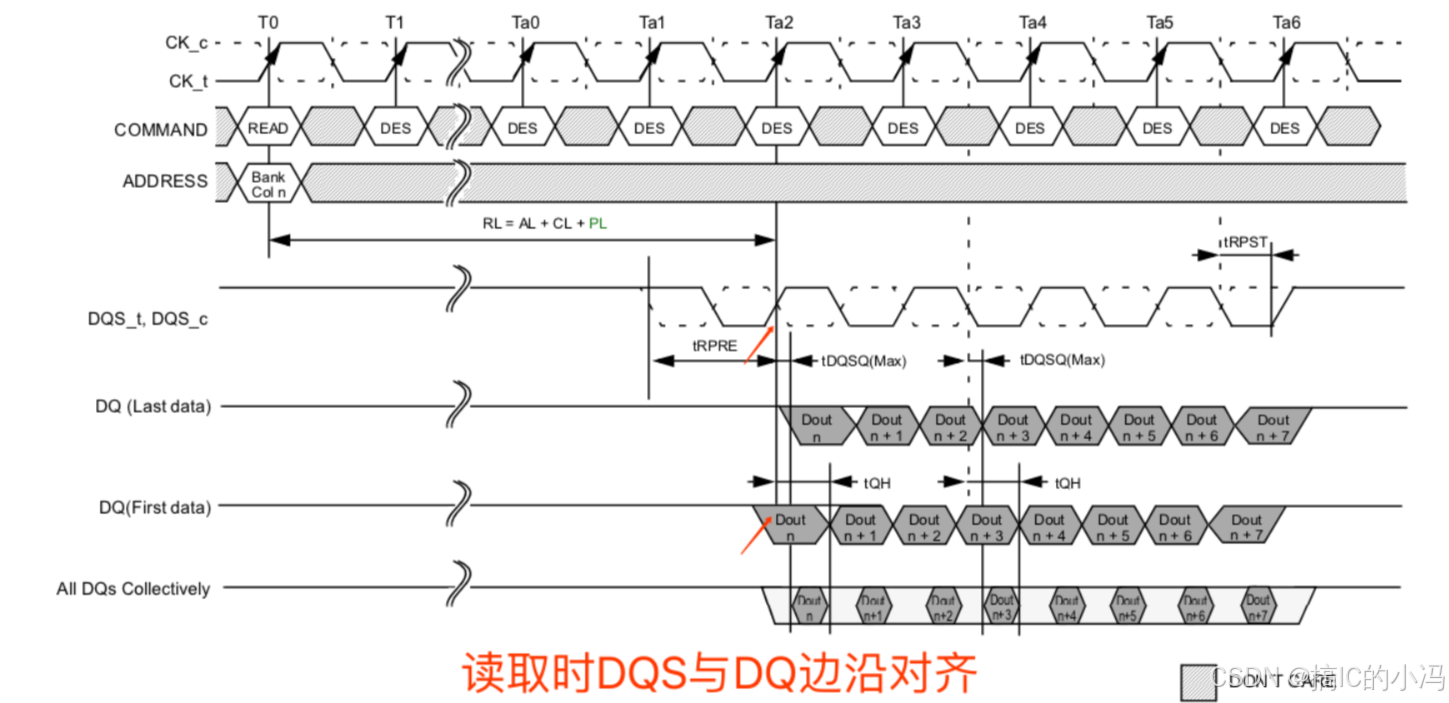

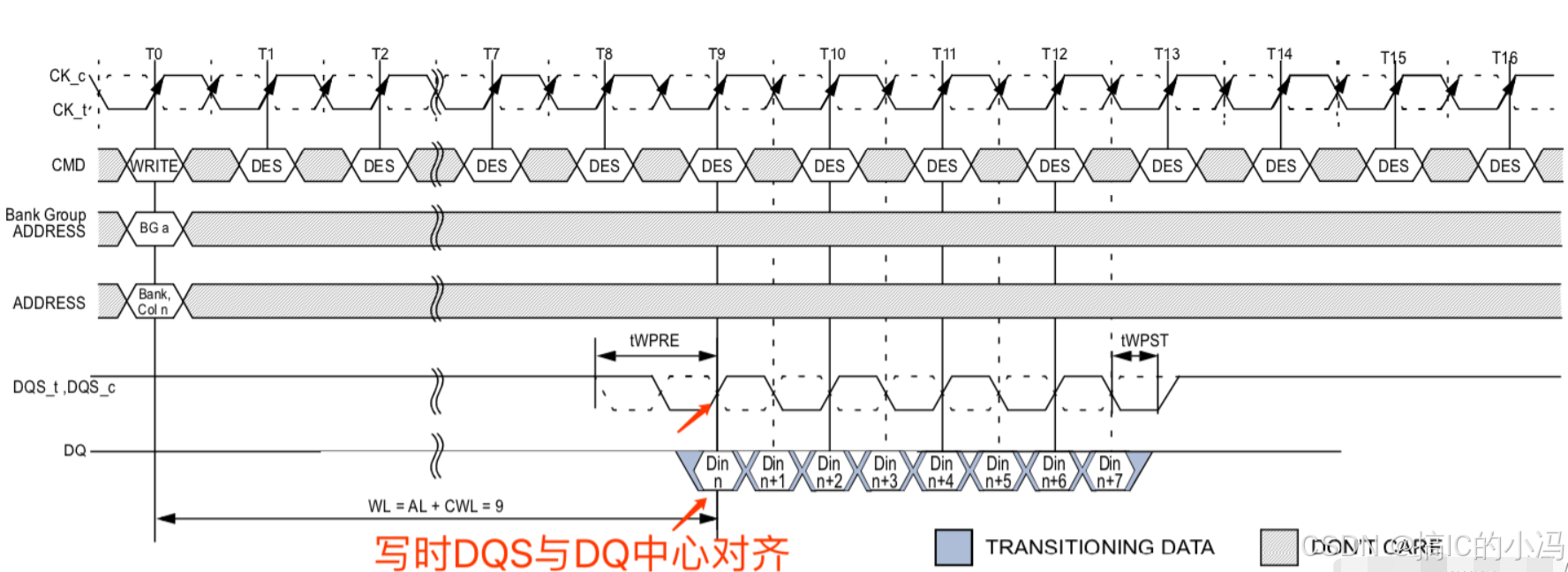

数据引脚:DQS

为什么引入DQS?

DQS主要用来在一个时钟周期内准确的区分出每个传输周期,并便于接收方准确接收数据。完全可以说,DQS就是数据的同步信号。

- DQ数据是通过DQS来采样的,且DQS是双向信号,可以通过DQS的传输信号来判断是信号开始还是结束。此外,也可以通过DQS与DQ的相位关系来判断传输信号是Read或Write信号。

- 从内存读数据时,将DQS边沿与DQ边沿对齐。

- 向内存写数据时,将DQS边沿与DQ中心对齐。

- 对于x16位的数据,DQSL对应于DQL0-DQL7上的数据;

- DQSU对应于DQU0-DQU7上的数据。数据时钟脉冲DQS_t、DQSL_t和DQSU_t分别与差分信号DQS_c、DQSL_c和DQSU_c配对,以在读取和写入过程中向系统提供差分对信号。

- DDR5 SDRAM仅支持差分数据时钟脉冲,不支持单端信号。

- DQ数据是通过DQS来采样的,且DQS是双向信号,可以通过DQS的传输信号来判断是信号开始还是结束。此外,也可以通过DQS与DQ的相位关系来判断传输信号是Read或Write信号。

-

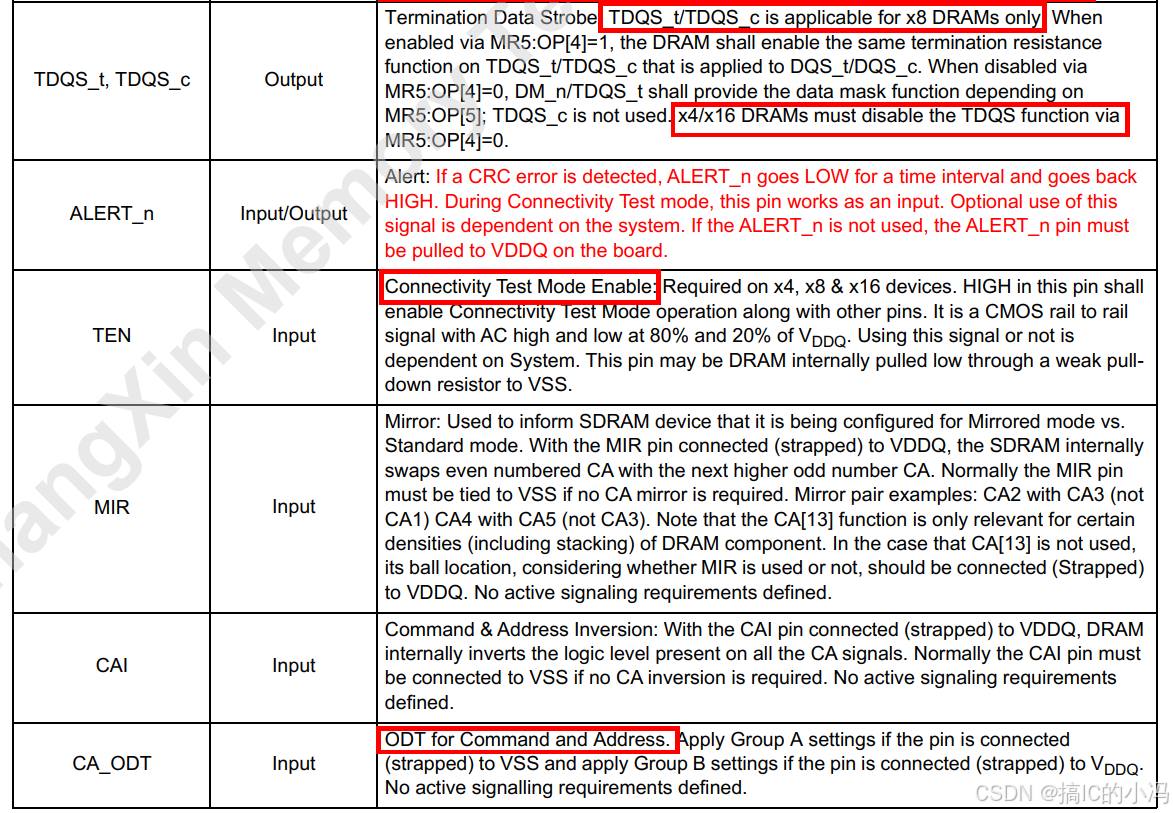

终端数据时钟脉冲(Termination Data Strobe):TDQS_t/TDQS_c仅适用于x8位的DRAM。

- 当通过MR5:OP[4]=1启用时,DRAM将在TDQS_t/TDQS_c上启用与DQS_t/DQS_c相同的终端电阻功能。

- 当通过MR5:OP[4]=0禁用时,DM_n/TDQS_t将根据MR5:OP[5]提供数据屏蔽功能;TDQS_c不使用。

- x4/x16位的DRAM必须通过MR5:OP[4]=0禁用TDQS功能。

-

警报信号(ALERT_n):如果CRC或者奇偶校验中存在错误,则ALERT_n引脚在一段时间内变为低电平,然后恢复为高电平。

- 在连通性测试模式下,此引脚作为输入使用。是否使用此信号取决于系统。

- 如果未连接为信号,则必须将ALERT_n引脚与电路板上的VDDQ连接。

-

连通性测试模式使能信号(TEN):对于x4、x8和x16设备是必需的。当此引脚为高电平时,将启用连通性测试模式操作。

以及其他引脚。它是一个CMOS的全摆幅信号,交流高电平和低电平分别为VDDQ的80%和20%。

是否使用此信号取决于系统。此引脚可以通过弱拉低电阻器将DRAM内部拉低到VSS。 -

镜像(Mirror): 模式切换。用于实现命令地址引脚的互换,方便布局布线。通过通知SDRAM设备,其正在配置为镜像模式还是标准模式。

- 当MIR引脚连接到VDDQ时,SDRAM内部会将偶数编号的CA与下一个更高的奇数编号的CA进行交换。通常,如果不需要CA镜像,则MIR引脚必须连接到VSSQ。

- 镜像对应示例:CA2与CA3(不是CA1),CA4与CA5(不是CA3)。

请注意,CA[13]功能仅适用于特定密度(包括堆叠)的DRAM组件。 - 如果不使用CA[13],考虑是否使用MIR的情况下,其焊球位置应连接到VDDQ。

-

命令和地址翻转信号(CAI):用于优化信号传输的电流消耗。

- 当CAI引脚连接到VDDQ时,DRAM内部翻转所有CA信号上的逻辑电平。

- 通常,如果不需要CA翻转,则CAI引脚必须连接到VSSQ。

-

命令和地址的ODT(CA_ODT):控制内存的ODT(On-Die Termination)

- 如果该引脚连接到VSS,则应用A组设置;

- 如果该引脚连接到VDDQ,则应用B组设置。不懂什么是A组B组

- CA_ODT引脚可以通过高电平激活ODT功能,优化数据传输的稳定性和速度。在读取大量数据时,这能降低信号反射,从而提高数据传输的完整性。

-

回环数据输出(LBDQ):该设备的输出通过MR53:OP[4:0]中定义的回环输出选择(Loopback Output Select)进行。

- 当启用回环时,它处于驱动器模式,并使用回环功能部分描述的默认RON。

- 当禁用回环时,根据MR36:OP[2:0]的设置,该引脚要么终端化,要么处于高阻态(HiZ)。

-

回环数据触发器(LBDQS): 这是一个单端触发器,其上升沿与回环数据边缘对齐,下降沿与数据中心对齐。

- 当启用回环时,它以驱动器模式工作,并使用回环功能部分描述的默认RON。

- 当禁用回环时,根据MR36:OP[2:0]的设置,该引脚要么终端化,要么处于高阻态(HiZ)。

在芯片的测试模式下,LBDQ将输出接收到的数据信号状态,而LBDQS则输出对应的DQS信号状态。这可以帮助工程师验证信号的完整性和时序,确保内存正常工作。

-

保留信号(RFU)

-

未使用信号(NC)

-

DQ信号电源(VDDQ) 主要给I/O提供电源

-

DDR5模块供电电源(VDD)芯片主电源供电

-

内存地(VSS)

-

DRAM激活电源(VPP): 用于激活内存芯片

-

ZQ校准(ZQ) 是ODT的校准参考,接RZQ(阻值240Ω)到地

- 有关ZQ校准,参考下面这个博客

还有两个信号,表中没有。

- VREFCA: CA信号的参考电平

- VSSQ: DQ信号参考Ground

什么是mirrored mode?

-

在DDR4阶段是通过SPD(Serial Presence Detect)里来通知CPU来知道外接的内存进行了mirror,并且没有这么大量的管脚被mirror。

SPD通常是EEPROM,存储各种配置信息。

-

从DDR5开始引入物理管脚来管理,通知DRAM颗粒它的偶数CA和下一个奇数CA进行了swap。

-

要做管脚mirror的原因,个人理解:应当是两rank下fly by结构的时候,为了CA信号能够尽可能地走线方便,减少stub(即线路板布线中的短线段)优化信号质量。

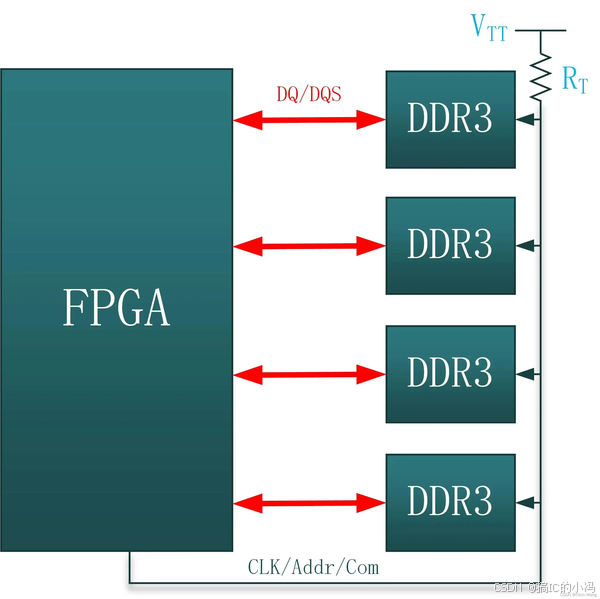

如下图,找到一张DDR3 fly-by的结构图,ddr5类似。

地址、命令和时钟的布线依次经过每一颗DDR3芯片,信号依次到达每个DDR3芯片,有效降低了同步切换噪声。减少了信号线的分支,借助于端接电阻,有效保证了信号的完整新。

因为时钟(CK)和数据选通(DQS)信号到达每一颗DDR3芯片的距离不一样,这就会导致time skew,需要进行Write leveling(写入均衡)。

-

Write leveling

不断增加Write DQS的延时以便满足CK与DQS之间的相位关系。

CAI和CAI_ODT是啥

- CAI

- 让DRAM内部翻转CA信号,在UDIMM和SODIMM上都未使用这个,在DDR4阶段有些设计会使用DMI信号,

- CAI是用来翻转Data Bus上的电平,为了减少功耗,CAI信号应该也是降低功耗的考虑。

- CAI_ODT

- C&A信号的匹配电阻的配置管脚。DDR5开始将CA/CS/CK信号的终端电阻放入DRAM die中,

并将上拉电阻能力分为两类——Group A较弱,Group B较强。 - CA_ODT接到VSS表示Group A,接到VDD则表示Group B。这样的好处是明显的,在应用中不需要再为DRAM添加终端电阻了。一个实例如下,最左边DRAM的CA_ODT接VDD,除此之外的接到VSS。

- C&A信号的匹配电阻的配置管脚。DDR5开始将CA/CS/CK信号的终端电阻放入DRAM die中,

Loopback(环回)功能是啥?

- LBDQ/LBDQS。Loopback功能,将DRAM收到的数据再直接发送出去,不受读写命令的影响,在CA Training和CS Training中会用到,详见4.39

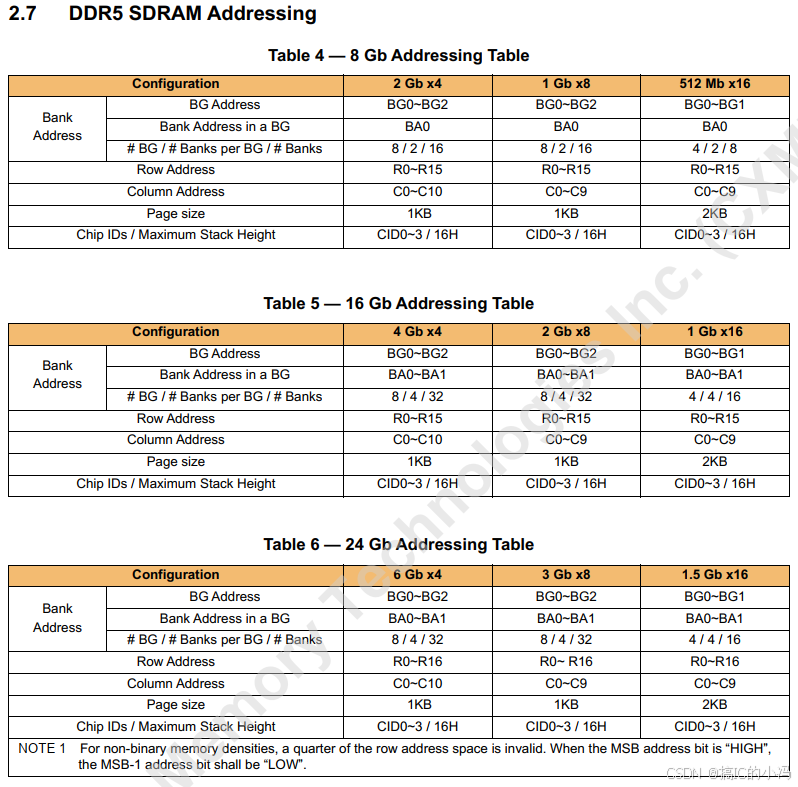

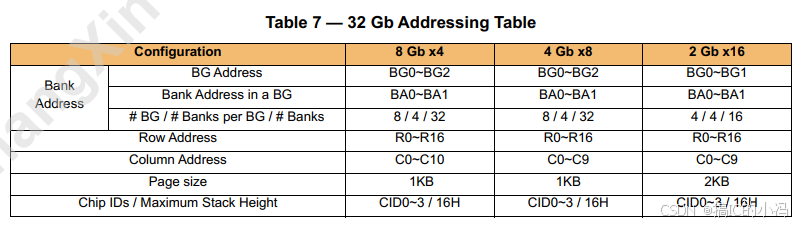

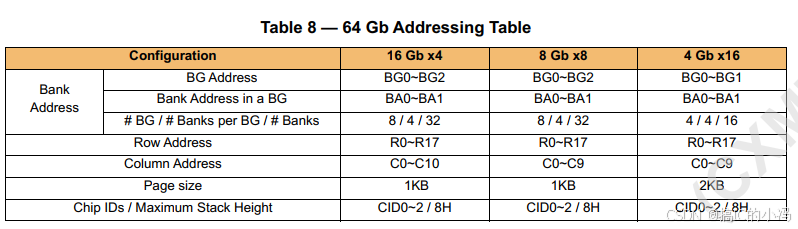

★2.7 DDR5 SDRAM 寻址

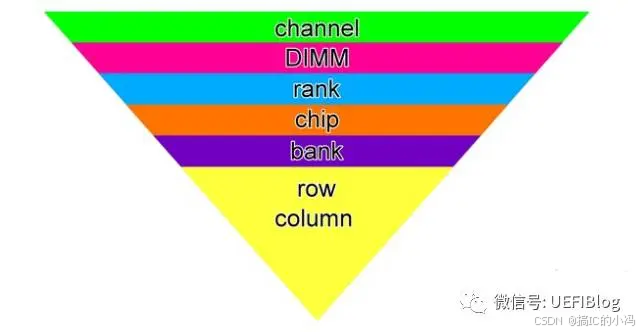

2.7.1 DIMM的层次结构

从内存控制器到内存颗粒内部逻辑,笼统来讲

channel→DIMM→rank→chip→bank(内存颗粒)→row(page)&column→cell

DDR5中有sub channel和bank group(BG)

每个DDR内存颗粒(chip)被分成多个Bank Group

每个Bank Group又分为多个Bank(共享Sense Amp,Sense Amp写回行的过程叫做precharge)

每个Bank有多个行和列(行和列时分复用,多的线用来表示读写状态/刷新状态等复用功能)

行和列的交差点就是一个cell?

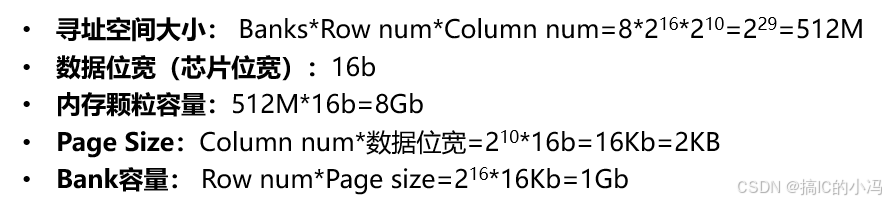

- 寻址空间大小:内存颗粒可以寻找的地址数量

- 数据位宽(芯片位宽):I/O宽度,

但是DDR5 DRAM内部存储单元(cell)容量是芯片位宽的16倍,

所以,每个基本存储单元cell容量为16*16bit=32B,即选定一行后,指定列,每个这样的基本存储单元,写命令时,向其中写入32B,读命令时,向外读出32B;

-

内存颗粒容量:寻址空间大小*数据位宽

-

Page Size:每一行的容量(列的数量)*数据位宽

DDR Page Size实际上是每次激活DDR时,输出到row buffer中的数据大小,具体的计算方式是2^column_width * chip_width / 8 Byte.

如果DDR的column address 10 bit, 那么chip_width是x4的 page size对应512B,chip_width是8的 page size对应1KB。

-

bank容量:每个bank的行数*Page Size

2.7.2 DDR5 SDRAM寻址计算

以8Gb中512Mb x16为例

2.7.3 prefetch 与 BL 和 DDR5每次操作将交付字节数的关系

- DDR5提供2个独立的32bit数据通道,prefetch为16,默认BL为16(这些为协议定义的内容)

- BL:Burst Lengths突发长度,是指在同一行中相邻的存储单元连续进行数据传输的方式,连续传输所涉及到存储单元(列)的数量就是突发长度(SDRAM),在DDR SDRAM中指连续传输的周期数。

- 对于DDR5,BL=16,通道通路32bit,则每次操作,产生的数据量为16*32bit=64B,即意味着每次操作,DDR5的单个channel一次交付64B数据,一个DDR5双channel一次就交付2个64B数据。

为什么这么设计?

个人理解:和cacheline有关。因为DDR和CPU中间是Cache。当从内存中取单元到cache中时,会一次取一个cacheline大小的内存区域到cache中,然后存进相应的cacheline中。cacheline是64字节,所以是和cacheline的大小有关系。

6129

6129

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?